шения достоверности контроля дополнительно введены второй 2 кодопреобразователь, третий счетчик 5, второй регистр 7, второй блок 10 сравнения, мультиплексор

11, одновибратор 13, шестой 22 и седьмой 23 элементы И, первый 24 и второй 25 элементы задержки. 2 ил. 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании самоконтролирующихся микропроцессорных систем. Целью изобретения является повышение достоверности контроля функционирования микропроцессорной системы за счет обеспечения контроля числа циклов и по- следовательност,и циклов любой выполняемой команды, принадлежащей алфавиту микропроцессоров (INTEL, 8Q80, К580, ИКЗО). Устройство содержит кодопреобразователь 1, первый 3 и второй 4 счётчики, первый регистр 6, сумматор 8, первый блок 9 сравнения, триггер 12, первый 14, второй 15 и третий 16 элементы ИЛИ, первый 17, второй 18, третий 19, четвертый 20 и пятый 21 элементы И. В устройство с целью повы« Ј VI СО & СА Ш1

Изобретение относится к цифровой вычислительной технике и может быть исполь- зовано при проектировании самоконтролирующихся микропроцессорных систем (МПС).

Цель изобретения - повышение достоверности контроля функционирования микропроцессорной системы путем обеспечения контроля числа циклов и последовательности циклов любой выполняемой команды, принадлежащей алфавиту микропроцессоров указанных типов.

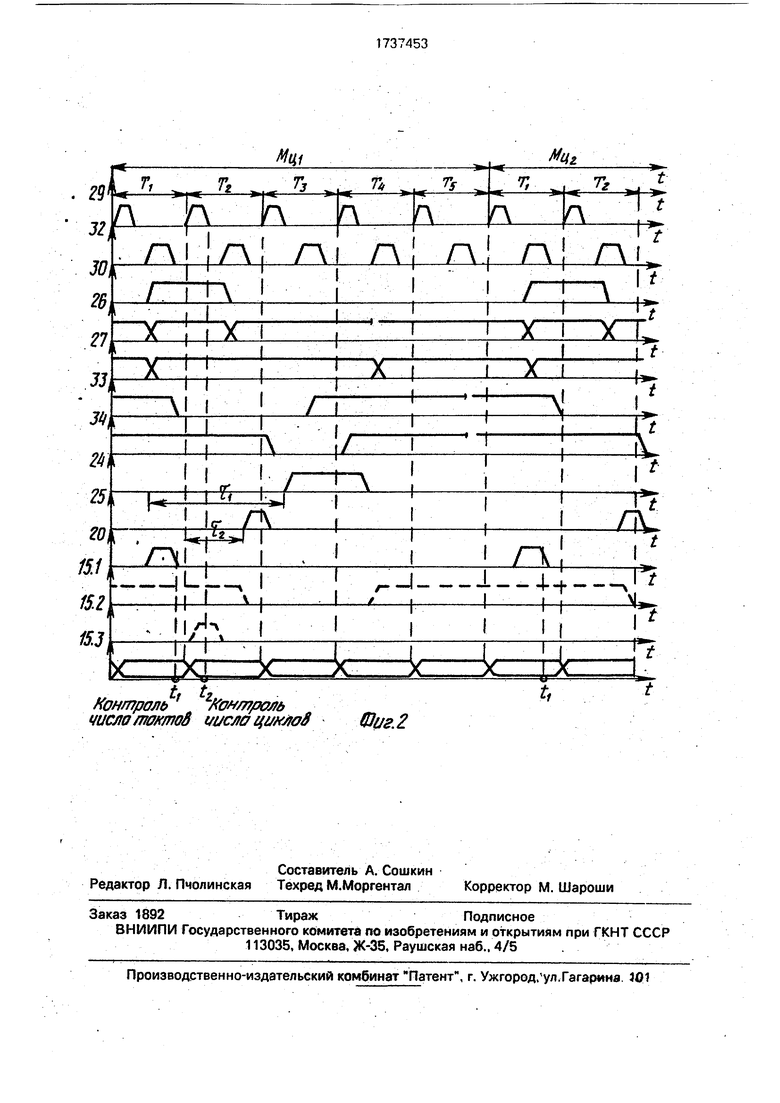

На фиг, 1 приведена функциональная схема устройства; на фиг. 2 - приведены временные диаграммы, поясняющие работу устройства.

Устройство содержит первый 1 и второй 2 преобразователи, первый 3, второй 4 и третий 5 счетчики, первый 6 и второй 7 регистры, сумматор 8, первый 9 и второй 10 блоки сравнения, мультиплексор 11, триггер 12, одновибратор 13, первый 14, второй 15 и третий 16 элемзнты ИЛИ, первый 17, второй 18, третий 19, четвертый 20, пятый 21, шестой 22 и седьмой 23 элементы И, первый 24 и второй 25 элементы задержки, группу информационных входов 26 устройства для подключения к шине данных микропроцессорной системы, группу информационных входов 27 устройства для подключения к шине адреса микропроцессорной системы, группу управляющих входов 28 устройства, являющуюся шиной управления микропроцессорной системы, тактовый вход 29 устройства для подключения к первому тактовому выходу (Ф1) микропроцессорной системы, тактовый вход 30 устройства для подключения к второму тактовому выходу (SYNC) микропроцессорной системы, информационный вход 31 устройства для подключения к шестому выходу шины данных микропроцессорной системы, тактовый вход 32 для подключения к третьему тактовому выходу (Ф2) микропроцессорной системы, вход 33 мультиплексора 11, являющийся входом сигнала МЕМР группы входов 28 устройства, вход 34 мультиплексора 11, являющийся входом сигнала MEMW группы входов 28 устройства, вход 35 мультиплексора 11, являющийся входом сигнала 1/OR группы входов 28 устройства,

вход 36 мультиплексора 11, являющийся входом сигнала 1 /OW группы входов 28 устройства, выход 37 устройства, являющийся выходом сигнала сбоя (отказа) микропроцессорной системы.

Позицией 15.1 обозначен сигнал на первом выходе элемента ИЛИ 15; позицией 15.2 - сигнал на втором входе элемента ИЛИ 15; 15.3 - сигнал на третьем входе элемента

ИЛИ 15.

Кодопреобразователь 1 предназначен для определения по коду слова состояния процессора соответствующего ему числа тактов в цикле команды и по коду команды числа циклов в команде, кодопреобразователь 2 -для формирования по коду команды и номера текущего цикла кода управляющих сигналов на мультиплексор 11 для идентификации типа цикла, сигнала разрешения

сравнения априорного и текущего адресов в текущем цикле, кода числа невыполненных циклов текущей команды, сигнала коррекции в счетчике 4 кода числа тактов первого цикла группы команд. Счетчик 3

считает числа реализованных в команде циклов, счетчик 4 - числа реализованных в цикле тактов, счетчик 5 определяет номер текущего цикла выполняемой команды. Регистр б фиксирует код команды. Сумматор 8

вычисляет априорный адрес в текущем цикле выполняемой команды по коду адреса команды и коду приращения. Блок 9 сравнения сравнивает код адреса в текущем цикле команды с априорно вычисленным, блок 10

сравнения формирует единичный сигнал об изменении числа циклов в текущей команде в первом такте по сигналу Ф1 в цикле выборки кода команды. Мультиплексор 11 коммутирует один из сигналов (MEMR, MEMW,

1/OR, 1/OW) в соответствии с кодом на управляющих входах на первый счетный вход счетчика 3 реализованных циклов. Триггер 12 формирует сигнал сбоя (отказа) объекта контроля, одновибратор 13 - сигнал сбоя

(отказа) на адресной шине микропроцессора в текущей команде по переднему фронту сигнала несравнения с блока 9 сравнения. Элемент ИЛИ 14 предназначен для формирования управляющего сигнала об измененми числа тактов в цикле команды на элемент И 22, элемент ИЛИ 15 - для обьединения сигналов о сбое (отказе) при выполнении текущей команды на информационный вход триггера 12, элемент ИЛИ 16-для объединения управляющих сигналов с вы- ходов элементов И 19 и 20 на синхровход триггера 12, Элемент И 17 формирует управляющие сигналы на синхровход счетчика А и элемента И 19, элемент И 18 - управляющий сигнал на второй счетный вход счетчика 4, элемент И 19 - управляющий сигнал на регистры б и 7, счетчики 3 и 5, синхровход триггера 12 через элемент ИЛИ 16 и разрешающий вход блока 10 сравнения, а также сигнал запрета на инверсный вход элемента И 22, элемент И 20 формирует сигнал фиксации результата контроля в триггере 12 в первом такте по заднему фронту сигнала Ф2 каждого цикла команды, элемент И 21 - управляющий сигнал на сравнение адресов в блоке 9 сравнения с учетом переходных процессов на элементах устройства, элемент И 22 - сигнал об изменении числа тактов в цикле на третий вход элемента ИЛИ 15, элемент И 23 - сигнал коррекции кода числа тактов в счетчике 4 в первом цикле команды.

Элемент 24 задержки предназначен для задержки сигнала SYNC, поступающего на первый вход элемента И 23, второй вход элемента И 21 и разрешающий вход мультиплексора 11 на время 1,75 такта машинного цикла, элемент 25 задержки - для задержки управляющего сигнала на синхровходы регистров 6 и 7, счетчика 3 и установочный вход счетчика 5 на время 0,75 такта машинного цикла команды.

Предлагаемое устройство при проверке правильности функционирования микропроцессорной системы, построенной на ба- зе микропроцессоров типа К580 ИК31, INTEL 8080 или других аналогичных, работает следующим образом.

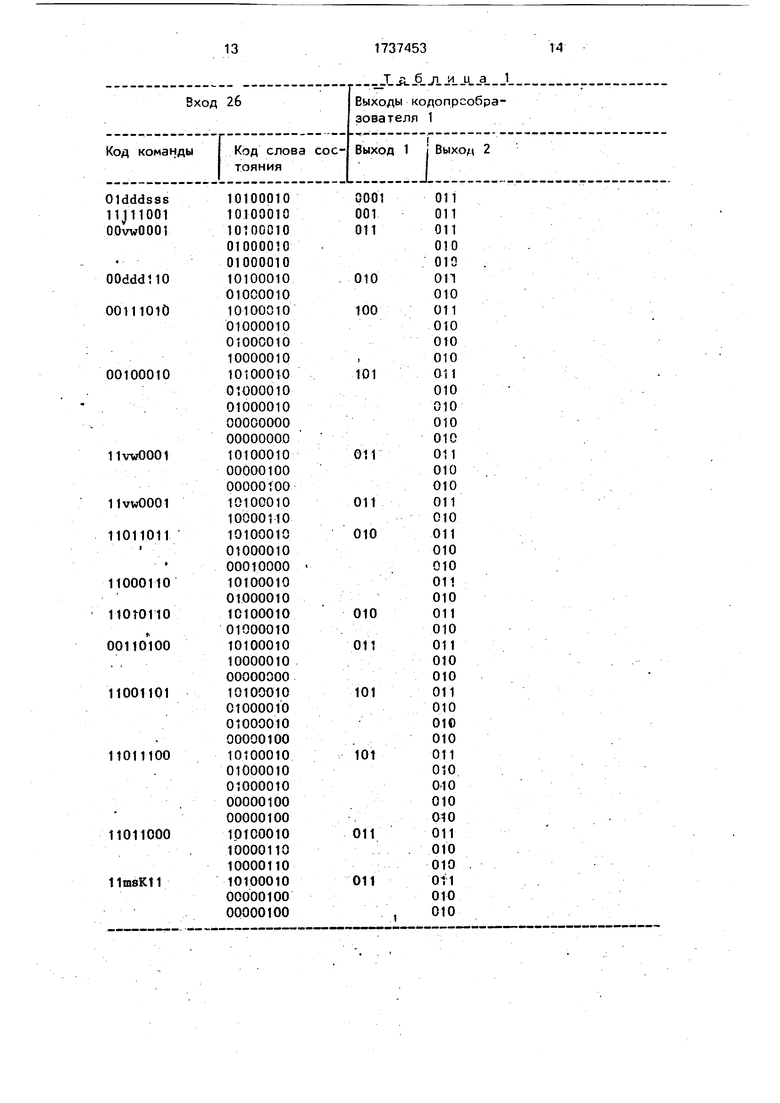

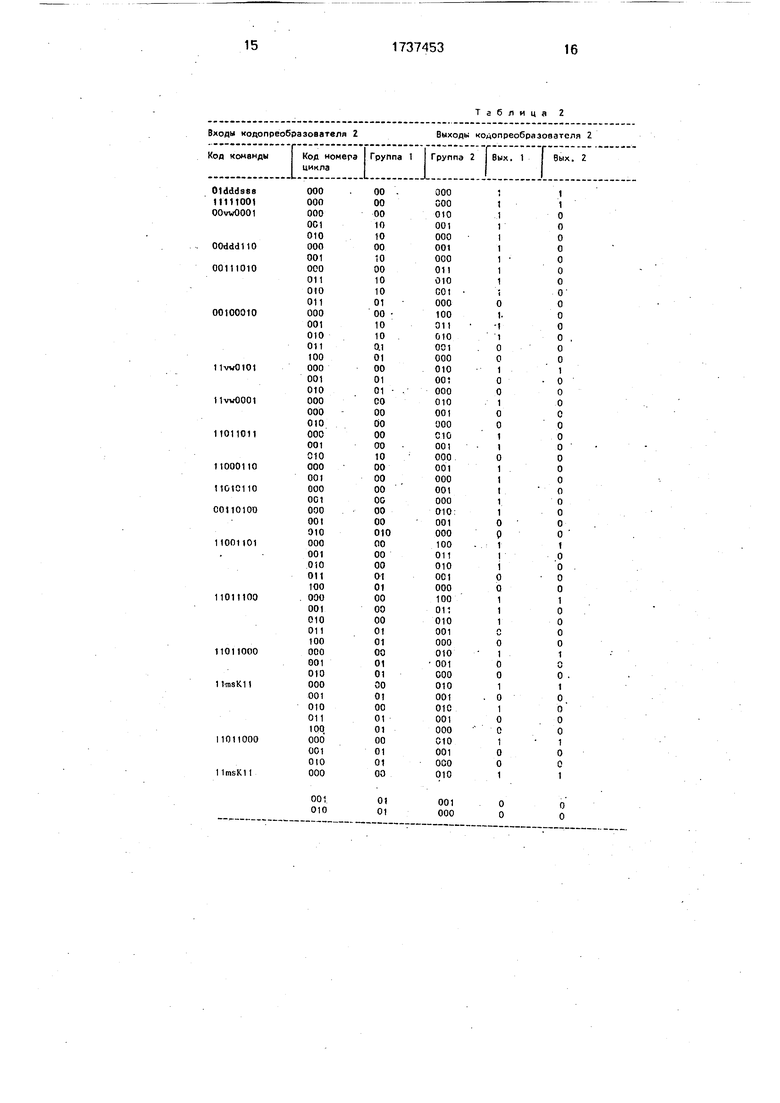

Кодопреобразователи 1 и 2 являются комбинационными схемами, их структура и работа определяются таблицами истинности. Примеры таблиц истинности кодопреобразователей 1 и 2 для различных типов команд приведены соответственно в табл. 1 и 2-.

В предлагаемом устройстве контроль правильности функционирования микропроцессорной системы осуществляется следующим образом.

Устройство начинает функционировать после перехода микропроцессора к выполнению первой команды программы. В исходном состоянии все элементы памяти находятся в нулевом состоянии (входы установки в О не показаны).

В первом такте каждого цикла текущей команды на шине адреса микропроцессора выставляется код адреса, по которому происходит обращение в данном цикле к внешнему устройству, а на шине данных микропроцессора (группа информационных входов 26 устройства) - появляется код слова состояния процессора. По коду слова состояния процессора в кодопреобразователе 1 априорно определяется число тактов в текущем цикле. Код числа тактов в цикле, уменьшенный на единицу, с второй группы выходов кодопреобразователя 1 подается на группу информационных входов счетчика 4 и фиксируется в нем по заднему фронту сигнала F1 - с выхода элемента И 17. Первый цикл каждой команды соответствует выборке кода команды из памяти. При этом в коде слова состояния, в шестом разряде устанавливается единица, соответствующая сигналу М1 - идентифицирующему цикл выборки кода команды. Сигнал М1 поступает на вход 31 устройства, являющийся вторым входом элемента И 19, и разрешает прохождение через последний сигнала F1 SYNCV O1 с выхода элемента И 17. Единичный сигнал F2 с выхода элемента И 19 подается на инверсный вход элемента И 22, запрещая формирование единичного сигнала на его выходе, сигнал F2 подается также на управляющий вход блока 10 сравнения, разрешая выдачу результата сравнения кодов реализованного и априорного чисел циклов на информационный вход триггера 12 через элемент ИЛИ 15. Через элемент ИЛИ 16 сигнал F2 подается на синхровход триггера 12. Так как начальное состояние всех элементов памяти устройства - нулевое, результат сравнения кодов в блоке 10 сравнения - нулевой, следовательно, в триггере 12 подтверждается нуль, свидетельствующий об отсутствии сбоя. Кроме го- го, сигнал F2 с выхода элемента И 19 задерживается в элементе задержки 25 на время 0,75 такта машинного цикла, т.е. до выставления из памяти на шину данных кода команды в конце второго такта первого цикла плюс время переходных процессов в кодопреобразователе 1. По заднему фронту задержанного сигнала F2 в регистре 6 фиксируется код адреса выборки кода команды с группы входов 27, в регистре 7 - код команды с группы информационных входов 26 устройства, в счетчике 3 - код числа циклов в выполняемой команде, априорно сформированный на первой группе выходов кодопреобразователя 1 из кода команды. Этим же сигналом F2 счетчик 5 устанавливается в нулевое состояние. В третьем такте

цикла элементом И 18 формируется сигнал F3 - SYNCSOL По переднему фронту этого сигнала на втором счетном входе счетчика 4 код числа тактов в счетчике 4 уменьшается на единицу. В каждом последующем такте код в счетчике 4 по положительному перепаду уменьшается на единицу. В третьем такте цикла на выходе задержки 24 формируется задержанный сигнал SYNC. Сигнал с выхода элемента 24 задержки подается на улрав- ляющий вход мультиплексора 11, а на группу управляющих входов мультиплексора 11 в этот момент поступает код на выбор для коммутации входа 33 сигнала MEMR. В третьем такте сигнал MEMR с входа 33 группы управляющих входов 28 подается на счетный вход счетчика 3. По положительному перепаду этого сигнала код в счетчике 3 уменьшается на единицу. В первом цикле команды на выходах счетчика 5 формируется нулевой код приращения к адресу на вторую группу входов сумматора 8, поэтому по сигналу не управляющем входе блока 9 сравнения в третьем такте цикла результат сравнения является нулевым, одновибратор 13 остается в неактивизированном состоянии. Таким образом, в следующем цикле подтверждается работа МПС без слоев на шине адреса. Во втором такте первого цикла команды в счетчике 4 фиксируется код, равный трем. Для команд, первый цикл которых выполняется за пять тактов, в четвертом такте первого цикла по отрицательному перепаду задержанного в элементе задержки 24 сигналу SYNC и единичному сигналу на втором выходе кодопреобразователя 2 в элементе И 23 формируется сигнал коррекции кода числа тактов. По отрицательному перепаду сигнала коррекции на первом счетном входе счетчика 4 код числа тактов тактов увеличивается на единицу.

Если текущая команда выполняется за один цикл, то по окончании его начинается выполнение первого цикла следующей команды. По положительному переходу сигнала Ф1 в первом такте первого цикла следующей команды код в счетчике 4 уменьшается в очередной раз единицу и в счетчике 4 должен установиться нулевой код. В этом случае на выходе элемента ИЛИ 14 формируется нулевой сигнал, который поступает на первый вход элемента И 22. На инверсном входе элемента И 22 отсутствует сигнал запрета, следовательно, нулевой сигнал с выхода элемента ИЛИ 14 через элемент И 22 и элемент ИЛИ 15 подается на информационный вход триггера 12. По отрицательному перепаду сигнала Ф2 в первом такте нулевой сигнал на информационном

входе триггера 12 фиксируется и подтверждает отсутствие изменения числа тактов в цикле предыдущей команды. После выполнения предыдущей команды в счетчике 5

нулевой код не изменяет, по нему на третьей группе выходов кодопреобразователя формируется нулевой код. В счетчике 3 после вычитания единицы в третьем такте остается нулевой код. Во втором такте первого

0 цикла следующей команды по сигналу Ф1 на управляющий вход блока 10 сравнения нулевые коды, поступающие с кодопреобразователя 2 и счетчика 3, сравниваются. Нулевой результат сравнения поступает

5 через элемент ИЛИ 15 на информационный вход триггера 12, по отрицательному паду сигнала Ф1 фиксируется в нем, подтверждая отсутствие изменения числа циклов и их последовательности в предыду0 щей команде.

Если текущая команда выполняется более чем за один цикл, то контроль числа циклов и их последовательности осуществляется в первом цикле следующей команды.

5 Кроме проверки числа тактов в каждом цикле, числа циклов и их последовательности, в выполняемой команде контролируется изменение адреса команды одно-, двух- и трехбайтовой структуры. Так, во втором цик0 ле трехбайтовой команды на выходах счетчика 5 формируется код приращения на вторую группу входов сумматора 8, равный единице, а в третьем цикле-двум. Полученный на выходе суммарный априорный адрес

5 соответствует текущему адресу на .группе входов 27 устройства.

Рассмотрим работу устройства при сбое, в результате которого изменяется число, тактов в цикле либо число циклов, либо

0 последовательность циклов в команде.

Допустим, что произошел сбой в МПС и число тактов в текущем цикле изменилось. При этом в первом такте следующего цикла в момент формирования сигнала Ф2 на вхо5 де 32 устройства в счетчике 4 код не равен нулю. На выходе элемента ИЛИ 14, а следовательно, и на выходе элементов И 22 ИЛИ 15 присутствует сигнал единицы. По отрицательному перепаду сигнала Ф2 в триггере

0 12 этот единичный сигнал фиксируется и на выходе 37 устройства формируется сигнал сбоя микропроцессорной системы.

Допустим, что произошел сбой в МПС и изменилась последовательность циклов в

5 текущей команде. При этом мультиплексор 11 в каждом цикле текущей команды настра- ивается на коммутацию определенного входа. Сигнал на счетный вход счетчика 3 может поступить только с выбранного входа в мультиплексоре 11. Если сигнал в этот момент находится на невыбранном входе, то он не поступает на счетчик 3 и код в нем не уменьшается на единицу в текущем цикле команды. По завершении выполнения команды в счетчике 3 остается код, не равный нулю, и в первом такте первого цикла следующей команды по сигналу F2 в блоке 10 сравнения формируется единичный сигнал, который фиксируется в триггере 12 по отрицательному перепаду сигнала F2. Таким образом, в триггере 12 сформируется сигнал сбоя МПС на выход 37 устройства.

Предположим, что произошел сбой в МПС и, как результат, изменилось число циклов в текущей команде. При этом число вычитаемых единиц из кода в счетчике 3 равно числу циклов трансформированной команды и «е соответствует коду в счетчике 3 и как результат, в первом такте первого цикла следующей команды в блоке 10 сравнения формируется единичный сигнал на информационный вход триггера 12 через элемент ИЛИ 15. По отрицательному перепаду сигнала F2 в триггере 12 зафиксируется единица и формируется сигнал сбоя МПС на выход 37 устройства.

Кроме того, любое несравнение априорно сформированного и текущего адресов в блоке 9 сравнения формирует единичный сигнал на вход одновибратора 13. По положительному перепаду сигнала несравнения на выходе одновибратора 13 формируется единичный сигнал на информационный вход триггера 12 через элемент ИЛИ 15 до момента фиксации в первом такте следующего цикла. В триггере 12 по отрицательному перепаду сигнала Ф2 в первом такте следующего цикла фиксируется единица и формируется сигнал сбоя МПС на выход 37 устройства.

При выполнении команд условного перехода со стековой адресацией контроль числа циклов в устройстве осуществляется либо после третьего, либо после пятого циклов команд. Если условный переход не выполняется по указателю стека, то контроль числа циклов осуществляется после третьего цикла, в противном случае- после пятого. В счетчике 3 при выборе кода команды фиксируется число пять. После выполнения трех циклов счетчике 3 находится число два, т.е. на вторую группу входов блока 10 сравнения поступает код, не равный нулю. Аналогичный код, равный двум, формируется в третьем цикле команды и на первой группе входов блока 10 сравнения с третьей группы выходов кодопреобразователя 2. Если условный переход по указателю стека не выполняется, то команда завершается за три цикла. Следующий цикл - цикл выборки

следующей команды. По сигналу F2 с выхода элемента И 19 на выходе блока 10 сравнения формируется нулевой сигнал сравнения, который фиксируется в триггере 5 12 по отрицательному спаду сигнала F2. При этом на выходе 37 устройства подтверждается состояние отсутствия сигнала сбоя МПС. При выполнении команды условного перехода за пять циклов контроль числа вы10 полненных циклов осуществляется в первом такте первого цикла следующей команды.

Формула изобретения Устройство для контроля микропроцес5 сорной системы, содержащее кодопреобразователь, первый и второй счетчики, регистр, сумматор, блок сравнения, триггер, первый, второй и третий элементы ИЛИ и первый-пятый элементы И. причем группа

0 информационных входов устройства для подключения к шине данных микропроцессорной системы является группой входов кодопреобразователя, первая и вторая группы выходов которого соединены с груп5 пами информационных входов соответственно первого и второго счетчиков, группа информационных выходов второго счетчика соединена с входами первого элемента ИЛИ, группа информационных входов уст0 ройства для подключения к адресной шине микропроцессорной системы является группой информационных входов регистра и первой группой информационных входов блока сравнения, группа выходов регистра

5 соединена с первой группой входов сумматора, группа выходов которого соединена с второй группой входов блока сравнения, тактовый вход устройства для подключения к первому тактовому выходу микропроцес0 сорной системы соединен с первым входом первого элемента И. тактовый вход устройства для подключения к второму выходу микропроцессорной системы - с вторым входом первого элемента И, выход которого

5 соединен с синхровходом второго счетчика, выход триггера является выходом неисправности устройства, отличающееся тем, что, с целью повышения достоверности контроля, в него введены второй ко0 допреобразователь, третий счетчик, второй регистр, второй блок сравнения, мультиплексор, одновибратор, шестой и седьмой элементы И, а также первый и второй элементы задержки, причем группа ин5 формационных входов устройства для подключения к шине данных микропроцессорной системы соединена с группой информационных входов второго регистра, группа выходов которого соединена с второй группой входов второго кодопреобраэователя, группа аыходоа первого счетчика - с второй группой входов второго блока сравнения, выход которого соединен с вторым входом второго элемента ИЛИ, управляющие входы устройства для подключения к шине управления микропроцессорной системы соединены с информационными входами мультиплексора, выход которого соединен со счетным входом первого счетчика, первая группа выхо- дов второго кодопреобразователя соединена с группой управляющих входов мультиплексора, вторая группа выходов второго кодопреобразователя - с первой группой входов второго блока сравнения, первый выход второго кодопреобразователя - с первым входом пятого элемента И, выход которого соединен с управляющим входом первого блока сравнения, выход первого блока сравнения соединен с входом одновибратора, выход одновибратора- с первым входом второго элемента ИЛИ, выход которого соединен с информационным входом триггера, второй выход второго кодопреобразователя соединен с вторым входом седьмого элемента И, выход которого соединен с первым входом второго счет- чика, тактовый вход устройства для подключения к первому тактовому выходу, микропроцессорной системы соединен с прямым входом второго элемента И, выход которого соединен с вторым счетным входом второго счетчика, тактовый вход устройства для подключения к второму тактовому

входу микропроцессорной системы соединен с инверсным входом второго элемента И, счетным входом третьего счетчика, первым входом четвертого элемента И и через

первый элемент задержки с первым входом седьмого элемента И. управляющим входом мультиплексора и вторым входом пятого элемента И, выход четвертого элемента И соединен с вторым входом третьего элемента ИЛИ, выход которого соединен синхров- ходом .триггера, информационный вход устройства для подключения к одному из выходов шины данных микропроцессорной системы соединен со вторым входом третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, управляющим входом второго блока сравнения, инверсным входом шестого элемента И и через второй элемент задержки с синхровходами первого и второго регистров, первого счетчика и установочным входом третьего

счетчика, тактовый вход устройства для

подключения к третьему тактовому выходу

микропроцессорной системы соединен с

вторым входом четвертого элемента И, выход первого элемента И - с первым входом третьего элемента И, группа информационных выходов третьего счетчика соединена с первой группой входов второго кодопреобраэователя и второй группой входов сумматора, выход первого элемента ИЛИ соединен с первым входом шестого элемента И, выход которого соединен с третьим входом второго элемента ИЛИ.

J 3. б л и А а J

Таблица 2

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СПОСОБ РАЗРАБОТКИ НЕФТЯНОЙ ЗАЛЕЖИ | 1995 |

|

RU2065939C1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коффрон Дж | |||

| Технические средства микропроцессорных систем | |||

| - М.: Мир, 1983, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

| Самофалов К.Г, и др | |||

| Микропроцессоры | |||

| - Киев: Техника, 1986, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

Авторы

Даты

1992-05-30—Публикация

1990-05-21—Подача