Изобретение относится к вычислительной технике и может быть использрвано для построения интегральных схем статических оперативных запом1Йнающих устрой тв с произвольной выборкой .на МДП-транзисторах.

Известен способ хранения информации на МДП-транзисторах, реализованный в запоминающем элементе, содержащем два МДП-транзистора и управляемый напряжением конденсатор l .

Недостатком этого способа является низкая надежность работы, связанная с жесткими требованиями к длительности фронтов управляющих сигналов, подключающих нагрузку к информационному выводу запоминающего элемента, и сложность получения большого отношения емкости управляемого напряжением конденсатора при хранении в запоминающем элементе единичного информационного заряда к его емкости при хранении нулевого информационного заряда.

Известен способ хранения информации на МДП-транзисторе , состоящий в подаче напряжения на сток МДПтранзистора и импульса записи и тактового импульса, устанавливающих на

затворе МДП-транзистора информационный заряд, в сохранении этого заряда в промежутках между тактовыми импульсами на изолированном затворе МДПтранзистора, и в периодической подаче последовательности возбуждающего и тактового импульсов, обеспечивающей при регенерации информации восстановление единичного информационного

10 заряда на затворе МДП-транзистора путем накопления заряда на истоке МДП-транзистора за счет протекания через него тока с шины питания при подаче возбуждающего импульса, отпи15рающего МДП-транзистор только при единичном информационном заряде на его затворе, и последующей передачи накопленного заряда с истока на затвор МДП-транзистора при подаче тактового

20 импульса Гз.

Недостатком этого способа является необходимость подачи при регенерации возбуждающего импульса и обеспечения

25 во время этого импульса надежного запирания МДП-транзистора при нулевом информационном заряде, что затрудняется необходимостью хорошего отпирания МДП-тразистора этим импульсом при

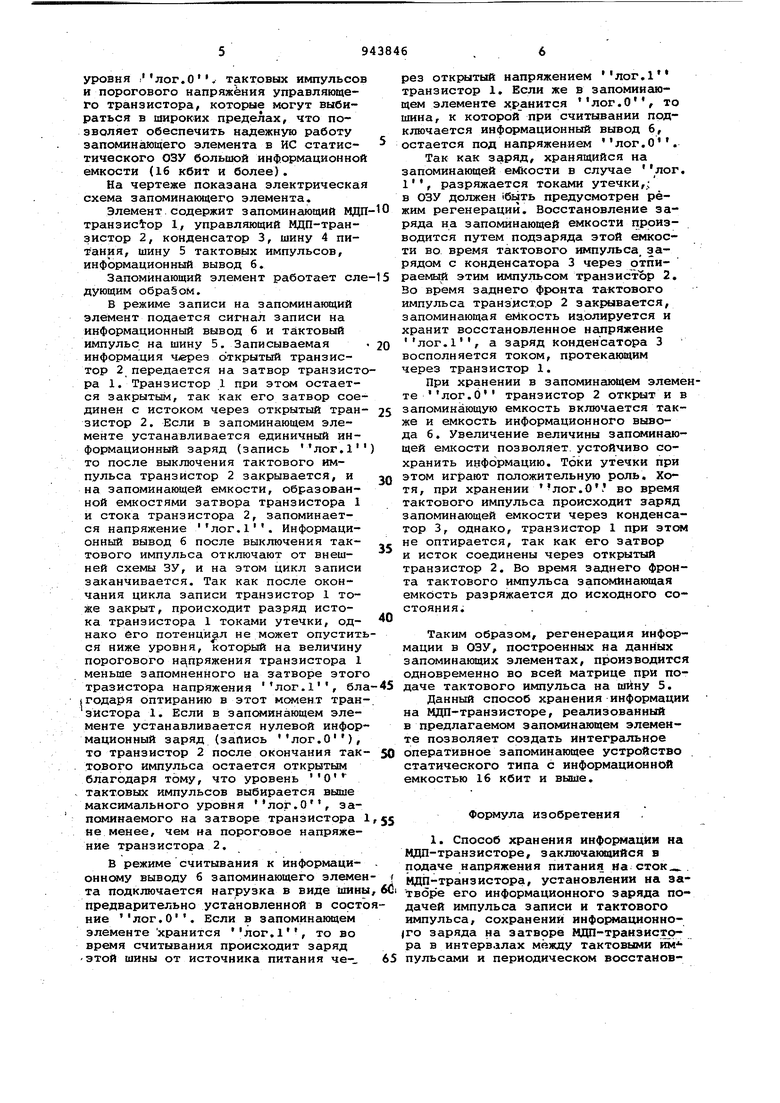

30 единичном информационном заряду. : Это усложняет запоминающий элемент снижает надежность его работы.. Известен запоминающий элемент на МДП-тразисторах, использующий указа ный способ хранения информации, содержащий запоминающий транзистор, сток которого соединен с шиной пита ния, исток с информационным выводом и с истоком управляющего транзистора, сток которого соединен с затвором запоминающего тразистора и с управляющим электродом управляемого напряжения конденсатора, другой эле 1ктрод которого подключен к шине возбуждающих импульсов, а затвор уп равляющего транзистора подключен к тактовой шине 2.. Для надежной работы данного запоминающего элемента емкость управляемого напряжением конденсатора пр хранении нулевого информационного з ряда должна быть достаточно малой п сравнению с емкостью затвора запоми нающего транзистора, чтобы наводимое на нем при подаче возбуждающего импульса напряжение не превышало порогового, С другой стороны, емкость управляемого конденсатора при хранении единичного информационного заряда должна быть достаточно большой по сравнению с той же емкостью затвора, чтобы получить на нем достаточно большое напряжение для эффективной регенераци Кроме того, для получения заряда в истоке запоминающего транзистора, 1 требуемого для эффективной регенера ции, необходимо обеспечить достаточ но большую емкость истока,. что достигается введением специального конденсатора или введением элементо в интегральном исполнении внполняющ роль конденсатора, например, увеличением области диффузии истока. Необходимость в источнике возбуждающих импульсов и сложность выполнения указанных требований к емкости управляемого напряжением конденсатора при хранении нулевого и единичного информационного зарядов, а также к емкости истока, усложняют запоминающий элемент и снижают его надежность. Целью изобретения является повышение надежности хранения информаци в запоминающем элементе за счет упрощения процесса восстановления информациойного заряда. Поставленная цель достигается те что согласно способу хранения информации на МДП-транзисторе, при ко тором подают напряжение питания на сток МДП-транзистора, устанавливают на затворе МДП-транзистора информационный заряд подачей импульса записи и тактового импульса, сохраняют информационный заряд на затвор МДП-транзистора в интервалах между тактовыми импульсами и периодически восстанавливают информационный заряд, единичный информационный заряд подачей тактового импульса передают с истока МДП-транзистора на его затвор и восстанавливают переданный единичный Информационный заряд на истоке МДП-транзистора передачей напряжения питания через открываемый выключением тактового импульса МДП-транзистор, а нулевой информационный заряд восстанавливают выравнивая потенциал затвора и истока МДП-транзистора. В предла гаемом способе надежное запирание МДП-транзистора при регенерации в случае хранения нулевого информационного заряда обеспечивается за счет поддержания потенциала затвора МДП-транзистора равным потенциалу его истока и для восстановления единичного информационного заряда на истоке МДП-транзистора не требуется подача возбуждающего импульса. Все это упрощает процесс регенерации информации в запоминающем элементе и повышает надежность |его работы. Такой способ хранения информации может быть осуществлен запоминающим элементом на МДП-транзисторах, содержащем запоминающий МДП-тразистор, сток которого соединен с шиной питания, исток - с информационным выводом и с истоком управляющего МДПтранзистора, сток которого соединен с затвором запоминающего МДП-транзистора, введением конденсатора, первый электрод которого подключен к истоку запоминающего транзистора, а второй электрод соединен с затвором управляющего транзистора и с тактовой шиной. Кроме того, с целью упрощения управления запоминающим элементом, управляющий транзистор запс 1Инающего элемента может быть выполнен со встроенным каналом, В предлагаемом запоминакнцем элементе конденсатор подклочен не к затвору запоминающего МДП-транзистора, а к его истоку. Это, во-первых, устраняет опасность отпирания этого транзистора во время регенерации при нулевом информационном заряде на его затворе и позволяет заменить управляемый конденсатор постоянным, и, во-вторых, устраняет необходимость в специальном конденсаторе или элементах, выполняющих в интегральном исполнении его роль, в цепи истока. Все это позволяет упростить запоминающий элемент и повысить его надежность. Устойчивость работы запоминающего элемента обеспечивается выбором уровня .О , тактовых импульсо и порогового напряжения управляющего транзистора, которые могут выбираться в широких пределах, что позволяет обеспечить надежную работу запоминающего элемента в ИС статистического ОЗУ большой информационно емкости (16 кбит и более). На чертеже показана электрическа схема запоминающего элемента. Элемент содержит запоминающий МД транзистор 1, управляющий МДП-транзистор 2, конденсатор 3, шину 4 питания, шину 5 тактовых импульсов, информационный вывод 6. Запоминающий элемент работает сл дующим обра§оМ. В режиме записи на запоминающий элемент подается сигнал записи на информационный вывод 6 и тактовый импульс на шину 5. Записываемая информация ч«рез Открытый транзистор 2 передается на затвор транзист ра 1. Транзистор 1 при этсйч остается закрытым, так как его затвор сое динен с истоком через открытый тран зистор 2. Если в запоминающем элементе устанавливается единичный информационный заряд (запись лог.1 то после выключения тактового импульса транзистор 2 закрывается, и на запоминающей емкости, образованной емкостями затвора транзистора 1 и стока транзистора 2, запоминается напряжение лог.1. Информационный вывод 6 после выключения тактового импульса отключают от внешней схемы ЗУ, и на этом цикл записи заканчивается. Так как после окончания цикла записи транзистор 1 тоже закрыт, происходит разряд истока транзистора 1 токами утечки, однако его потенциал не может опустит ся ниже уровня, который на величину порогового на пряжения транзистора 1 меньше запомненного на затворе этог тразистора напряжения лог.1, бл (годаря оптиранию в этот момент тран зистора 1. Если в запоминающем элементе устанавливается нулевой инфор мационный заряд (запись лог.О ), то транзистор 2 после окончания так тового импульса остается открытым благодаря тому, что уровень 0 тактовых импульсов выбирается выше максимального уровня лог.О , запоминаемого на затворе транзистора не менее, чем на пороговое напряжение транзистора 2. В режиме считывания к йнформациoHHCwy выводу б запоминающего элеме та подключается нагрузка в виде шин предварительно установленной в сост ние лог.О . Если в запоминающем элементе хранится лог.1, то во время считывания происходит заряд ЭТОЙ шины от источника питания че- рез открытый напряжением лог.1 транзистор 1. Если же в запоминающая элементе хранится лог.О , то шина, к которой при считывании подключается информационный вывод 6, остается под напряжением лог.О . Так как заряд, хранящийся на запоминающей емкости в случае лог. 1, разряжается токами утечки,; в ОЗУ должен (быть предусмотрен режим регенераций. Восстановление заряда на запоминающей емкости производится путем подзаряда этой емкости во время тактового импульса, зарядом с конденсатора 3 через отпираемцй этим импульсом транзистор 2. Во время заднего фронта тактового импульса транзистор 2 закрывается, запоминающая емкость иаолируется и хранит восстановленное напряжение .1, а заряд конденсатора 3 восполняется током, протекающим через транзистор 1. При хранении в запоминающем элементе лог.О транзистор 2 открыт и в запоминающую емкость включается также и емкость информационного вывода 6. Увеличение величины запоминающей емкости позволяет, устойчиво сохранить информацию. Токи утечки при этом играют положительную роль. Хотя, при хранении лог.О во время тактового импульса происходит заряд запоминающей емкости через конденсатор 3, однако, транзистор 1 при этом не оптирается, так как его затвор и исток соединены через открытый транзистор 2. Во время заднего фронта тактового импульса запоминающая емкость разряжается до исходного состояния;Таким образом, регенерация информации в ОЗУ, построенных на данных запоминающих элементах, производится одновременно во всей матрице при подаче тактового импульса на шину 5. Данный способ хранения информации на МДП-транзисторе, реализованный в предлагаемом запоминсцощем элементе позволяет создать интегральное оперативное запоминающее устройство статического типа с информационной емкостью 16 кбит и выше. Формула изобретения 1. Способ хранения информации на МДП-транзисторе, заключакицийся в подаче напряжения питания .. МДП-транзистора, установлении на затвбре его информационного заряда подачей импульса записи и тактового импульса, сохранений информационно(го заряда на затворе МДП-транзисГрра в интервалах между тактовыми импульсс1ми и периодическом восстановлении информационного заряда, от-, личающийся тем, что,,с целью повышения надежности хранения информации за счет упрощения процесса восстановления информационного заряда, единичный инфор 1ационный . . . заряд передает с истока МДП- транзистора на его затвор подачей тактового импульса и восстанавливают переданный единичный информационный заряд на истоке МДП-транзистора передачей на- О пряжения питания чере открываемый Быклгочением тактового импульса МДПтранзистор, а нулевой информационный заряд восстанавливают, выравнивая потенциалы затвора и истока МДП-тран-5 зистора,

2. Запоминающий элемент для осуществления способа по П.1, о т л ичающийс я тем, что он содержит запоминающий МДП-транзист-ор, сток ко-20

торого соединен с шиной питания, исток - с информационным выводом и с истоком управляющего МДП-транзистора, сток которого соединен с затворо запоминающего МДП-тразистора, в запомингиощий элемент введен конденсатор, первый электрод которого подключен к истоку запоминающего МДП-тран зистора, а второй электрод соединен с затвором управляющего МДП- ран зистооа и с тактовой шиной.

3. Элемент по п.2, отличающийся тем, что управляющий МДП-транзистор выполнен со встроенаюл каналом.

Источники информации, принятые во внимание при экспертизе

1. Патент СЗПА 3744037, кл. 340/173, опублик. 1973.

2. Патент США № 3878404, кл. 307/238, опублик. 1975 (прототип

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходное устройство на мдп транзисторах | 1975 |

|

SU547970A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Ячейка памяти | 1976 |

|

SU681455A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

.,

Авторы

Даты

1982-07-15—Публикация

1977-09-16—Подача