Изобретение относится к автоматике и вычислительной технике и может быть использовано в многоканальных системах телеизмерения и телеуправления для передачи информации без предварительного фазирования.

Цель изобретения - повышение быстродействия.

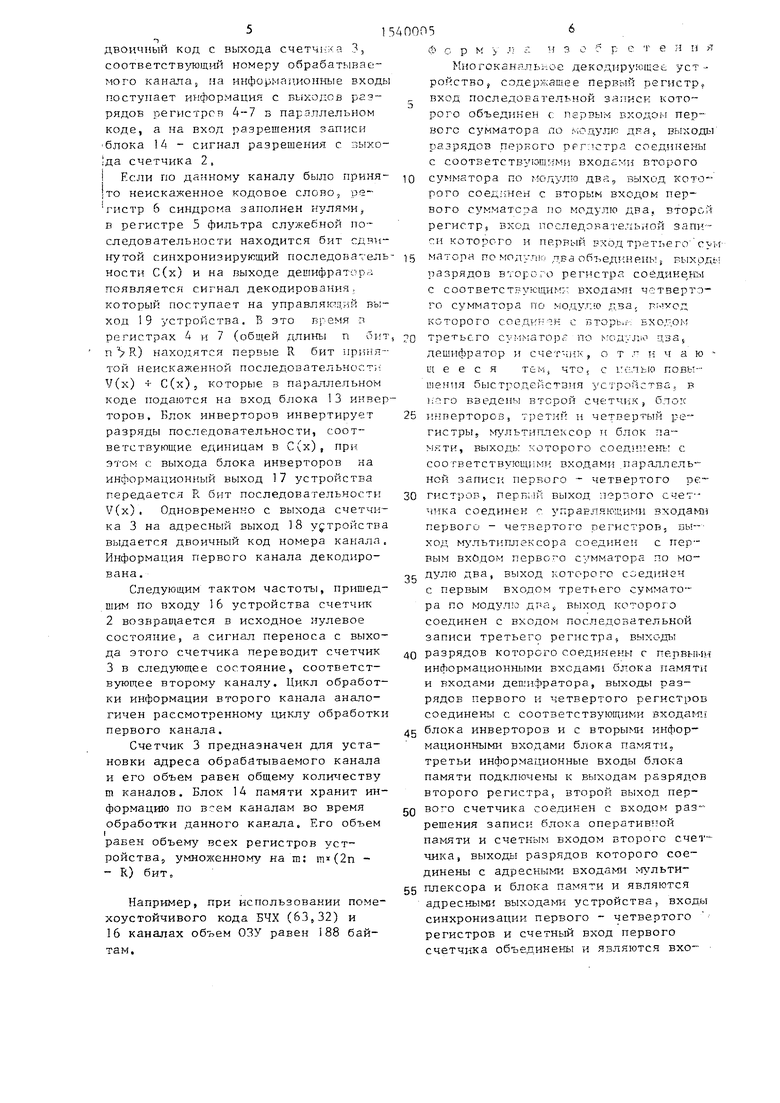

На чертеже представлена функциональная схема устройства.

Многоканальное декодирующее уст- .ройство содержит мультиплексор 1 , счетчики 2 и 3, регистры 4-7,чсумматоры 8-11 по модулю два, дешифратор 12, блок 13 инверторов и блок 14памяти, информационный вход 15, вход 16 синхронизации, информационный выход 17, адресный выход 18 и управляющий выход 19 устройства.

Многоканальное декодирующее устройство работает следующим образом,

На вход 16 синхронизации устройства непрерывно поступает последовательность синхроимпульсов, частота следования которых выбрана таким образом, чтобы за время, проходящее межцу поступлением двух последовательных разрядов информации, передаваемой по одному каналу, осуществлялся циклический опрос всех каналов с последовательностью действий, описанной ниже.

В исходном состоянии счетчики

2и 3 находятся в нулевом положении.

Двоичный код состояния счетчика

3поступает на адресные входы мультиплексора 1, который подключает первый канал информационного входа

15устройства к входу фильтра информационной последовательности, образованного регистром 4 и сумматорами 8 и 9. Одновременно сигнал нулевого счетчика 2 подается на управляющие входы регистров 4-7. Двоичный код состояния счетчика 3 поступает также на адресный вход блока 14 памяти, при этом на выходе блока 14 устанавливается информация, соответствующая первому каналу. В нулевом состоянии счетчика 2 эта информация по входам параллельной записи регистров 4-7 записывается в регистры. Счетчик

2 представляет собой двоичный счетчи с тремя состояниями. Следующим такто частоты, приходящим по входу 16, счетчик 2 переводится во второе состояние ,

10

15

20

25

м 40005 4

В этом положении счетчика 2 отсутствует сигнал управления регистров 4-7. Перечисленные регистры перестраиваются на работу в режиме последовательного сдвига информации. В этом режиме осуществляется запись очередного бита информации первого канала в регистр 4 длины R бит фильтра информационной последовательности. В фильтре информационной последовательности проводится умножение входного сигнала первого канала на проверочный полином h(x) кода, благодаря чему на выход фильтра не проходят информационные кодовые слова V(x); с другой стороны, синхронизирующая последовательность С(х) проходит на выход фипьтра, получая при этом определенный фазовый сдвиг.

Регистр 5 длины S бит с сумматорами 10 и 11 образует фильтр служебной (синхронизирующей) последовательности, умножающей поступающие „ на его вход сигналы на полином f(x), Полином f(x) является проверочным полиномом последовательности С(х). При поступлении на вход фильтра безошибочного участка кодового слова, после заполнения регистров 4 и

5правильными символами сигнал на выходе сумматора 10 исчезает, так как последовательнодть V(x) не пропускается фильтром информационной последовательности, а последователь35 ность С(х) - фильтром служебной последовательности. Помехи, отличающиеся от кодового слова, проходят, преобразуясь, через оба фильтра. Нулевые сигналы, соответствующие правильно принятому кодовому слову заполняют регистр 6 синдрома. Во втором состоянии счетчика 2 в регистр

6синдрома записывается один бит информации. При числе информационных бит в кодовом слове R, числе информационных бит в синхронизирующей последовательности S, объем регистра синдрома равен п - R - S,

i

С целью уменьшения вероятности

ложного приема объем регистра синдрома можно изменять.

После прихода следующего такта частоты по входу 16 устройства счетчик 2 переходит в третье состояние. В этом состоянии осуществляется запись информации, хранящейся в регистрах 4-7 в блок 14 памяти. При этом на адресные входы 14 поступает

30

40

45

50

двоичный код с выхода счетчика 3, соответствующий номеру обрабатываемого канала, на информационные входы поступает информация с выходов разрядов регистров 4-7 в параллельном коде, а на вход разрешения записи блока 14 - сигнал разрешения с выхода счетчика 2.

Если по данному каналу было принято неискаженное кодовое слово, регистр 6 синдрома заполнен нулями, в регистре 5 фильтра служебной последовательности находится бит сдвиФормула изобретения Многоканальное декодирующее устройство, содержащее Первый регистр, 5 вход последовательной записи которого объединен с первым входом первого сумматора по модулю два, выходы разрядов первого регистра соединены с соответствующими входами второго Ю сумматора по модулю два, выход которого соединен с вторым входом первого сумматора по модулю два, второй регистр, вход последовательной записи которого и первый вход третьего сумразрядов второго регистра соединенны с соответствующими входами четвертого сумматора по модулю два5 выход которого соединен с вторым входом

нутой синхронизирующий последователь- 15 матора по модулю два объединены, выходы ности С(х) и на выходе дешифратора появляется сигнал декодирования, который поступает на управляющий выход 19 устройства. Б это время в

регистрах 4 и 7 (общей длины п бит, 20 третьего сумматора по модулю два, n V R) находятся первые R бит принятой неискаженной последовательности V(x) + С(х), которые в параллельном коде подаются на вход блока 13 инверторов. Блок инверторов инвертирует разряды последовательности, соответствующие единицам в С(х), при этом с выхода блока инверторов на информационный выход 17 устройства передается R бит последовательности V(x). Одновременно с выхода счетчика 3 на адресный выход 18 устройства выдается двоичный код номера канала. Информация первого канала декодирована.

Следующим тактом частоты, пришед- шим по входу 16 устройства счетчик

2возвращается в исходное нулевое состояние, а сигнал переноса с выхода этого счетчика переводит счетчик

3в следующее состояние, соответствующее второму каналу. Цикл обработки информации второго канала аналогичен рассмотренному циклу обработки первого канала.

Счетчик 3 предназначен для установки адреса обрабатываемого канала и его объем равен общему количеству m каналов. Блок 14 памяти хранит информацию по всем каналам во время

обработки данного канала. Его объем i

равен объему всех регистров устройства, умноженному на т: гах(2п - - R) бит.

Например, при использовании помехоустойчивого кода БЧХ (63,32) и 16 каналах объем ОЗУ равен 188 байтам.

дешифратор и счетчик, отличающееся тем, что, с и елью повышения быстродействия устройства, в него введены второй счетчик, блок

25 инверторов, третий и четвертый регистры, мультиплексор и блок памяти, выходы которого соединены с соответствующими входами параллельной записи первого - четвертого ре30 гистров, первый выход первого счетчика соединен с управляющими входами первого - четвертого регистров, выход мультиплексора соединен с первым входом первого сумматора по мо35 ДУЛЮ два, выход которого соединен с первым входом третьего сумматора по модулю два, выход которого соединен с входом последовательной записи третьего регистра, выходы

40 разрядов которого соединены с первыми информационными входами блока памяти и входами дешифратора, выходы разрядов первого и четвертого регистров соединены с соответствующими входами

45 блока инверторов и с вторыми информационными входами блока памяти, третьи информационные входы блока памяти подключены к выходам разрядов второго регистра, второй выход пер5о вого счетчика соединен с входом разрешения записи блока оперативной памяти и счетным входом второго счетчика, выходы разрядов которого соединены с адресными входами мульти55 плексора и блока памяти и являются адресными выходами устройства, входы синхронизации первого - четвертого регистров и счетный вход первого счетчика объединены и являются вхо400056

Формула изобретения Многоканальное декодирующее устройство, содержащее Первый регистр, 5 вход последовательной записи которого объединен с первым входом первого сумматора по модулю два, выходы разрядов первого регистра соединены с соответствующими входами второго Ю сумматора по модулю два, выход которого соединен с вторым входом первого сумматора по модулю два, второй регистр, вход последовательной записи которого и первый вход третьего сумразрядов второго регистра соединенны с соответствующими входами четвертого сумматора по модулю два5 выход которого соединен с вторым входом

матора по модулю два объединены, выходы

третьего сумматора по модулю два,

дешифратор и счетчик, отличающееся тем, что, с и елью повышения быстродействия устройства, в него введены второй счетчик, блок

инверторов, третий и четвертый регистры, мультиплексор и блок памяти, выходы которого соединены с соответствующими входами параллельной записи первого - четвертого регистров, первый выход первого счетчика соединен с управляющими входами первого - четвертого регистров, выход мультиплексора соединен с первым входом первого сумматора по моДУЛЮ два, выход которого соединен с первым входом третьего сумматора по модулю два, выход которого соединен с входом последовательной записи третьего регистра, выходы

разрядов которого соединены с первыми информационными входами блока памяти и входами дешифратора, выходы разрядов первого и четвертого регистров соединены с соответствующими входами

блока инверторов и с вторыми информационными входами блока памяти, третьи информационные входы блока памяти подключены к выходам разрядов второго регистра, второй выход первого счетчика соединен с входом разрешения записи блока оперативной памяти и счетным входом второго счетчика, выходы разрядов которого соединены с адресными входами мультиплексора и блока памяти и являются адресными выходами устройства, входы синхронизации первого - четвертого регистров и счетный вход первого счетчика объединены и являются вхо715400058

дом синхронизации устройства, входы соответственно информационными в хо- мультиплексора, выходы блока инвер- дами, информационными выходами и торов и выход дешифратора являются управляющим выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1585830A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в многоканальных системах телеизмерения и телеуправления для передачи информации без предварительного фазирования. Цель изобретения - повышение быстродействия. Многоканальное декодирующее устройство содержит мультиплексор 1, счетчик 2,3, регистры 4-7, сумматоры 8-11 по модулю два, дешифратор 12, блок 13 инверторов и блок 14 памяти. 1 ил.

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU365033A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-01-30—Публикация

1987-11-16—Подача