Изобретение относится к области управления производственными процессами и может быть использовано в дискретных системах управления, например, в угольной и горнорудной промышленности (управление водоотливными и холодильными установками, шахтным рельсовым транспортом и др.)

Цель изобретения - уменьшение потребляемой мощности и повышение надежности работы устройства.

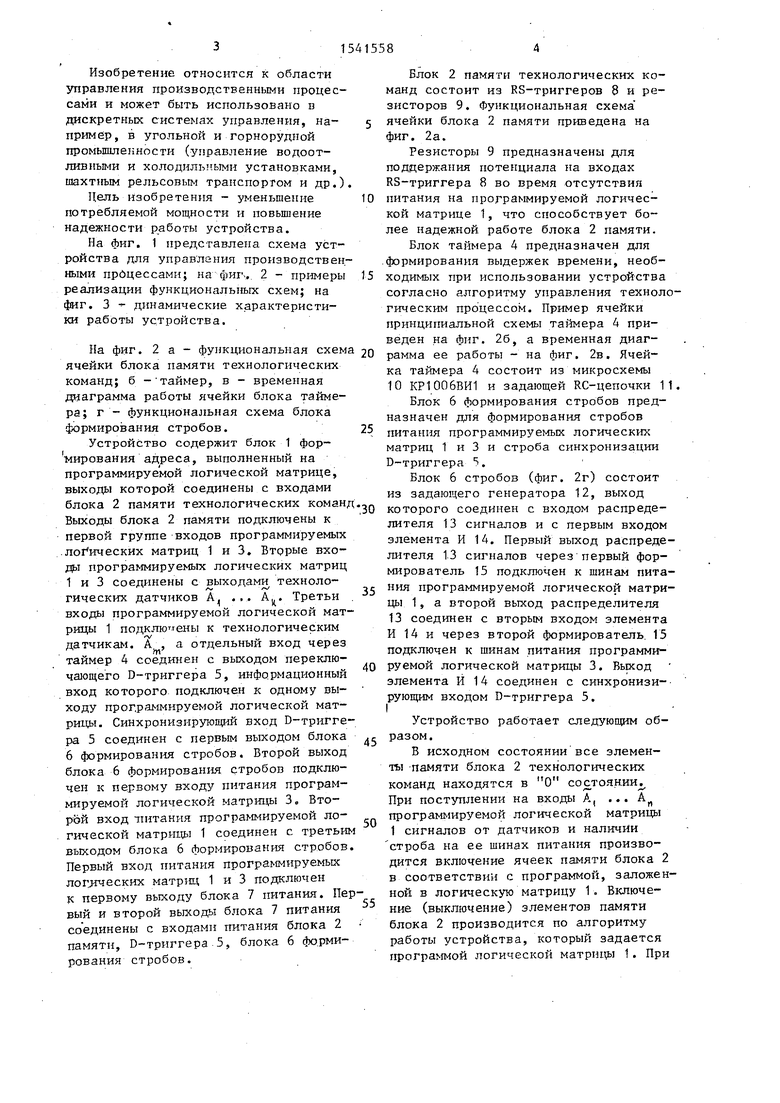

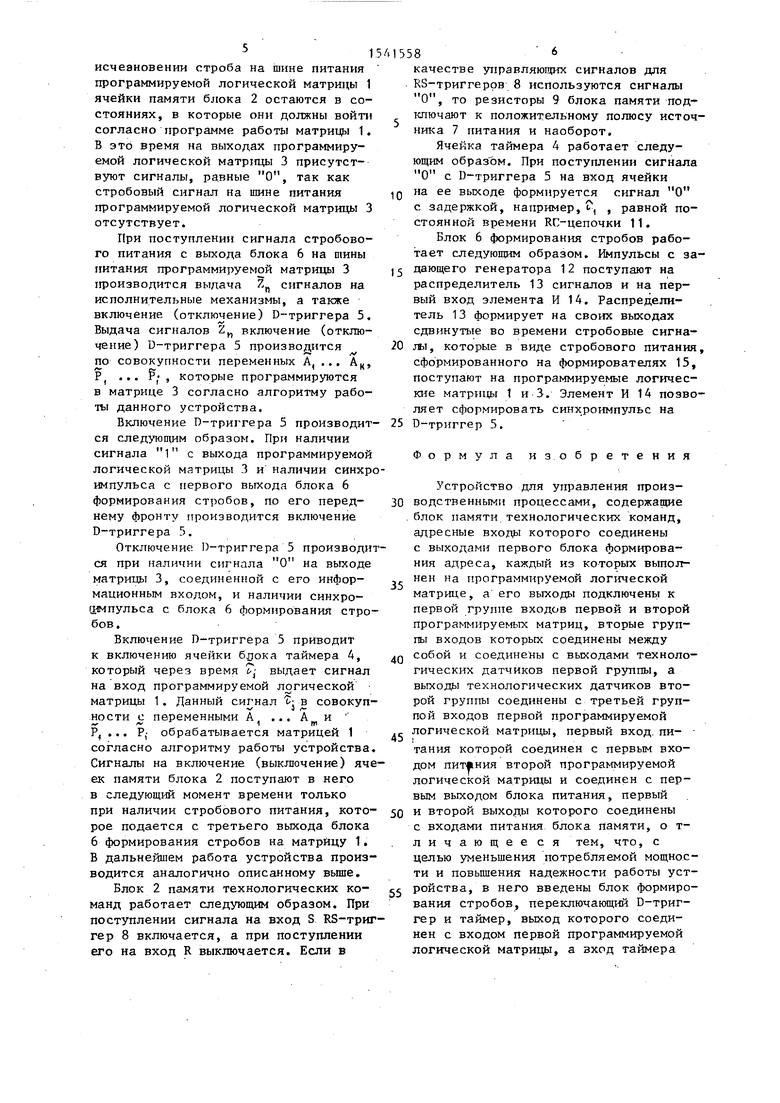

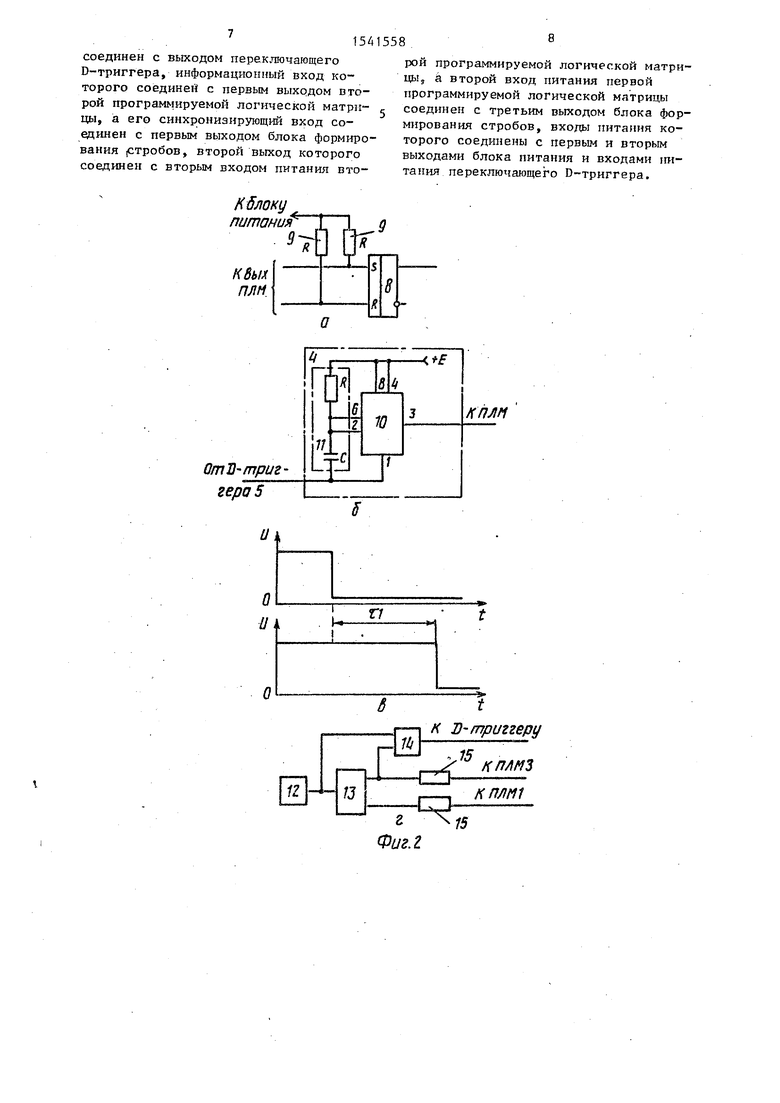

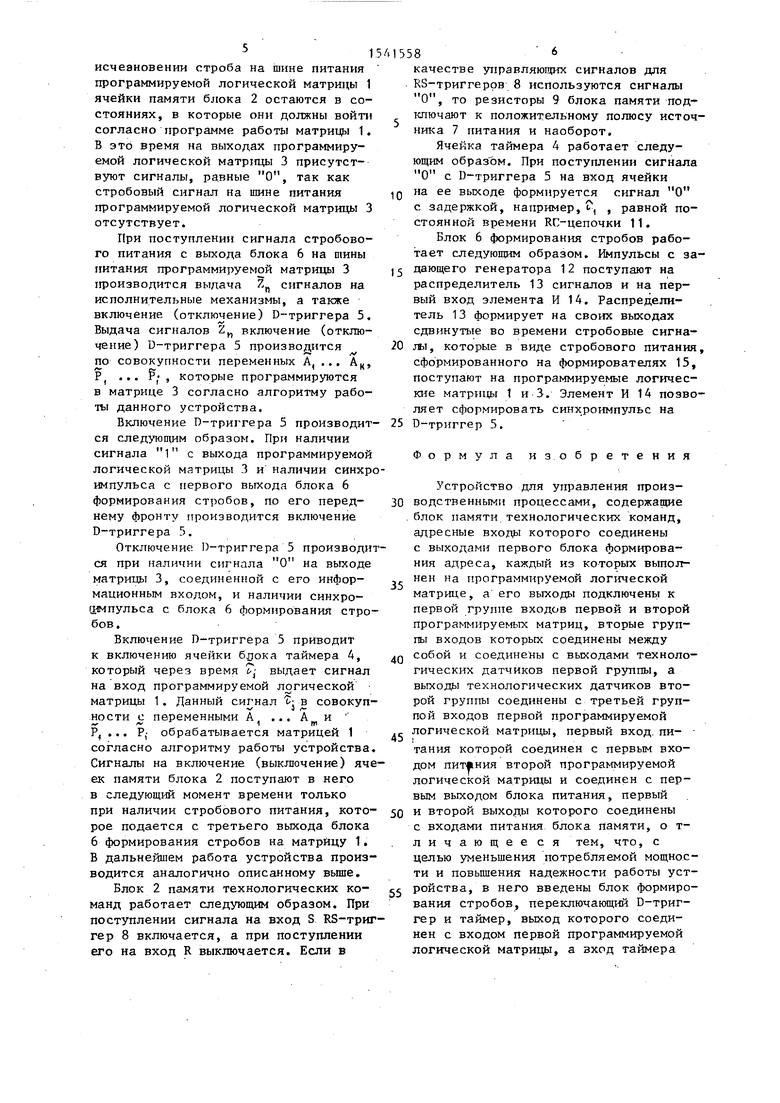

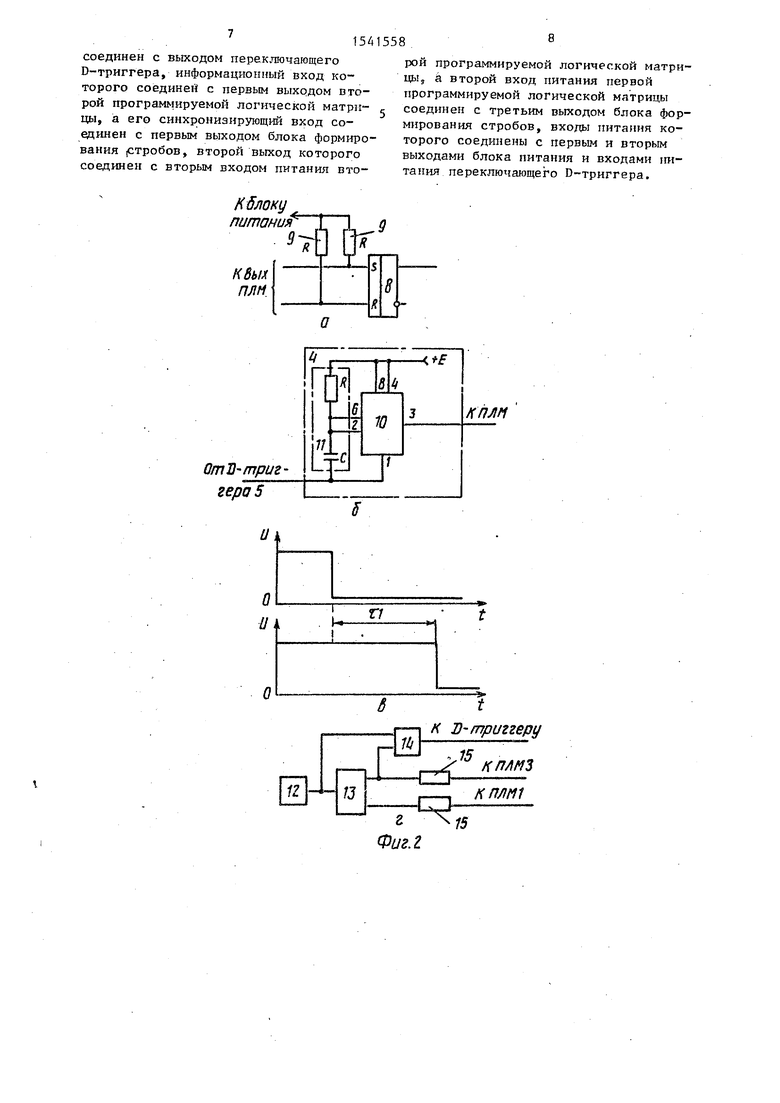

На фиг. 1 предегавлена схема устройства для управления производственными процессами; на фиг. 2 - примеры реализации функциональных схем; на фиг. 3 - динамические характеристики работы устройства.

На фиг. 2 а - функциональная схем ячейки блока памяти технологических команд; б - таймер, в - временная диаграмма работы ячейки блока таймера; г - функциональная схема блока формирования стробов.

Устройство содержит блок 1 формирования адреса, выполненный на программируемой логической матрице, выходы которой соединены с входами блока 2 памяти технологических коман Выходы блока 2 памяти подключены к первой группе входов программируемых логических матриц 1 и 3. Вторые входы программируемых логических матриц 1 и 3 соединены с выходами технологических датчиков А,, ... Ац. Третьи входы программируемой логической матрицы 1 подключены к технологическим датчикам. А , а отдельный вход через таймер 4 соединен с выходом переключающего D-триггера 5, информационный вход которого подключен к одному выходу программируемой логической матрицы. Синхронизирующий вход D-триггера 5 соединен с первым выходом блока 6 формирования стробов. Второй выход блока 6 формирования стробов подключен к первому входу питания программируемой логической матрицы 3. Второй вход -питания программируемой логической матрицы 1 соединен с третьи выходом блока 6 формирования стробов Первый вход питания программируемых логических матриц 1 и 3 подключен к первому выходу блока 7 питания. Певый и второй выходы блока 1 питания соединены с входами питания блока 2 памяти, D-триггера 5, блока 6 формирования стробов.

0

5

Блок 2 памяти технологических команд состоит из RS-триггеров 8 и резисторов 9. Функциональная схема ячейки блока 2 памяти приведена на фиг. 2а.

Резисторы 9 предназначены для поддержания потенциала на входах RS-триггера 8 во время отсутствия 0 питания на программируемой логической матрице 1, что способствует более надежной работе блока 2 памяти.

Блок таймера 4 предназначен для формирования выдержек времени, необ- 5 ходимых при использовании устройства согласно алгоритму управления технологическим процессом. Пример ячейки принципиальной схемы таймера 4 приведен на фиг. 26, а временная диаграмма ее работы - на фиг. 2в. Ячейка таймера 4 состоит из микросхемы 10 КР1006ВИ1 и задающей КС-цепочки 11.

Блок 6 формирования стробов предназначен для формирования стробов питания программируемых логических матриц 1 и 3 и строба синхронизации D-триггера 5.

Блок 6 стробов (фиг. 2г) состоит из задающего генератора 12, выход 0 которого соединен с входом распределителя 13 сигналов и с первым входом элемента И 14. Первый выход распределителя 13 сигналов через первый формирователь 15 подключен к шинам пита- 5 ния программируемой логической матрицы 1 , а второй выход распределителя 13 соединен с вторым входом элемента И 14 и через второй формирователь 15 подключен к шинам питания программируемой логической матрицы 3. Выход элемента И 14 соединен с синхронизирующим входом D-триггера 5.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти блока 2 технологических команд находятся в О состоянии.. При поступлении на входы А, ... АП программируемой логической матрицы 1 сигналов от датчиков и наличии строба на ее шинах питания производится включение ячеек памяти блока 2 в соответствии с программой, заложенной в логическую матрицу 1. Включе- ние (выключение) элементов памяти блока 2 производится по алгоритму работы устройства, который задается программой логической матрицы 1. При

0

5

0

исчезновении строба на шнне питания программируемой логической матрицы 1 ячейки памяти блока 2 остаются в состояниях, в которые они должны войти согласно программе работы матрицы 1. В это время на выходах программируемой логической матрицы 3 присутствуют сигналы, равные О, так как стробовый сигнал на шине питания программируемой логической матрицы 3 отсутствует.

При поступлении сигнала стробово- го питания с выхода блока 6 на шины питания программируемой матрицы 3 ггроизводится выдача Zn сигналов на исполнительные механизмы, а также включение (отключение) D-триггера 5. Выдача сигналов 2М включение (отключение) D-триггера 5 производится по совокупности переменных А,... Аи, Р( ... ; , которые программируются в матрице 3 согласно алгоритму работы данного устройства.

Включение D-триггера 5 производится следующим образом. При наличии сигнала 1м с выхода программируемой логической матрицы 3 и наличии синхримпульса с первого выхода блока 6 формирования стробов, по его переднему фронту производится включение D-триггера 5.

Отключение D-триггера 5 производися при наличии сигнала О на выходе матрицы 3, соединенной с его информационным входом, и наличии синхро- гимпульса с блока 6 формирования стробов.

Включение D-триггера 5 приводит к включению ячейки блока таймера 4, который через время Ј, выдает сигнал на вход программируемой логической матрицы 1. Данный сигнал 1. в совокупs Злности с переменными А, ... А„ и

+ Л 1Гт

Р ... Р, обрабатывается матрицей 1 согласно алгоритму работы устройства Сигналы на включение (выключение) ячеек памяти блока 2 поступают в него в следующий момент времени только при наличии стробового питания, которое подается с третьего выхода блока 6 формирования стробов на матрицу 1. В дальнейшем работа устройства производится аналогично описанному выше.

Блок 2 памяти технологических команд работает следующим образом. При поступлении сигнала на вход S RS-триг гер 8 включается, а при поступлении его на вход R выключается. Если в

качестве управляющих сигналов для RS-триггеров 8 используются сигналы О, то резисторы 9 блока памяти подключают к положительному полюсу источника 7 питания и наоборот.

Ячейка таймера 4 работает следующим образом. При поступлении сигнала О с D-триггера 5 на вход ячейки на ее выходе формируется сигнал О с задержкой, например, t4, , равной постоянной времени RC-цепочки 11.

Блок 6 формирования стробов работает следующим образом. Импульсы с задающего генератора 12 поступают на распределитель 13 сигналов и на первый вход элемента И 14. Распределитель 13 формирует на своих выходах сдвинутые во времени стробовые сигналы, которые в виде стробового питания, сформированного на формирователях 15, поступают на программируемые логические матрицы 1 и 3. Элемент И 14 позволяет сформировать синхроимпульс на 5 D-триггер 5.

Формула изобретения

5

0

0

5

0

5

Устройство для управления производственными процессами, содержащие блок памяти технологических команд, адресные входы которого соединены с выходами первого блока формирования адреса, каждый из которых выполнен на программируемой логической матрице, а его выходы подключены к первой группе входов первой и второй программируемых матриц, вторые группы входов которых соединены между собой и соединены с выходами технологических датчиков первой группы, а выходы технологических датчиков второй группы соединены с третьей группой входов первой программируемой логической матрицы, первый вход питания которой соединен с первым входом питания второй программируемой логической матрицы и соединен с первым выходом блока питания, первый 0 и второй выходы которого соединены с входами питания блока памяти, о т- личающее ся тем, что, с целью уменьшения потребляемой мощности и повышения надежности работы устройства, в него введены блок формирования стробов, переключающий D-триггер и таймер, выход которого соединен с входом первой программируемой логической матрицы, а вход таймера

5

соединен с выходом переключающего D-триггера, информационный вход которого соединен с первым выходом а торой программируемой логической матрицы, а его синхронизирующий вход соединен с первым выходом блока формирования ,стробов,, второй выход которого соединен с вторым входом питания второй программируемой логической матрицы, а второй вход питания первой программируемой логической матрицы соединен с третьим выходом блока формирования стробов, входы питания которого соединены с первым и вторым выходами блока питания и входами питания переключающего D-триггера.

Фи&з

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ | 1989 |

|

RU2022344C1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для ввода дискретных сигналов | 1988 |

|

SU1522221A1 |

| Цифровое устройство для управления машиной непрерывного литья заготовок | 1989 |

|

SU1632621A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для контроля работы сельскохозяйственных машин для внесения жидкостей | 1988 |

|

SU1676565A1 |

| Устройство для автоматического управления водоотливной установкой | 1989 |

|

SU1656499A1 |

| Устройство контроля и управления технологическим комплексом для намотки изделий | 1989 |

|

SU1661721A1 |

Изобретение относится к области управления производственными процессами и может быть использовано в дискретных системах управления, например, в угольной и горнорудной отраслях промышленности (управление водоотливными и холодильными установками, шахтным рельсовым транспортом и др.). Целью изобретения является уменьшение потребляемой мощности и повышение надежности устройства в работе. Указанная цель достигается тем, что в устройство для управления производственными процессами, содержащее первую и вторую программируемые логические матрицы 1 и 3, блок 2 памяти технологических команд, блок питания, дополнительно введены таймер 4, D-триггер 5 и формирователь 6 стробов, что позволяет временно задействовать ПЛМ в работу, сберегая при этом их ресурс и снижая потребляемую мощность устройства. 3 ил.

| Баранов С.И | |||

| и Баркалов А.А | |||

| Применение программируемых логических матриц в цифровой технике | |||

| - Зарубежная радиоэлектроника, 1982, № 6, с | |||

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

Авторы

Даты

1990-02-07—Публикация

1988-02-23—Подача