Изобретение относится к вычислительной технике и может быть использовано в устройствах отладки микро- 20 программ и для проверки работоспособности и диагностики аппаратуры микропроцессорных устройств (МПУ).

Цель изобретения - расширение области применения за счет возможности 25 совместного использования блоков памяти микропрограмм устройства,отладки и отлаживаемого микропрограммного блока

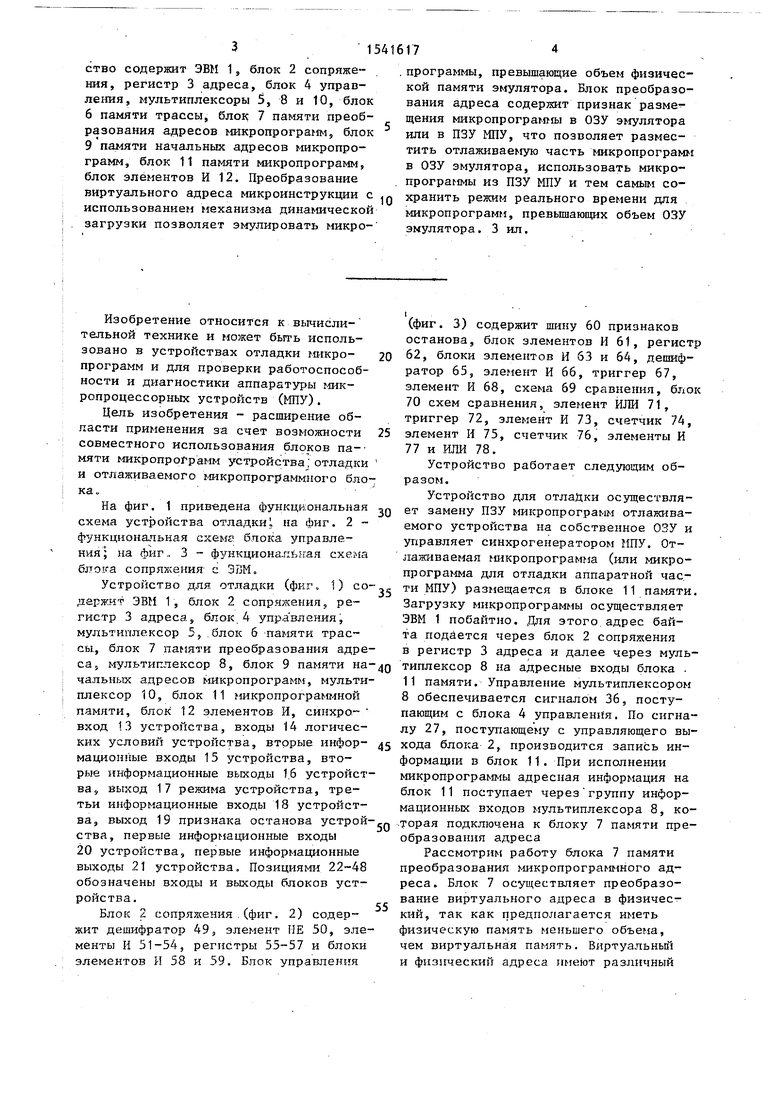

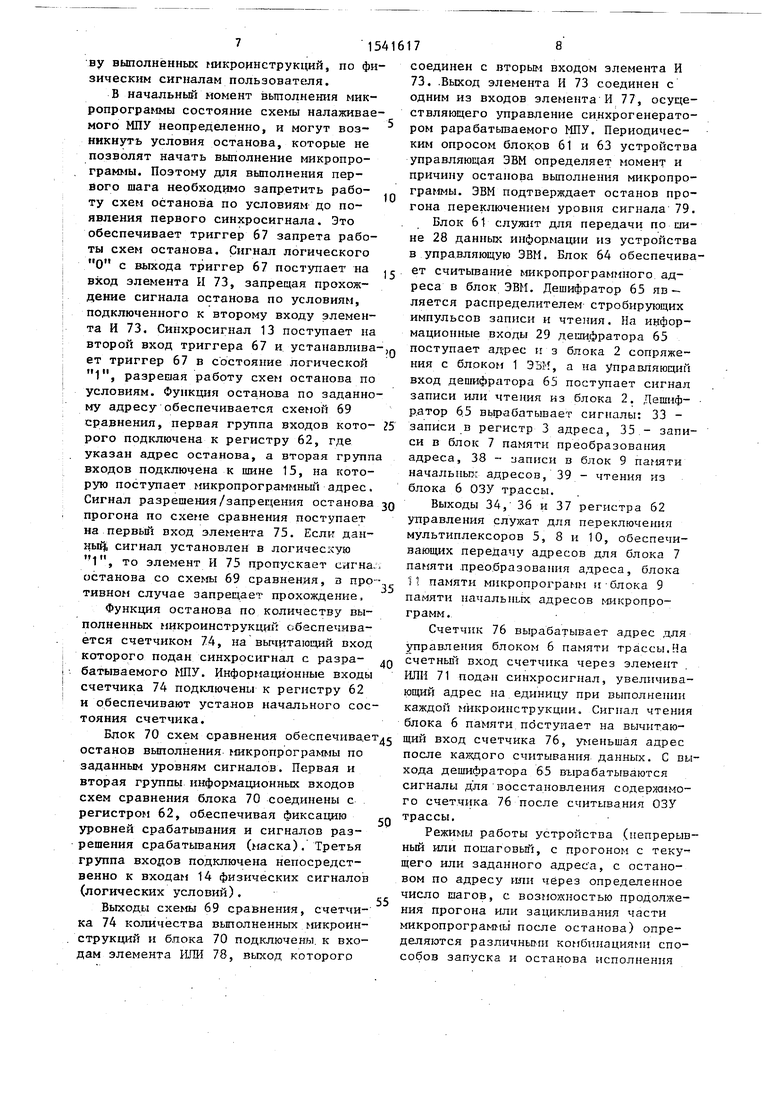

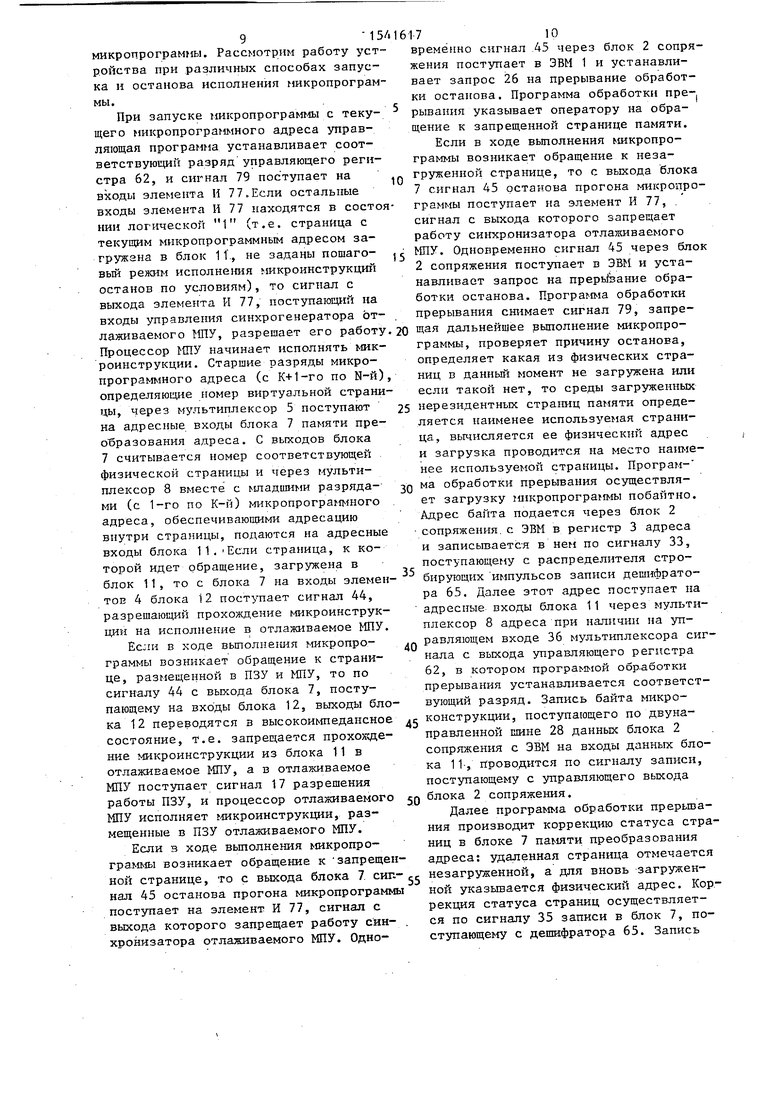

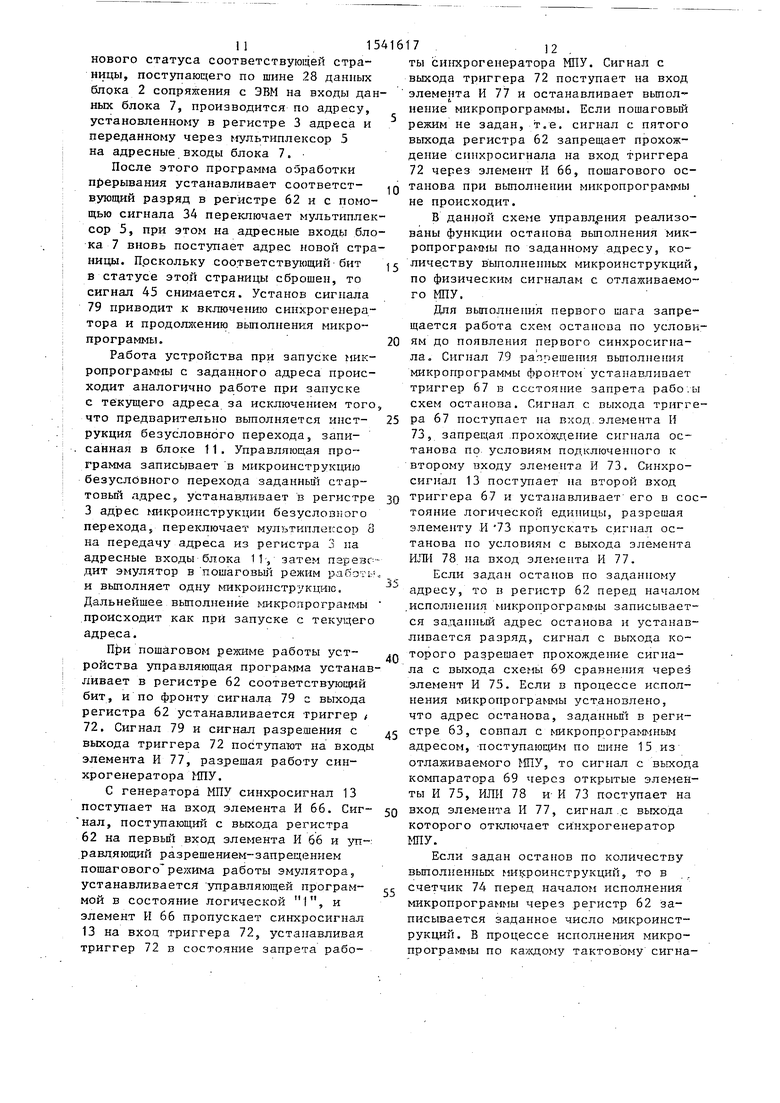

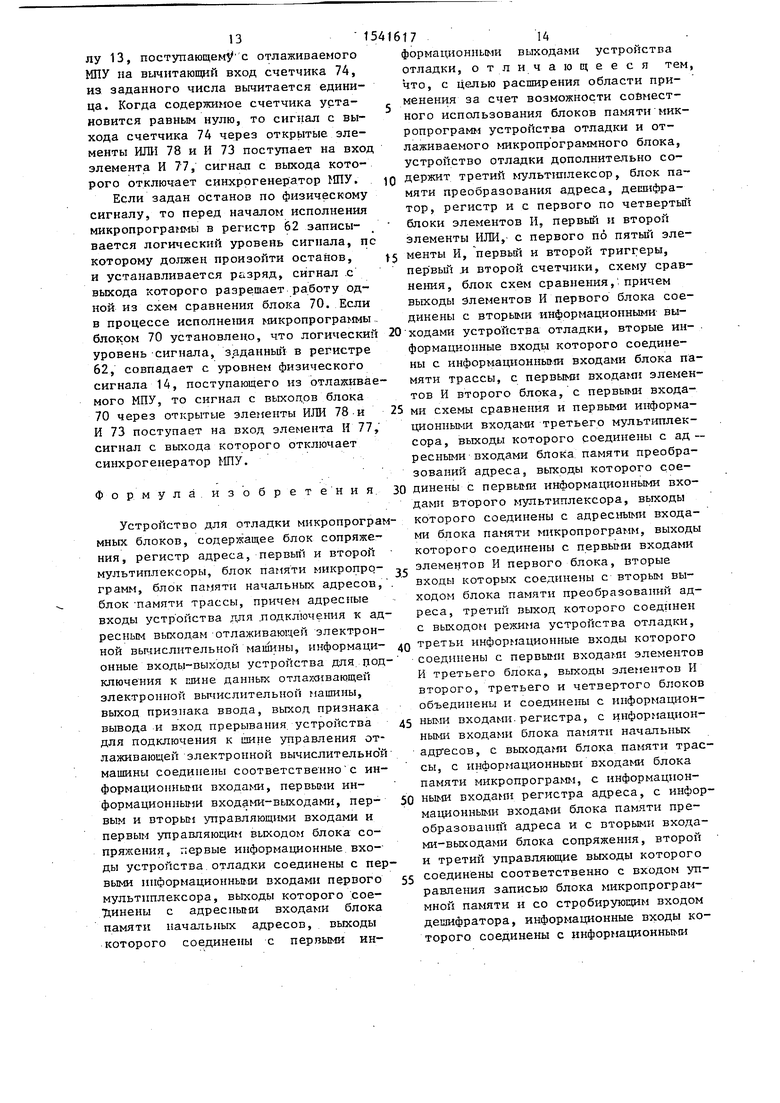

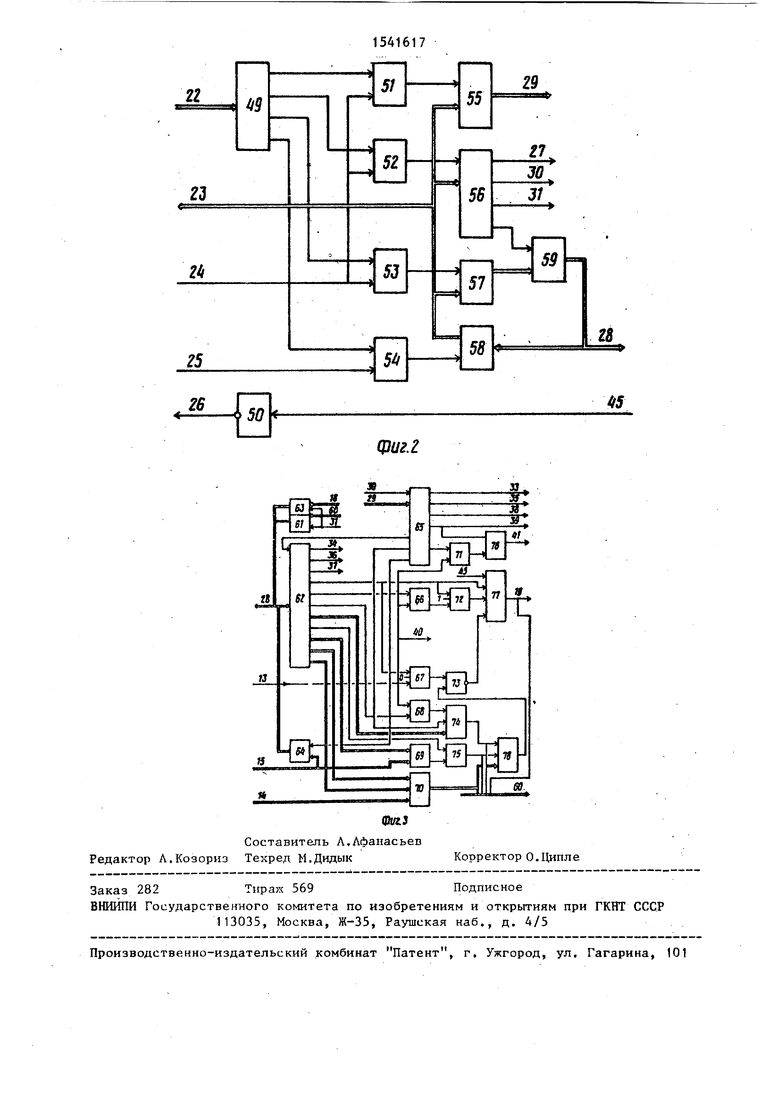

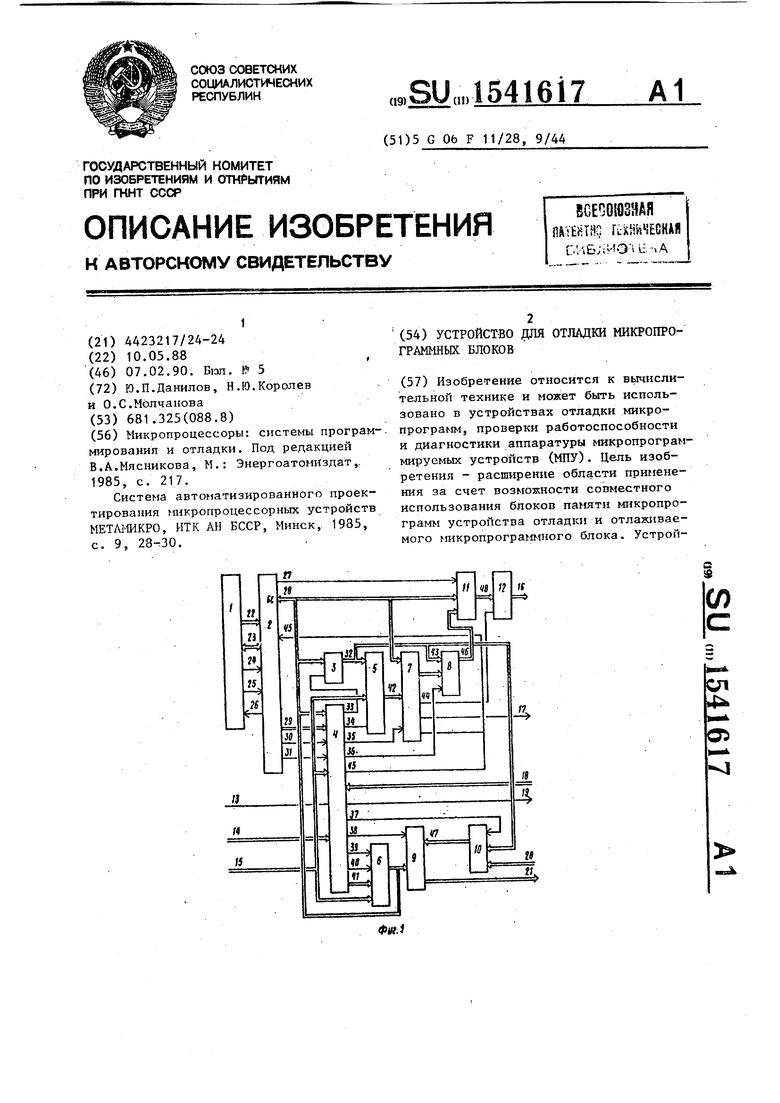

На фиг. 1 приведена функц -; опальная Q схема устройства отладки, на фиг. 2 - функциональная схеме бчока управления; на фиг, 3 - функциональная схема бло га сопряжения с ЭВМ,

Устройство для отладки (фиг. 1) содержит ЭВМ 1, блок 2 сопряжения, регистр 3 адреса, блок 4 управления, мультиплексор 5, блок 6 памяти трассы, блок 7 памяти преобразования адреса } мультиплексор 8, блок 9 памяти на-дд чальных адресов микропрограмм, мультиплексор 10, блок 11 микропрограммной памяти, блок 12 элементов И, синхро- вход 13 устройства, входы 14 логических условий устройства, вторые инфор- 45 мациоиные входы 15 устройства, вторые информационные выходы 16 устройства, выход 17 режима устройства, третьи информационные входы 18 устройст35

ва, выход 19 признака останова устройства, первые информационные входы 20 устройства, первые информационные выходы 21 устройства. Позициями 22-48 обозначены входы и выходы блоков устройства.

Блок 2 сопряжения (фиг. 2) содержит дешифратор 49, элемент НЕ 50, элементы И 51-54, регистры 55-57 и блоки элементов И 58 и 59. Блок управления

0

5

Q

д 5

5

0

5

(фиг. 3) содержит шину 60 признаков останова, блок элементов И 61, регистр 62, блоки элементов И 63 и 64, дешифратор 65, элемент И 66, триггер 67, элемент И 68, схема 69 сравнения, блок 70 схем сравнения, элемент ИЛИ 71, триггер 72, элемент И 73, счетчик 74, элемент И 75, счетчик 76, элементы И 77 и ИЛИ 78.

Устройство работает следующим образом.

Устройство для отладки осуществляет замену ПЗУ микропрограмм отлаживаемого устройства на собственное ОЗУ и управляет синхрогенератором МПУ. Отлаживаемая микропрограмма (или микропрограмма для отладки аппаратной части МПУ) размещается в блоке 11 памяти. Загрузку микропрограммы осуществляет ЭВМ 1 побайтно. Для этого адрес байта подается через блок 2 сопряжения в регистр 3 адреса и далее через мультиплексор 8 на адресные входы блока . 11 памяти. Управление мультиплексором 8 обеспечивается сигналом 36, поступающим с блока 4 управления. По сигналу 27, поступающему с управляющего выхода блока 2, производится запись информации в блок 11. При исполнении микропрограммы адресная информация на блок 11 поступает через группу информационных входов мультиплексора 8, которая подключена к блоку 7 памяти преобразования адреса

Рассмотрим работу блока 7 памяти преобразования микропрограммного адреса. Блок 7 осуществляет преобразование виртуального адреса в физический, так как предполагается иметь физическую память меньшего объема, чем виртуальная память. Виртуальный и физический адреса имеют различный

формат.Пусть виртуальный адрес имеет следующую структуру: адресные разряды с 1-го по К-й обеспечивают адресацию внутри страницы, с К+1-го по N-й- номер виртуальной страницы памяти. Блок 7 памяти преобразования адреса осуществляет преобразование только номера страницы, оставляя разряды с 1-го по К-й без изменения.

Таким образом, физический адрес имеет структуру: адресные разряды с 1-го по К-й обеспечивают адресацию внутри страницы, с K+1-ro по М-й-но- мер физической страницы памяти. Преобразование адреса осуществляется подачей на адресные входы ОЗУ номера виртуальной страницы и считывания с выходов ОЗУ номера физической страницы со статусной информацией. Статусная информация содержит следующие данные: первый разряд - признак размещения страницы (в ОЗУ либо в ПЗУ, МПУ); второй - запрос обслуживания и останова прогона микропрограммы для всех виртуальных страниц, работа с которыми запрещена, и для страниц, которые не загружены в блок 11 устройства в разрядах с 3-го по (М-К+3)-й указывается номер физической страницы. При инициализации в блоке 7 все виртуальные страницы указываются незагруженными .

Перед выполнением микропрограммы оператор делав - начальную разметку памяти, т.е. укатывает тип каждой виртуальной страницы памяти.Тип страницы определяет, где размещена данная страница: в ОЗУ, ПЗУ, либо запрещена для работы. При размещении страницы в блоке 11 возможны два варианта: страница размещена постоянно (резидентная страница) либо загружается по требованию (нерезидентная страница). В памяти управляющей ЭВМ хранятся типы виртуалышх страниц, их приоритеты для программы-загрузчика. Для записи статусной информации и номера физической страницы в блок 7 памяти преобразования адреса ЭВМ устанавливает адрес в регистр 3 адреса, адрес передается на адресные входы блока 7 через мультиплексор 5, управляющий вход

1541617

10

15

20

Блок 4 осуществляет управление схемой устройства отладки. Для наладки аппаратной части и программного обеспечения МПУ необходимо обеспечить управление выполнением микропрограммы. Б данном устройстве отладки реализованы функции: запуска программы с текущего или заданного адреса, выполнение микропрограммы в непрерывном или пошаговом режиме, останова выполнения по требованию оператора, заданному адресу, количеству выполненных микрокоманд, по физическим сигналам (логическим условиям), зацикливание определенной части микропрограммы.Регаты выполнения микропрограммы получаются из комбинации функций устройства.

Управление прогоном (выполнением) микропрограммы основано на управлении синхрогенератором налаживаемого МПУ (фиг. 3). Выход элемента И 77 разрешает/запрещает работу синхроге- 25 нератора. Управление прогоном микропрограммы осуществляется с помощью управляющего регистра 62. На входы элемента И 77 поступают сигналы управления: с выхода блока 7 ОЗУ преобразования адреса (сигнал 45), с выхода триггера 72, обеспечивающего пошаговый режим работы, с четвертого выхода регистра 62 управления - сигнал разрешения работы от ЭВМ, с выхода элемента И 73, являющийся сигналом прекращения работы от схем останова по условиям (по адресу, количеству выполненных микроинструкций, физическим сигналам (логическим условиям)).

Сигнал, поступающий с пятого выхода регистра 62 на первый вход элемента 66, управляет разрешением/запрещением пошагового режима работы устройства. Если данный сигнал установлен в состояние логической 1, то синхросигнал проходит через элемент 66 на вход триггера 72, устанавливает триггер 72 в состояние запрета работы синхрогенератора МПУ (состояние логического О) и останавливает выполнение микропрограммы. Если данный сигнал установлен в состояние логического О, то элемент 66 запрещает прохождение синхросигнала на вход трнгге30

35

40

45

50

торого соединен с выходом 33 блока 3,- ра 72 и пошагового останова при выполнеобходимая информация передается по шине 28 данных блока 2 сопряжения с блоком 1 ЭВМ, сигнал 35 управляет записью в блок 7.

нении микропрограммы не происходит. В данной схеме управления реализованы функции останова выполнения микропрограммы по заданному адресу, колнчест-о1541617

0

Блок 4 осуществляет управление схемой устройства отладки. Для наладки аппаратной части и программного обеспечения МПУ необходимо обеспечить управление выполнением микропрограммы. Б данном устройстве отладки реализованы функции: запуска программы с текущего или заданного адреса, выполнение микропрограммы в непрерывном или пошаговом режиме, останова выполнения по требованию оператора, заданному адресу, количеству выполненных микрокоманд, по физическим сигналам (логическим условиям), зацикливание определенной части микропрограммы.Регаты выполнения микропрограммы получаются из комбинации функций устройства.

Управление прогоном (выполнением) микропрограммы основано на управлении синхрогенератором налаживаемого МПУ (фиг. 3). Выход элемента И 77 разрешает/запрещает работу синхроге- 5 нератора. Управление прогоном микропрограммы осуществляется с помощью управляющего регистра 62. На входы элемента И 77 поступают сигналы управления: с выхода блока 7 ОЗУ преобразования адреса (сигнал 45), с выхода триггера 72, обеспечивающего пошаговый режим работы, с четвертого выхода регистра 62 управления - сигнал разрешения работы от ЭВМ, с выхода элемента И 73, являющийся сигналом прекращения работы от схем останова по условиям (по адресу, количеству выполненных микроинструкций, физическим сигналам (логическим условиям)).

Сигнал, поступающий с пятого выхода регистра 62 на первый вход элемента 66, управляет разрешением/запрещением пошагового режима работы устройства. Если данный сигнал установлен в состояние логической 1, то синхросигнал проходит через элемент 66 на вход триггера 72, устанавливает триггер 72 в состояние запрета работы синхрогенератора МПУ (состояние логического О) и останавливает выполнение микропрограммы. Если данный сигнал установлен в состояние логического О, то элемент 66 запрещает прохождение синхросигнала на вход трнгге0

5

0

5

0

нении микропрограммы не происходит. В данной схеме управления реализованы функции останова выполнения микропрограммы по заданному адресу, колнчеству выполненных никроинструкций, по физическим сигналам пользователя.

В начальный момент выполнения микропрограммы состояние схемы налаживаемого ЦПУ неопределенно, и могут возникнуть условия останова, которые не позволят начать выполнение микропрограммы. Поэтому для выполнения первого шага необходимо запретить работу схем останова по условиям до появления первого синхросигнала. Это обеспечивает триггер 67 запрета работы схем останова. Сигнал логического О с выхода триггер 67 поступает на вход элемента И 73, запрещая прохождение сигнала останова по условиям, подключенного к второму входу элемента И 73. Синхросигнал 13 поступает на

5

соединен с вторым входом элемента И 73. Выход элемента И 73 соединен с одним из входов элемента И 77, осуществляющего управление синхрогенерато- ром рарабатываемого МПУ. Периодическим опросом блоков 61 и 63 устройства управляющая ЭВМ определяет момент и причину останова выполнения микропрограммы. ЭВМ подтверждает останов прогона переключением уровня сигнала 79. Блок 61 служит для передачи по стане 28 данных информации из устройства в управляющую ЭВМ. Блок 64 обеспечивает считывание микропрограммного адреса в блок ЭВМ. Дешифратор 65 является распределителем стробирующих импульсов записи и чтения. На информационные входы 29 дешифратора 65

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1495789A1 |

| Устройство для отладки многомодульной ЦВМ | 1987 |

|

SU1564630A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство для отладки программ | 1982 |

|

SU1062708A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах отладки микропрограмм, проверки работоспособности и диагностики аппаратуры микропрограммируемых устройств (МПУ). Цель изобретения - расширение области применения за счет возможности совместного использования блоков памяти микропрограмм устройства отладки и отлаживаемого микропрограммного блока. Устройство содержит ЭВМ 1, блок 2 сопряжения, регистр 3 адреса, блок 4 управления, мультиплексоры 5,8 и 10, блок 6 памяти трассы, блок 7 памяти преобразования адресов микропрограмм, блок 9 памяти начальных адресов микропрограмм, блок 11 памяти микропрограмм, блок элементов И 12. Преобразование виртуального адреса микроинструкции с использованием механизма динамической загрузки позволяет эмулировать микропрограммы, превышающие объем физической памяти эмулятора. Блок преобразования адреса содержит признак размещения микропрограммы в ОЗУ эмулятора или в ПЗУ МПУ, что позволяет разместить отлаживаемую часть микропрограмм в ОЗУ эмулятора и использовать микропрограммы из из ПЗУ МПУ и тем самым сохранить режим реального времени для микропрограмм, превышающих объем ОЗУ эмулятора. 3 ил.

второй вход триггера 67 и устанавлива-, поступает адрес и з блока 2 сопряжеет триггер 67 в состояние логической 1, разрешая работу схем останова по условиям. Функция останова по заданному адресу обеспечивается схемой 69 сравнения, первая группа входов кото- 25 рого подключена к регистру 62, где указан адрес останова, а вторая группа входов подключена к шине 15, на которую поступает микропрограммный адрес. Сигнал разрешения/запрещения останова зо прогона по схеме сравнения поступает на первый вход элемента 75. Если данный, сигнал установлен в логическую 1, то элемент И 75 пропускает t-игна ,

ния с блоком 1 ЭВМ, а на управляющий вход дешифратора 65 поступает сигнал записи или чтения из блока 2. Дешифратор 65 вырабатывает сигналы: 33 - записи в регистр 3 адреса, 35 - запи си в блок 7 памяти преобразования адреса, 38 - записи в блок 9 памяти начальны адресов, 39 - чтения из блока 6 ОЗУ трассы.

Выходы 34, 36 и 37 регистра 62 управления служат для переключения мультиплексоров 5, 8 и 10, обеспечивающих передачу адресов для блока 7 памяти преобразования адреса, блока 1 памяти микропрограмм и блока 9 памяти начальных адресов микропрограмм.

останова со схемы 69 сравнения, з про тивном случае запрещает прохождение,

Функция останова по количеству выполненных микроинструкций обеспечивается счетчиком 74, на вычитающий вход которого подан синхросигнал с разрабатываемого МПУ. Информационные входы счетчика 74 подключены к регистру 62 и обеспечивают установ начального состояния счетчика.

Блок 70 схем сравнения обеспечивает щий вход счетчика 76, уменьшая адрес

останов выполнения микропрограммы по заданным уровням сигналов. Первая и вторая группы информационных входов схем сравнения блока 70 соединены с регистром 62, обеспечивая фиксацию уровней срабатывания и сигналов разрешения срабатывания (маска). Третья группа входов подключена непосредственно к входам 14 физических сигналов (логических условий).

Выходы схемы 69 сравнения, счетчика 74 количества выполненных микроинструкций и блока 70 подключены к входам элемента ИЛИ 78, выход которого

о

5

0

ния с блоком 1 ЭВМ, а на управляющий вход дешифратора 65 поступает сигнал записи или чтения из блока 2. Дешифратор 65 вырабатывает сигналы: 33 - записи в регистр 3 адреса, 35 - записи в блок 7 памяти преобразования адреса, 38 - записи в блок 9 памяти начальны адресов, 39 - чтения из блока 6 ОЗУ трассы.

Выходы 34, 36 и 37 регистра 62 управления служат для переключения мультиплексоров 5, 8 и 10, обеспечивающих передачу адресов для блока 7 памяти преобразования адреса, блока 1 памяти микропрограмм и блока 9 памяти начальных адресов микропрограмм.

Счетчик 76 вырабатывает адрес для управления блоком 6 памяти трассы.Ча счетный вход счетчика через элемент ИЛИ 71 пода-н синхросигнал, увеличивающий адрес на единицу при выполнении каждой микроинструкции. Сигнал чтения блока 6 памяти поступает на вычитаю0

5

после каждого считывания данных. С выхода дешифратора 65 вырабатываются сигналы для восстановления содержимого счетчика 76 после считывания ОЗУ трассы.

Режимы работы устройства (непрерывный или пошаговый, с прогоном с текущего или заданного адреса, с остановом по адресу или через определенное число иагов, с возможностью продолжения прогона или зацикливания части микропрограммы после останова) определяются различными комбинациями способов запуска и останова исполнения

9 154

микропрограммы. Рассмотрим работу устройства при различных способах запуска и останова исполнения микропрограммы.

При запуске микропрограммы с теку- щего микропрограммного адреса управляющая программа устанавливает соответствующий разряд управляющего регистра 62, и сигнал 79 поступает на входы элемента И 77.Если остальные входы элемента И 77 находятся в состоянии логической 1 (т.е. страница с текущим микропрограммным адресом загружена в блок 11, не заданы пошаго- вый режим исполнения микроинструкций останов по условиям), то сигнал с выхода элемента И 77, поступающий на входы управления синхрогенератора отлаживаемого Т1ПУ, разрешает его работу. Процессор МПУ начинает исполнять микроинструкции. Старшие разряды микропрограммного адреса (с K+1-ro по Ы-й), определяющие номер виртуальной страницы, через мультиплексор 5 поступают на адресные входы блока 7 памяти преобразования адреса. С выходов блока 7 считывается номер соответствующей физической страницы и через мультиплексор 8 вместе с младшими разряда- ми (с 1-го по К-й) микропрограммного адреса, обеспечивающими адресацию внутри страницы, подаются на адресные входы блока 11. Если страница, к которой идет обращение, загружена в блок 11, то с блока 7 на входы элементов 4 блока 12 поступает сигнал 44, разрешающий прохождение микроинструкции на исполнение в отлаживаемое МПУ.

Если в ходе выполнения микропро- граммы возникает обращение к странице, размещенной в ПЗУ и МПУ, то по сигналу 44 с выхода блока 7, поступающему на входы блока 12, выходы блока 1 2 переводятся в высокоимпедансное состояние, т.е. запрещается прохождение микроинструкции из блока 11 в отлаживаемое МПУ, а в отлаживаемое МПУ поступает сигнал 17 разрешения работы ПЗУ, и процессор отлаживаемого МПУ исполняет микроинструкции, размещенные в ПЗУ отлаживаемого МПУ.

Если в ходе выполнения микропрограммы возникает обращение к запрещенной странице, то с выхода блока 7 сиг.- нал 45 останова прогона микропрограммы поступает на элемент И 77, сигнал с выхода которого запрещает работу синхронизатора отлаживаемого МПУ. Одно

5 0

« 0

с

5

1710

временно сигнал 45 через блок 2 сопряжения поступает в ЭВМ 1 и устанавливает запрос 26 на прерывание обработки останова. Программа обработки прерывания указывает оператору на обращение к запрещенной странице памяти.

Если в ходе выполнения микропрограммы возникает обращение к незагруженной странице, то с выхода блока 7 сигнал 45 останова прогона микропрограммы поступает на элемент И 77, сигнал с выхода которого запрещает работу синхронизатора отлаживаемого МПУ. Одновременно сигнал 45 через блок 2 сопряжения поступает в ЭВМ и устанавливает запрос на прерывание обработки останова. Программа обработки прерывания снимает сигнал 79, запрещая дальнейшее выполнение микропрограммы, проверяет причину останова, определяет какая из физических страниц в данный момент не загружена или если такой нет, то среды загруженных нерезидентных страниц памяти определяется наименее используемая страница, вычисляется ее физический адрес и загрузка проводится на место наименее используемой страницы. Програм- ма обработки прерывания осуществляет загрузку микропрограммы побайтно. Адрес байта подается через блок 2 сопряжения с ЭВМ в регистр 3 адреса и записывается в нем по сигналу 33, поступающему с распределителя стро- бирующих импульсов записи дешифратора 65. Далее этот адрес поступает на адресные входы блока 11 через мультиплексор 8 адреса при наличии на управляющем входе 36 мультиплексора сигнала с выхода управляющего регистра 62, в котором программой обработки прерывания устанавливается соответствующий разряд. Запись байта микроконструкции, поступающего по двунаправленной шине 28 данных блока 2 сопряжения с ЭВМ на входы данных блока 11, лроводится по сигналу записи, поступающему с управляющего выхода блока 2 сопряжения.

Далее программа обработки прерывания производит коррекцию статуса страниц в блоке 7 памяти преобразования адреса: удаленная страница отмечается незагруженной, а для вновь загруженной указывается физический адрес. Коррекция статуса страниц осуществляется по сигналу 35 записи в блок 7, поступающему с дешифратора 65. Запись

нового статуса соответствующей страницы, поступающего по шине 28 данных блока 2 сопряжения с ЭВМ на входы данных блока 7, производится по адресу, установленному в регистре 3 адреса и переданному через мультиплексор 5 на адресные входы блока 7.

После этого программа обработки прерывания устанавливает соответствующий разряд в регистре 62 и с помощью сигнала 34 переключает мультиплексор 5, при этом на адресные входы блока 7 вновь поступает адрес новой страницы. Поскольку соответствующий бит в статусе этой страницы сброшен, то сигнал 45 снимается. Установ сигнала 79 приводит к включению синхрогенера- тора и продолжению выполнения микропрограммы.

Работа устройства при запуске микропрограммы с заданного адреса происходит аналогично работе при запуске с текущего адреса за исключением того что предварительно выполняется инструкция безусловного перехода, записанная в блоке 11. Управляющая программа записывает в микроинструкцию безусловного перехода заданный стартовый адрес, устанавливает в регистре 3 адрес микроинструкции безусловного перехода, переключает мультиплексор 8 на передачу адреса из регистра 3 па адресные входы блока 11э затем пзрезс дит эмулятор в пошаговый режим и выполняет одну микроинструкциго. Дальнейшее выполнение микропрограммы происходит как при запуске с текущего адреса.

При пошаговом режиме работы устройства управляющая программа устанавливает в регистре 62 соответствующий бит, и по фронту сигнала 79 с выхода регистра 62 устанавливается триггер t 72. Сигнал 79 и сигнал разрешения с выхода триггера 72 поступают на входы элемента И 77, разрешая работу син- хрогенератора МПУ.

С генератора МПУ синхросигнал 13 поступает на вход элемента И 66. Сиг- нал, поступающий с выхода регистра 62 на первый вход элемента И 66 и управляющий разрешением-запрещением пошагового режима работы эмулятора, устанавливается управляющей программой в состояние логической I, и элемент И 66 пропускает синхросигнал 13 на вхоц триггера 72, устанавливая триггер 72 в состояние запрета рабо

0

5

0

5

0

5

0

5

ты синхрогенератора МПУ. Сигнал с выхода триггера 72 поступает на вход элемента И 77 и останавливает выполнение микропрограммы. Если пошаговый режим не задан, т.е. сигнал с пятого выхода регистра 62 запрещает прохождение синхросигнала на вход триггера 72 через элемент И 66, пошагового останова при выполнении микропрограммы не происходит.

В данной схеме управления реализованы функции останова выполнения микропрограммы по заданному адресу, количеству выполненных микроинструкций, по физическим сигналам с отлаживаемого МПУ.

Для выполнения первого шага запрещается работа схем останова по условиям до появления первого синхросигнала. Сигнал 79 ратпешения выполнения микропрограммы фронтом устанавливает триггер 67 в состояние запрета рабо ы схем останова. Сигнал с выхода триггера 67 поступает на вход элемента И 73, запрещая прохождение сигнала останова по условиям подключенного к второму входу элемента И 73. Синхросигнал 13 поступает на второй вход триггера 67 и устанавливает его в состояние логической единицы, разрешая элементу И 73 пропускать сигнал останова по условиям с выхода элемента ИЛИ 78 на вход элемента И 77.

Если задан останов по заданному адресу, то в регистр 62 перед началом исполнения микропрограммы записывается заданный адрес останова и устанавливается разряд, сигнал с выхода которого разрешает прохождение сигнала с выхода схемы 69 сравнения через элемент И 75. Если в процессе исполнения микропрограммы установлено, что адрес останова, заданный в регистре 63, совпал с микропрограммным адресом, поступающим по шине 15 из отлаживаемого МПУ, то сигнал с выхода компаратора 69 через открытые элементы И 75, ИЛИ 78 и И 73 поступает на вход элемента И 77, сигнал с выхода которого отключает синхрогенератор МПУ.

Если задан останов по количеству выполненных микроинструкций, то в счетчик 74 перед началом исполнения микропрограммы через регистр 62 записывается заданное число микроинструкций. В процессе исполнения микропрограммы по каждому тактовому сигна13

лу 13, поступающему с отлаживаемого МПУ на вычитающий вход счетчика 74, из заданного числа вычитается единица. Когда содержимое счетчика установится равным нулю, то сигнал с выхода счетчика 74 через открытые элементы ИЛИ 78 и И 73 поступает на вхо элемента И 77, сигнал с выхода которого отключает синхрогенератор МПУ.

Если задан останов по физическому сигналу, то перед началом исполнения микропрограммы в регистр 62 записывается логический уровень сигнала, п которому должен произойти останов, и устанавливается разряд, сигнал с выхода которого разрешает работу одной из схем сравнения блока 70. Если в процессе исполнения микропрограммы

блоком 70 установлено, что логический 20 ходами устройства отладки, вторые ин- уровень сигнала, заданный в регистре формационные входы которого соедине- 62, совпадает с уровнем физического ны с информационными входами блока па- сигнала 14, поступающего из отлаживав- мяти трассы, с первыми входами элеменмого МПУ, то сигнал с выходов блока 70 через открытые элементы ИЛИ 78 и И 73 поступает на вход элемента И 77, сигнал с выхода которого отключает синхрогенератор МПУ.

Формула изобретения

Устройство для отладки микропрограммных блоков, содержащее блок сопряжения, регистр адреса, первый и второй

тов И второго блока, с первыми входа- 25 ми схемы сравнения и первыми информационными входами третьего мультиплексора, выходы которого соединены с ад - ресными входами блока памяти преобразований адреса, выходы которого сое- 30 динены с первыми информационными входами второго мультиплексора, выходы которого соединены с адресными входами блока памяти микропрограмм, выходы которого соединены с первыми входами элементов И первого блока, вторые входы которых соединены с вторым выходом блока памяти преобразований адреса, третий выход которого соединен с выходом режима устройства отладки,

35

мультиплексоры, блок памяти микропрограмм, блок памяти начальных адресов, блок памяти трассы, причем адресные входы устройства для подключения к адресным выходам отлаживающей электронной вычислительной машины, информаци- 40 третьи информационные входы которого онные входы-выходы устройства для под- соединены с первыми входами элементов

ключения к мине данных отлаживающей электронной вычислительной машины, выход признака ввода, выход признака вывода и вход прерывания устройства для подключения к шине управления отлаживающей электронной вычислительной машины соединены соответственно с информационными входами, первыми информационными входами-выходами, первым и вторым управляющими входами и первым управляющим выходом блока сопряжения, первые информационные входы устройства отладки соединены с первыми информационными входами первого мультиплексора, выходы которого соединены с адресными входами блока памяти начальных адресов, выходы которого соединены с первыми ин1617

14

формационными выходами устройства отладки, отличающееся тем, что, с целью расширения области применения за счет возможности совместного использования блоков памяти микропрограмм устройства отладки и отлаживаемого микропрограммного блока, устройство отладки дополнительно содержит третий мультиплексор, блок памяти преобразования адреса, дешифратор, регистр и с первого по четвертый блоки элементов И, первый и второй элементы ИЛИ, с первого по пятый эле- 5 менты И, первый и второй триггеры, первый л второй счетчики, схему сравнения, блок схем сравнения, причем выходы элементов И первого блока соединены с вторыми информационными вы0

тов И второго блока, с первыми входа- ми схемы сравнения и первыми информационными входами третьего мультиплексора, выходы которого соединены с ад - ресными входами блока памяти преобразований адреса, выходы которого сое- динены с первыми информационными входами второго мультиплексора, выходы которого соединены с адресными входами блока памяти микропрограмм, выходы которого соединены с первыми входами элементов И первого блока, вторые входы которых соединены с вторым выходом блока памяти преобразований адреса, третий выход которого соединен с выходом режима устройства отладки,

третьи информационные входы которого соединены с первыми входами элементов

И третьего блока, выходы элементов И второго, третьего и четвертого блоков объединены и соединены с информационными входами регистра, с информационными входами блока памяти начальных адресов, с выходам блока памяти трассы, с информационными входами блока памяти микропрограмм, с информацнонными входами регистра адреса, с информационными входами блока памяти пре- образовашш адреса и с вторыми входами-выходами блока сопряжения, второй и третий управляющие выходы которого соединены соответственно с входом управления записью блока микропрограммной памяти и со стробирующим входом дешифратора, информационные входы которого соединены с информационными

15

выходами блока сопряжения, четвертый управляющий выход которого соединен с первыми входами элементов И четвертого и вторыми входами элементов И третьего блоков, а первый выход дешиф- ратора соединен с вычитающим входом первого счетчика и с входом управления чтением блока памяти трассы, адресные входы которого соединены с выходами первого счётчика, суммирующий вход которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с первыми входами пер

вого и второго элементов И, с входом ., третий входы которого соединены соотуправления записью блока памяти трассы, с входом установки в 1 первого триггера и с синхровходом устройства отладки, входы логических условий которого соединены с первыми информационными входами схем сравнений блока, вторые информационные входы и входы разрешения схем сравнений блока соединены соответственно с выходами первой и второй групп регистра, выходы третьей группы которого соединены с вторыми информационными входами схемы сравнения, выход которой соединен с первым входом третьего элемента И, второй вход которого соединен с первым выходом регистра, с второго по седьмой выходы дешифратора соединены соответственно с входами управлегия записью регистра адреса, блока преобразований адреса и блока памнти начальных адресов, с вторым гкодом первого элемента ИЛИ, с синхровходом второго счетчика и с входом записи регистра, восьмой выход дешифратора соединен с вторыми входами элементов И второго блока, выходы четвертой группы регистра соединены с информационными входами второго счетчика,

20

25

30

35

40

ветственно с выходом второго триггера и инверсным выходом пятого элемента И, первый и второй входы которого сЬединены соответственно с выходами первого триггера и второго элемента ИЛИ, первый и второй входы которого соединены соответственно с выходом равенства нулю второго счетчика и выходом элемента И, остальные входы третьего элемента ИЛИ соединены с выходами схем сравнения блока, выход равенства нулю счетчика, выходы третьего и четвертого элементов И и выходы схем сравнения блока объединены и соединены с вторыми входами элементов И четвертого , выход второго элемента И соединен с вычитаю- DtHM входом второго счетчика, четвертью выход блока памяти преобразований адреса соединен с четвертым входом четвертого элемента И и с третьим управляющим входом блока сопряжения, выходы регистра адреса соединены с вторыми информационными пходаьш первого, второго и третьего мультиплексоров, выход первого элемента И соединен с входом установки второго триггера.

16

с второго по шестой выходы регистра соединены с входами управления первого, второго и третьего мультиплексоров и с вторыми входами первого и второго элементов И, седьмой выход регистра соединен с первым входом четвертого элемента И и с синхровходами первого и второго регистров, информационные входы которых соединены соответственно с шинами логических нуля и единицы устройства отладки, выход признака останова которого соединен с выходом четвертого элемента И, второй и

0

5

0

5

0

ветственно с выходом второго триггера и инверсным выходом пятого элемента И, первый и второй входы которого сЬединены соответственно с выходами первого триггера и второго элемента ИЛИ, первый и второй входы которого соединены соответственно с выходом равенства нулю второго счетчика и выходом элемента И, остальные входы третьего элемента ИЛИ соединены с выходами схем сравнения блока, выход равенства нулю счетчика, выходы третьего и четвертого элементов И и выходы схем сравнения блока объединены и соединены с вторыми входами элементов И четвертого , выход второго элемента И соединен с вычитаю- DtHM входом второго счетчика, четвертью выход блока памяти преобразований адреса соединен с четвертым входом четвертого элемента И и с третьим управляющим входом блока сопряжения, выходы регистра адреса соединены с вторыми информационными пходаьш первого, второго и третьего мультиплексоров, выход первого элемента И соединен с входом установки второго триггера.

| Микропроцессоры: системы программирования и отладки | |||

| Под редакцией В.А.Мясникова, М.: ЭнергоатомИздат, 1985, с | |||

| Искусственный двухслойный мельничный жернов | 1921 |

|

SU217A1 |

| Система автоматизированного проектирования микропроцессорных устройств МЕТАМИКРО, НТК АН БССР, Минск, 1985, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-10—Подача