Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании систем отладки микропрограммных устройств.

Целью изобретения является повышение контроля пригодности устройства.

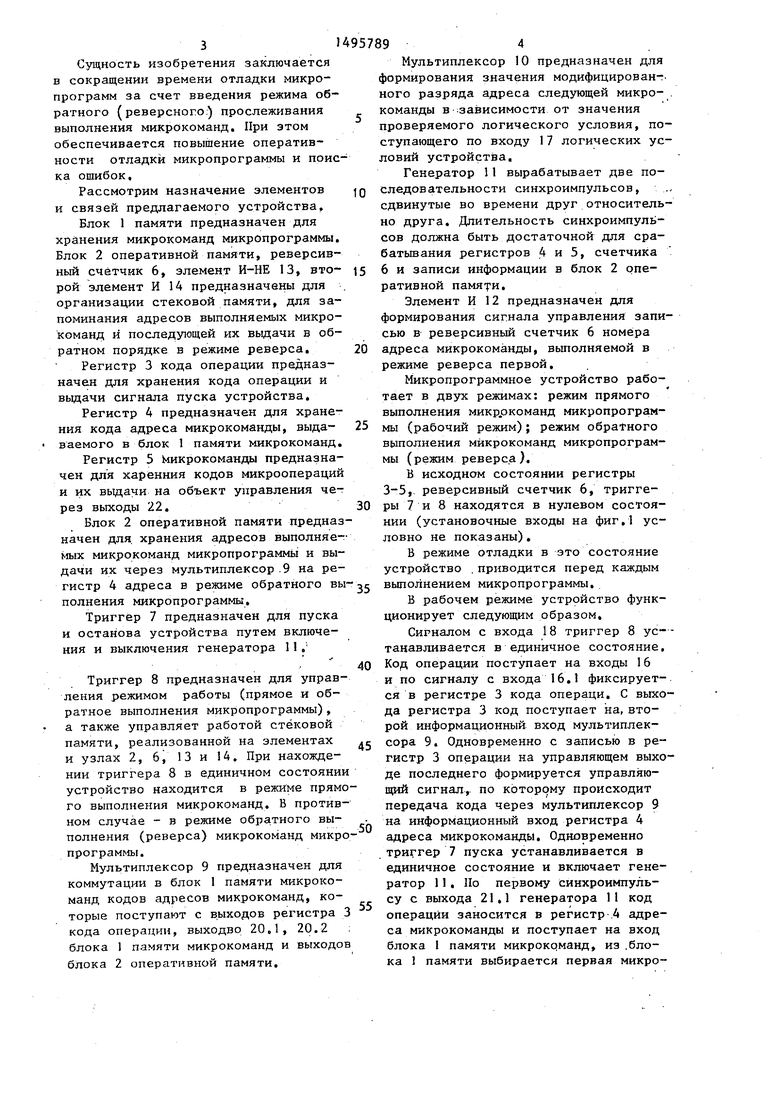

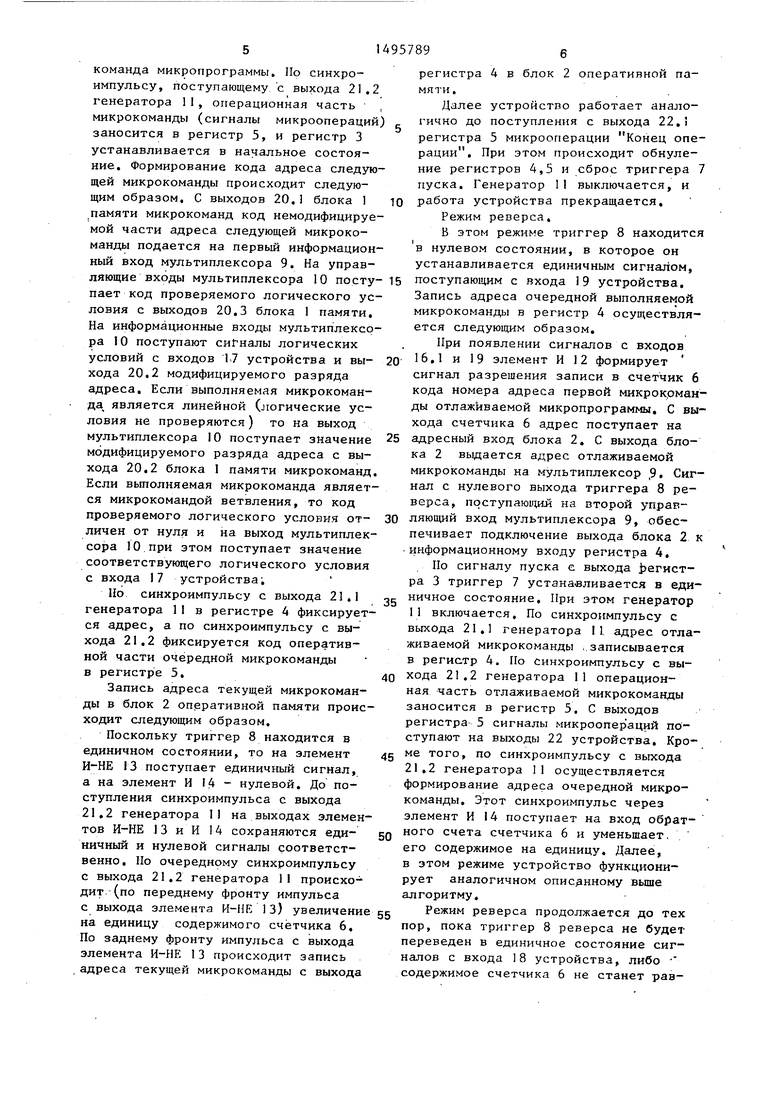

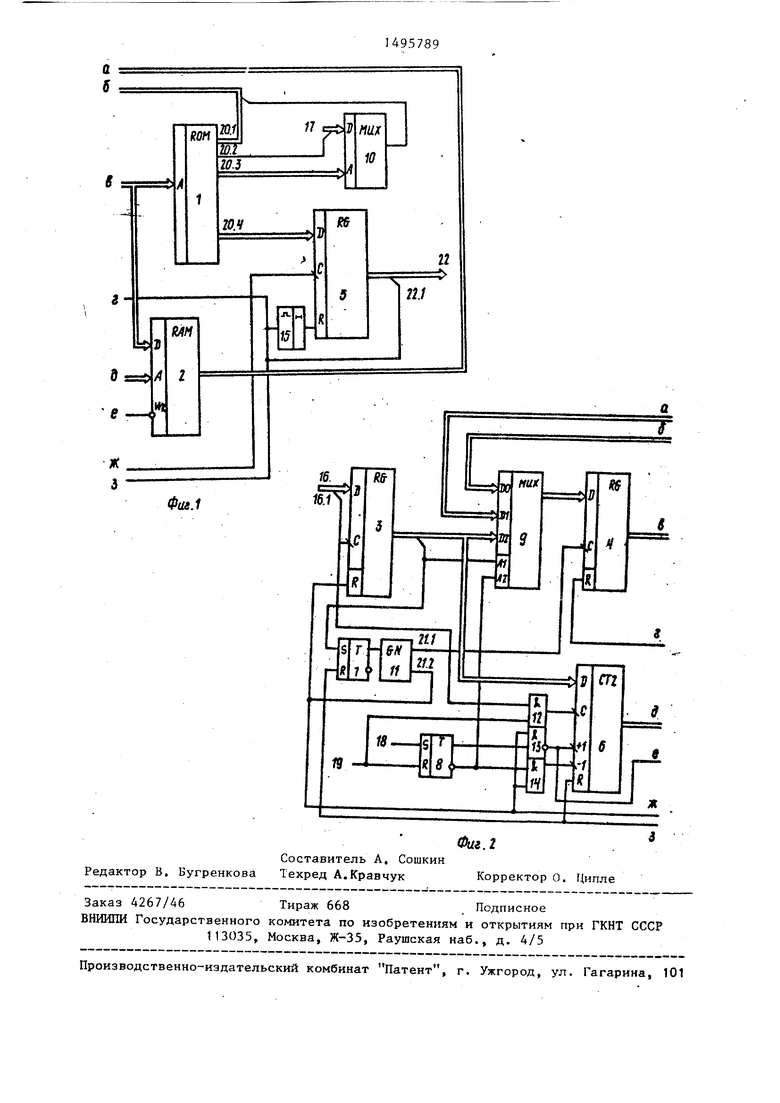

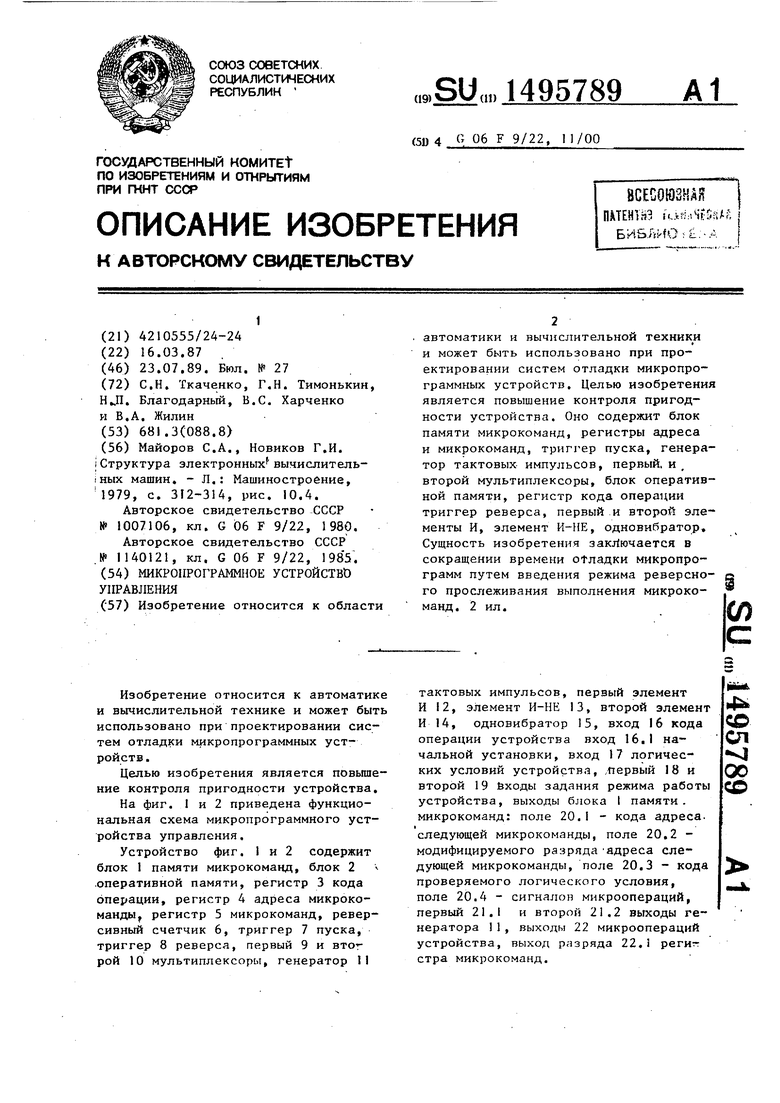

На фиг. 1 и 2 приведена функциональная схема микропрограммного устройства управления.

Устройство фиг, 1 и 2 содержит блок 1 памяти микрокоманд, блок 2 v .оперативной памяти, регистр 3 кода операции, регистр 4 адреса микроко- манды регистр 5 микрокоманд, реверсивный счетчик 6, триггер 7 пуска, триггер 8 реверса, первый 9 и втог рой 10 мультиплексоры, генератор II

тактовых импульсов, первый элемент И 12, элемент И-НЕ 13, второй элемент И 14, одновибратор 15, вход 16 кода операции устройства вход 16.1 начальной установки, вход 17 логических условий устройства, .первый 18 и второй 19 бходы задания режима работы устройства, выходы блока I памяти, микрокоманд: поле 20.1 - кода адреса, следующей микрокоманды, поле 20.2 - модифицируемого разряда адреса следующей микрокоманды, поле 20.3 - кода проверяемого логического условия, поле 20.4 - сигналов микроопераций, первый 21.1 и второй 21.2 выходы генератора 1, выходы 22 микроопераций устройства, выход разряда 22. региг: стра микрокоманд.

4 СО СП

С50 СО

Сущность изобретения заключается в сокращении времени отладки микропрограмм за счет введения режима обратного ( реверсного.) прослеживания выполнения микрокоманд. При этом обеспечивается повышение оперативности отладки микропрограммы и поиска ошибок.

Рассмотрим назначение элементов и связей предлагаемого устройства.

Блок 1 памяти предназначен для хранения микрокоманд микропрограммы. Блок 2 оперативной памяти, реверсивный счётчик 6, элемент И-НЕ 13, второй элемент И 14 предназначены для организации стековой памяти, для запоминания адресов выполняемь1х микрокоманд и последующей их выдачи в обратном порядке в режиме реверса.

Регистр 3 кода операции предназначен для хранения кода операции и вьщачи сигнала пуска устройства.

Регистр 4 предназначен для хранения кода адреса микрокоманды, выдаваемого в блок 1 памяти микрокоманд.

Регистр 5 Микрокоманды предназначен для харенния кодов микроопераций и их выдачи на объект управления через выходы 22.

Блок 2 оперативной памяти предназначен для. хранения адресов выполняемых микрокоманд микропрограммы и выдачи их через мультиплексор .9 на регистр 4 адреса в режиме обратного выполнения микропрограммы.

Триггер 7 предназначен для пуска и останова устройства путем включения и выключения генератора 11 ,

Триггер 8 предназначен для управления режимом работы (прямое и обратное выполнения микропрограммы), а также управляет работой стековой памяти, реализованной на элементах и узлах 2, 6, 13 и 14, При нахождении триггера 8 в единичном состоянии устройство находится в режиме прямого выполнения микрокоманд, В противном случае - в режиме обратного выполнения (реверса) микрокоманд микропрограммы.

Мультиплексор 9 предназначен для коммутации в блок 1 памяти микрокоманд кодов адресов микрокоманд, которые поступают с выходов регистра 3 кода операции, выходво 20,1, 20.2 блока 1 памяти микрокоманд и выходов блока 2 оперативной памяти.

0

0

5

0

5

0

5

0

5

Мультиплексор 10 предназначен для формирования значения модифицирован-. ного разряда адреса следующей микрокоманды в зависимости от значения проверяемого логического условия, поступающего по входу 17 логических условий устройст ва.

Генератор 11 вырабатывает две последовательности синхроимпульсов, сдвинутые во времени друг относительно друга. Длительность синхроимпульсов должна быть достаточной для срабатывания регистров 4 и 5, счетчика 6 и записи информации в блок 2 оперативной памяти.

Элемент И 12 предназначен для формирования сиг.нала управления записью в реверсивный счетчик 6 номера адреса микрокоманды, вьшолняемой в режиме реверса первой,

М икропрограммное устройство работает в двух режимах: режим прямого выполнения микрркоманд микропрограммы (рабочий режим); режим обратного выполнения микрокоманд микропрограммы (режим реверса),

В исходном состоянии регистры 3-5,. реверсивный счетчик 6, триггеры 7 и 8 находятся в нулевом состоянии (установочные входы на фиг,1 условно не показаны),

В режиме отладки в это состояние устройство .приводится перед каждым выполнением микропрограммы,.

В рабочем режиме устройство функционирует следующим образом.

Сигналом с входа 18 триггер 8 ус- танавливается в единичное состояние. Код операции поступает на входы 16 и по сигналу с входа 16,1 фиксируется в регистре 3 кода операци, С выхода регистра 3 код поступает на, второй информационный вход мультиплексора 9. Одновременно с записью в регистр 3 операции на управляющем выходе последнего формируется управляющий сигнал,, по которому происходит передача кода через мультиплексор 9 на информационный вход регистра 4 адреса микрокоманды. Одновременно триггер 7 пуска устанавливается в единичное состояние и включает генератор П, По первому Синхроимпульсу с выхода 21,1 генератора 11 код операции заносится в регистр-.4 адреса микрокоманды и поступает на вход блока 1 памяти микрокоманд, из .блока 1 памяти выбирается первая микро

команда микропрограммы. По синхроимпульсу, поступающему с выхода 21,2 генератора 11, операционная часть микрокоманды (сигналы микроопераций заносится в регистр 5, и регистр 3 устанавливается в начальное состояние. Формирование крда адреса следующей микрокоманды происходит следующим образом, С выходов 20,1 блока 1 памяти микрокоманд код немодифицируемой части адреса следующей микроко- мандь подается на первый информационный вход мультиплексора 9, На управляющие входы мультиплексора 10 посту пает код проверяемого логического условия с выходов 20,3 блока 1 памяти. На информационные входы мультиплексора 10 поступают сигналы логических условий с входов 17 устройства и выхода 20,2 модифицируемого разряда адреса. Если выполняемая микрокоманда, является линейной (логические условия не проверяются) то на выход мультиплексора 10 поступает значение модифицируемого разряда адреса с выхода 20,2 блока 1 памяти микрокоманд Если выполняемая микрокоманда является микрокомандой ветвления, то код проверяемого логического условия отличен от нуля и на выход мультиплексора 10.при этом поступает значение соответствующего логического условия с входа 17 устройства;

По синхроимпульсу с выхода 21.1 генератора 1I в регистре 4 фиксируется адрес, а по синхроимпульсу с выхода 21,2 фиксируется код оперативной части очередной микрокоманды в регистре 5,

Запись адреса текущей микрокоманды в блок 2 оперативной памяти происходит следующим образом.

Поскольку триггер 8 находится в единичном состоянии, то на элемент И-НЕ 13 поступает единичный сигнал, а на элемент И 14 нулевой. До поступления синхроимпульса с выхода 21,2 генератора II на выходах элементов И-НЕ 13 и И 14 сохраняются единичный и нулевой сигналы соответственно. Но очередному синхроимпульсу с выхода 21,2 генератора II происходит (по переднему фронту импульса с выхода элемента И-НЕ 13) увеличение на единицу содержимого счётчика 6, По заднему фронту импульса с выхода элемента И-НЕ 13 происходит запись адреса текущей микрокоманды с выхода

0

25

Ю 15

5

0

5

0

5

0

регистра 4 в блок 2 оперативной памяти.

Далее устройство работает аналогично до поступления с выхода 22,1 регистра 5 микрооперации Конец операции. При этом происходит обнуление регистров 4,5 и сброс триггера 7 пуска. Генератор 11 выключается, и работа устройства прекращается.

Режим реверса,

В этом режиме триггер 8 находится в нулевом состоянии, в которое он устанавливается единичным сигналом, поступающим с входа 19 устройства. Запись адреса очередной выполняемой микрокоманды в регистр 4 осуществляется следующим образом.

При появлении сигналов с входов 16,1 и 19 элемент И 12 формирует сигнал разрешения записи в счетчик 6 кода номера адреса первой микрокрман- ды отлаживаемой микропрограммы, С выхода счетчика 6 адрес поступает на адресный вход блока 2, С выхода блока 2 выдается адрес отлаживаемой микрокоманды на мультиплексор ,9, Сигнал с нулевого выхода триггера 8 реверса, поступающий на второй управляющий вход мультиплексора 9, обеспечивает подключение выхода блока 2 к информационному входу регистра 4.

По сигналу пуска е выхода 1 егист- ра 3 триггер 7 устанавливается в единичное состояние. При этом генератор 11 включается. По синхроимпульсу с выхода 21,1 генератора II. адрес отлаживаемой микрокоманды ,, записывается в регистр 4. По синхроимпульсу с выхода 21,2 генератора 11 операционная часть отлаживаемой микрокоманды заносится в регистр 5, С выходов регистра- 5 сигналы микроопер аций поступают на выходы 22 устройства. Кроме того, по синхроимпульсу с выхода 21,2 генератора II осуществляется формирование адреса очередной микрокоманды. Этот синхроимпульс через элемент И 14 поступает на вход обратного счета счетчика 6 и уменьшает, его содержимое на единицу. Далее, в этом режиме устройство функционирует аналогичном описанному выше алгоритму.

Режим реверса продолжается до тех пор, пока триггер В реверса не будет переведен в единичное состояние сигналов с входа 18 устройства, либо содержимое счетчика 6 не станет равным нулю, в последнем случае по нулевому адресу будет выбрана из блока 1 памяти микрооперация Конец операции. При этом сигналом с выхода 22,1 регистра 5 регистры 4,5, счет-, чик 6 и триггер 7 установятся в нулевое состояние, и выключится генератор 11, Работа устройства прекращается.

Формула изобретения

Микропрограммное устройство управления, содержап1ее блок памяти микро- команд, регистры адреса и микрокоманд, триггер пуска, генератор такто- .вых импульсов, первый и второй мультиплексоры, причем выход регистра адреса соединен с адресным входом блока памяти микрокоманд старшие разряды поля адреса выхода которого соединены со старшими разрядами первого информационного входа первого мультиплексора, выход поля логичес- ких условий блока памяти микрокоманд соединен с адресным .входом второго мультиплексора, выход поля микрокоманд блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, выход которого является выходом микроопераций устройства, младший разряд поля адреса выхода блока памяти микрокоманд и входы логи 1еских условий устройства соедине- ны соответственно с младшим разрядом и старшими разрядами информационного входа второго мультиплексора, выход которого соединен с младшим разрядо первого информационного входа йерво- го мультиплексора, выход признака Конец операции регистра микрокоманды соединен с входом установки в О триггера пуска, прямой выход триггера пуска соединен с входом запуска генератора тактовых импульсов, выход первого мультиплексора соединен с информационным входом регистра адреса, первый и второй выходы генератора тактовых импульсов соединены соответственно с входом синхронизации регистра адреса и регистра микроко-. манд, отличающееся тем, что, с целью повышения контроля пригодности устройства, оно дополнитель но содержит регистр кода операции, блок оперативной памяти, реверсивный

0 5 0 5 о д е

0

счетчик, триггер реверса, одновибра- тор, первый и второй элементы И, элемент И-НЕ, причем вход кода операций устройства соединен с информационным входом регистра кода операции, вход начальной установки устройства соединен с входом синхронизации регистра кода операции и с первым входом первого элемента И, выход регистра кода операции соединен с вторым информационным входом первого мультиплексора и информационным входом реверсивного счетчика, выход признака разряда запуска регистра кода операции соединен с первым адресным входом первого мультиплексора и с входом установки в 1 триггера пуска, выход регистра адреса соедиен с информационным входом блока оперативной памяти, выход которого соединен с информационным входом перво- го мультиплексора, первый задания режима работы устройства соединен с входом установки в 1 триггера реверса, второй вход задания режима работы устройства соединен с входом установки в О триггера реверса и вторым входом первого элемента И, выход которого соединен с входом записи реверсивного счетчика, прямой выход триггера реверса соединен с первым входом элемента И-НЕ, инверсный выход триггера реверса соединен с первым входом второго элемента И и с вторым адресным входом первого мультиплексора, выход элемента И-НЕ соединен с входом разрешения прямого счета реверсивного счетчика НС входом записи блока оперативной; памяти, выход второго элемента И сбе- динен с входом разрешения обратного счета реверсивного счетчика, второй выход генератора тактовых импульсрв соединен с вторьщи входами элемента И-НЕ, второго элемента И и с входом установки в О рег истра кода операции, информационный выход реверсивного счетчика соединен с адресным входом блока оперативной памяти, выход признака Конец операции регистра микрокоманд соединен с входами установки в О регистра адреса, реверсивного счетчика и с входом одновиб- ратора, выход которого соединен с входом установки в О регистра микрокоманды.

а 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Динамическое микропрограммное устройство для контроля и управления | 1984 |

|

SU1226454A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при проектировании систем отладки микропрограммных устройств. Целью изобретения является повышение контроля пригодности устройства. Оно содержит блок памяти микрокоманд, регистры адреса и микрокоманд, триггер пуска, генератор тактовых импульсов, первый и второй мультиплексоры, блок оперативной памяти, регистр кода операции, триггер реверса, первый и второй элементы И, элемент И-НЕ, одновибратор. Сущность изобретения заключается в сокращении времени отладки микропрограмм путем введения режима реверсного прослеживания выполнения микрокоманд. 2 ил.

tf r

IKOH

JW

гН

MM

Л. 15

ж

3

Фаг.1

Фиг.2

Составитель A, Сошкин Редактор В, Бугренкова Техред А.Кравчук Корректор О. Ципле

Заказ 4267/46Тираж 668Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

f1U)( 10

22J

| Майоров С.А., Новиков Г.И | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| - Л.: Машиностроение, 1979, с | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1007106A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-03-16—Подача