Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных комплексов.

Цель изобретения - расширение области применения устройства за счет перераспределения заданий.

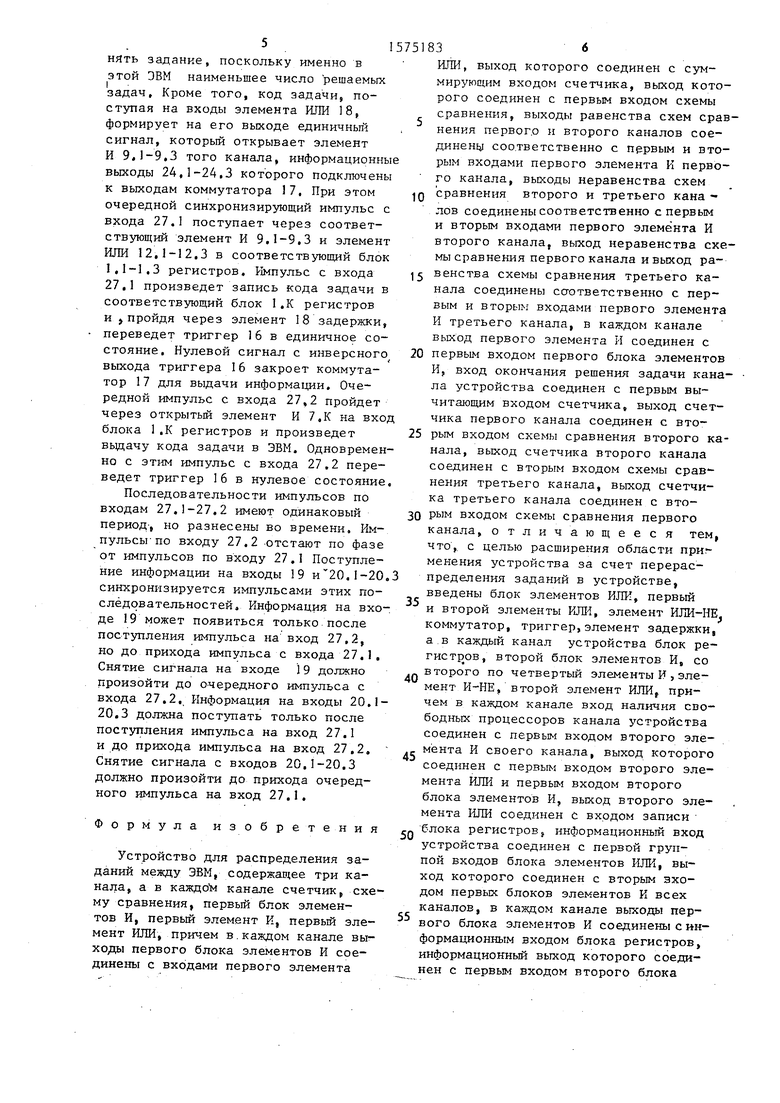

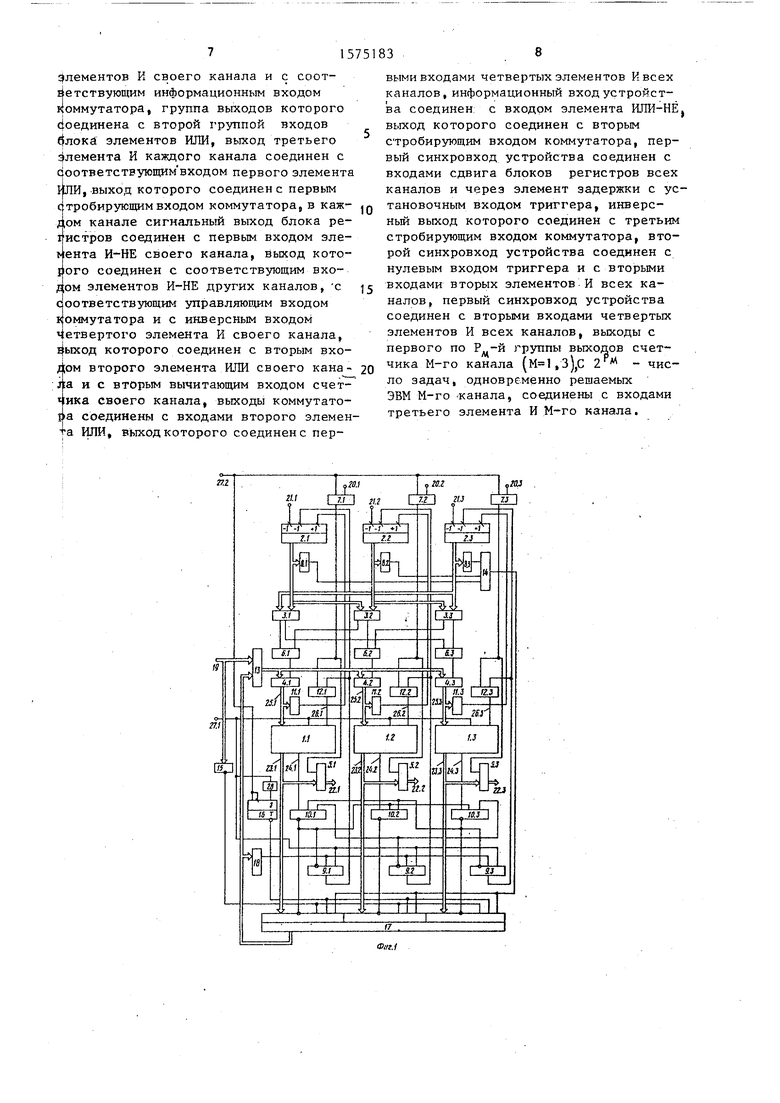

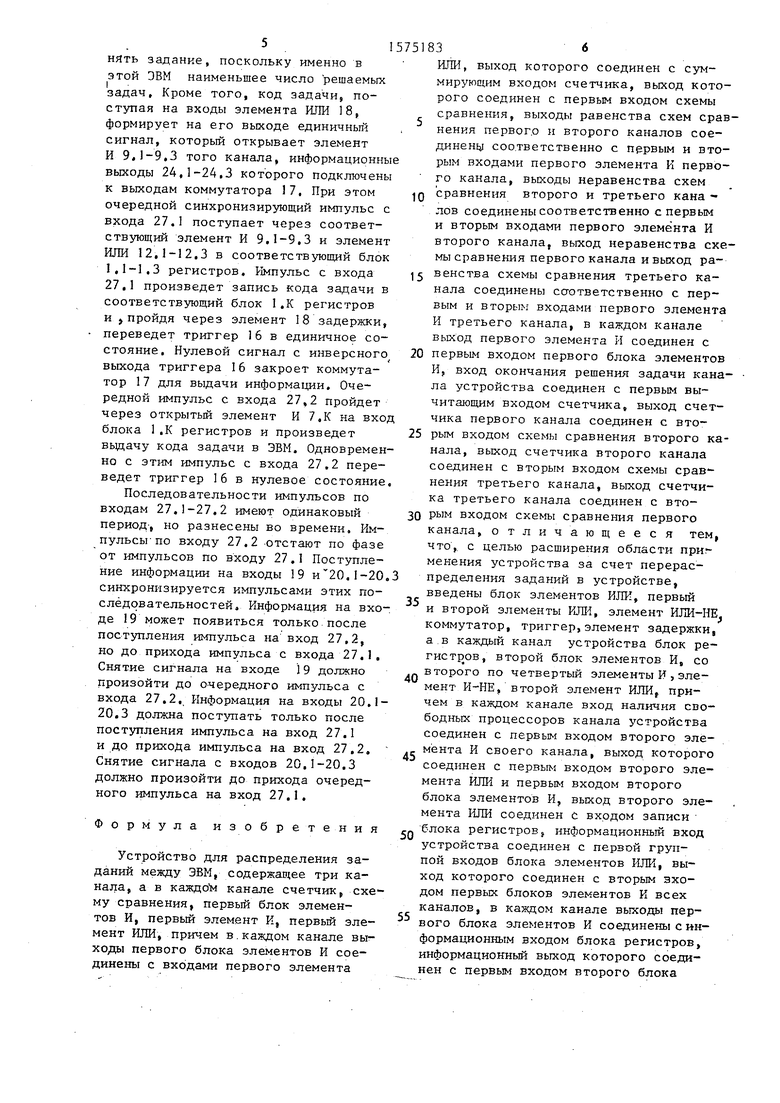

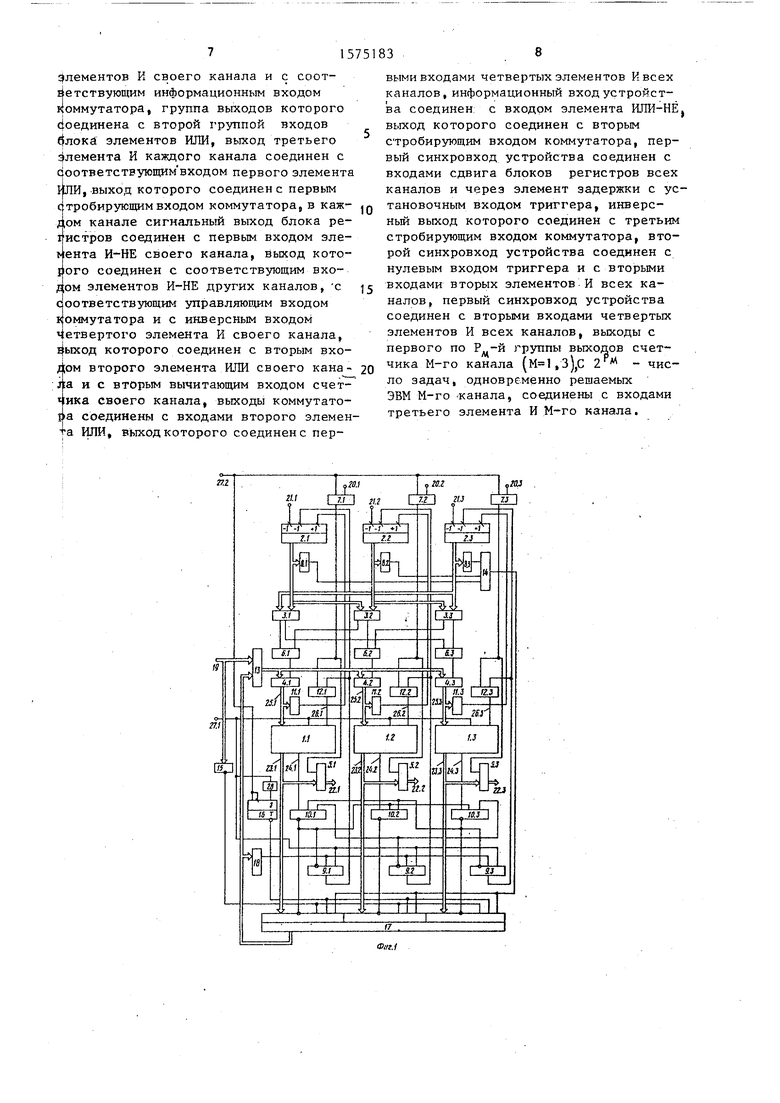

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока регистров.

Устройство Для распределения заданий ЭВМ содержит три канала и в каждом К-м канале блок 1.К регистров, счетчик 2 , схему сравнения З.К блоки элементов И 4.К-9.К, элемент И-НЕ 10.К, элемент ИЛИ 11.К-12.К, : а также общие для всего устрой-.

ства блок 13 элементов ИЛИ элемент ИЛИ 14, элемент ШТК-КЕ 15, триггер 16, коммутатор 17, элемент ИЛИ 18, а также информационный вход 19 устройства, входы 20.1-20.3 наличия свободных ЭВМ, входы окончания решения задачи 21.1-21.3, информационные выходы каналов 22.1-22.3, информационные выходы блоков 23,1-23.3 регистров, сигнальные выходы блоков 24.1-24.3 регистров, информационные входы блоков 25s1-25 о 3 регистров, входы записи блоков регистров ИЛИ 26.1- 26.3, синхровходы устройства 27.1- 27.2 элемент. 28 задержки.

Блок 1.1-1.3 регистров (фиг.2) содержит регистры 29, блоки 30 элементов ИЛИ, элементы И 31-33.

сд сд

00

оо

315

Устройство работает следующим образом.

В исходном состоянии все ЭВМ свободны и находятся в работоспособном состоянии. Счетчики 2,1-2.3, блоки 1.1-1.3 регистров находятся в нулевом состоянии. Входы начальной установки на чертежах условно не показаны, Равенство содержимого счетчиков Ј.1- 2,3 обуславливает выдачу с первых выходов схем 3,1-3.3 сравнения разрешающих сигналов, поступающих через элемент И 6,1 на управляющий вход блока 4,1 элементов И. На управляющие входы блоков элементов И 4,2-4.3 разрешающие сигналы не подаются, следовательно первый пришедший на информационный вход 19 код задачи, через бло 13 элементов ИЛИ и блок 4.1 элементов И поступает на входы 25.1 блока 1 .1 регистров,

Код задачи по синхронизирующему импульсу с входа 27.1 записывается в блок 1.1 регистров (в регистр 29,1), Как только при передаче кода задачи срабатывает блок 4,1 элементов К на выходе элемента ИЛИ 11,1 появляется единичный сигнал, по заднему фронту которого содержимое счетчика 2.1 увеличивается на единицу. Поскольку ЭВМ все свободны, то на сигнальном входе 20.1 присутствует единичный сигнал.

Синхронизирующий импульс с входа

27,2 поступает через открытый эле

мент И 7.1 и элемент ИЛИ 12.1 в блок 1, регистров и на управляющий вход блока элементов И 5,1 для выдачи кода задачи непосредственно в ЭВМ. При поступлении второй задачи она направляется во вторую ЭВМ, аналогичным образом, поскольку с первого выхода схемы 3.3 сравнения и второго выхода схемы 3.2 сравнения подаются разрешающие сигналы на элемент И 6.2 и далее на управляющий вход блока элементов И 4,2, Таким образом, очередная поступившая на вход 19 устройства задача направляется в ту ЭВМ, число решаемых задач в которой минимально. В случае равенства числа решаемых задач задана поступает в ЭВМ с минимальным порядковым номером, что обеспечивает равномерную загрузку всех ЭВМ.

По окончании решения задачи на вычитающие входы 21.1-21„3 счетчиков 2.1-2,3 соответственно поступает сигнал, который уменьшает содержимое

-1 ,„

5

0

0

35

40

50

55

834

того или иного счетчика на единицу. При записи очередной поступившей задачи в блок 1.1-1.3 регистров при невозможности ЭВМ обработать ее задача хранится в блоке 1,1-1.3 регистров до тех пор, пока ЭВМ не сможет принять ее на обслуживание. Тогда на соответствующем входе 20.1-20.3 появляется единичный сигнал и очередной синхронизирующий импульс с входа 27.2 поступает через элемент И 7.1-7.3 на вход соответствующего блока 1,1-1,3 регистров и на управляющий вход блока 5.1- 5.3 элементов И соответственно.

В связи с тем, что время обслуживания различных задач может существенно отличаться,- возможны случаи, когда одна из ЭВМ может принять задание на обслуживание, а в другой -есть задачи, ожидающие в очереди на обслуживание,,

Рассмотрим работу устройства в этом режиме.

Как только какая-либо ЭВМ может принять задачу на обслуживание, на выходе соответствующего элемента И 8,1-8,3 появится единичный сигнал, . который через элемент ИЛИ 14 поступает на один из управляющих входов коммутатора 17, При наличии в каком-либо блоке 11-1.3 регистров задачи, которая еще не поступила в ЭВМ для обслуживания на выходе 24.1-24.3 соответствующего блока 1.1-1,3 регистров формируется единичный сигнал. Этот сигнал поступает на вход соответствующего элемента И-НЕ; 10..1-10.3.

С выхода этого элемента нулевой сигнал поступает- на входы двух других элементов И-НЕ 10,1-10.3 запрещая тем самым фррмирование нулевого сигнала.

Нулевой сигнал поступает на инверсный вход коммутатора 17, Таким образом, при отсутствии в данный момент кода задачи на входе устройства 19, о чем свидетельствует единичный сигнал с выхода элемента ИЛЙ-НЕ 15, для одного из информационных выходов 23,1- 23,3 блоков 1 о 1-1.3 регистров коммутатор 17 является открытым.

Код задачи с соответствующего выхода 23.1-23,3 блока 1,1-1.3 регистров поступает на входы блока элементов ИЛИ 13. Далее с выхода блока элементов ИЛИ 13 код задачи поступает непосредственно . в блок 1,1-1.3 регистров . той ЭВМ, которая может вылол51

нять задание, поскольку именно в этой ЭВМ наименьшее число решаемых задач. Кроме того, код задачи, поступая на входы элемента ИЛИ 18, формирует на его выходе единичный сигнал, который открывает элемент И 9.1-9.3 того канала, информационны выходы 24,1-24,3 которого подключены к выходам коммутатора 17, При этом очередной синхронизирующий импульс с входа 27.1 поступает через соответствующий элемент И 9.1-9.3 и элемент ИЛИ 12,1-12.3 в соответствующий блок 1,1-1.3 регистров. Импульс с входа 27.1 произведет запись кода задачи в соответствующий блок 1.К регистров и t пройдя через элемент 18 задержки, переведет триггер 16 в единичное состояние. Нулевой сигнал с инверсного выхода триггера 16 закроет коммутатор 17 для выдачи информации. Очередной импульс с входа 27,2 пройдет через открытый элемент И 7.К на вход блока 1,К регистров и произведет выдачу кода задачи в ЭВМ. Одновременно с этим импульс с входа 27.2 переведет триггер 16 в нулевое состояние

Последовательности импульсов по входам 27.1-27.2 имеют одинаковый

период, но разнесены во времени. Импульсы по входу 27.2 отстают по фазе от импульсов по входу 27.1 Поступление информации на входы 19 ,1-20 синхронизируется импульсами этих последовательностей. Информация на входе 19 может появиться только после поступления импульса на вход 27.2, но до прихода импульса с входа 27.1, Снятие сигнала на входе 19 должно произойти до очередного импульса с входа 27.2. Информация на входы 20.1 20.3 должна поступать только после поступления импульса на вход 27.1 и до прихода импульса на вход 27.2. Снятие сигнала с входов 20,1-20,3 должно произойти до прихода очередного импульса на вход 27.1.

Формула изобретения

Устройство для распределения заданий между ЭВМ, содержащее три канала, а в каждо м канале счетчик, схему сравнения, первый блок элементов И, первый элемент И, первый элемент ИЛИ, причем в каждом канале выходы первого блока элементов И соединены с входами первого элемента

б

0

5

0

5

83

ИЛИ, выход которого соединен с суммирующим входом счетчика, выход которого соединен с первым входом схемы сравнения, выходы равенства схем сравнения первого и второго каналов сое- динену соответственно с первым и вторым входами первого элемента К первого канала, выходы неравенства схем сравнения второго и третьего кана - лов соединены соответственно с первым и вторым входами первого элемента И второго канала, выход неравенства схемы сравнения первого канала и выход равенства схемы сравнения третьего канала соединены саответственно с первым и вторые входами первого элемента И третьего канала, в каждом канале выход первого элемента И соединен с первым входом первого блока элементов И, вход окончания решения задачи канала устройства соединен с первым вычитающим входом счетчика, выход счетчика первого канала соединен с вторым входом схемы сравнения второго канала, выход счетчика второго канала соединен с вторым входом схемы сравнения третьего канала, выход счетчика третьего канала соединен с вто- 0 рым входом схемы сравнения первого канала, отличающееся тем, что, с целью расширения области применения устройства за счет перераспределения заданий в устройстве, введены блок элементов ИЛИ, первый и второй элементы ИЛИ, элемент ИЛИ-НЕ, коммутатор, триггер,элемент задержки, а в каждый канал устройства блок ре- гистр в, второй блок элементов И, со второго по четвертый элементы И,элемент И-НЕ, второй элемент ИЛИ{ причем в каждом канале вход наличия свободных процессоров канала устройства соединен с первым входом второго элемента И своего канала, выход которого соединен с первым входом второго элемента ИЛИ и первым входом второго блока элементов И, выход второго элемента ИЛИ соединен с входом записи блока регистров, информационный вход устройства соединен с первой группой входов блока элементов ИЛИ, выход которого соединен с вторым эхо- дом первых блоков элементов И всех

5

0

5

0

каналов, в каждом канале выходы первого блока элементов И соединены с информационным входом блока регистров, информационный выход которого соединен с первым входом второго блока

элементов К своего канала и с соотЗетствующим информационным входом оммутатора, группа выходов которого соединена с второй группой входов Йлока элементов ИЛИ, выход третьего Элемента И каждого канала соединен с аоответствующим входом первого элемента ИЛИ, выход которого соединен с первым с|тробирующимвходом коммутатора, в каж- Дом канале сигнальный выход блока ре- ifHCTpoB соединен с первым входом эле- 4ента И-НЕ своего канала, выход которого соединен с соответствующим входом элементов И-НЕ других каналов, с соответствующим управляющим входом коммутатора и с инверсным входом Четвертого элемента И своего канала, ёыход которого соединен с вторым вхо- Дом второго элемента ИЛИ своего кана- да и с вторым вычитающим входом счет- Цика своего канала, выходы коммутато4

ta ИЛИ, выход которого соединен с пера соединены с входами второго элеменвыми входами четвертых элементов И всех каналов, информационный вход устройства соединен с входом элемента ИЛИ-НЁ выход которого соединен с вторым с тробирующим входом коммутатора, первый синхровход устройства соединен с входами сдвига блоков регистров всех каналов и через элемент задержки с установочным входом триггера, инверсный выход которого соединен с третьим стробирующим входом коммутатора, второй синхровход устройства соединен с нулевым входом триггера и с вторыми входами вторых элементов И всех каналов, первый синхровход устройства соединен с вторыми входами четвертых элементов И всех каналов, выходы с первого по Р„-й группы выходов счетчика М-го канала (,3)С 2м - число задач, одновременно решаемых ЭВМ М-го -канала, соединены с входами третьего элемента И М-го канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для контроля и испытаний блоков памяти бортовых ЭВМ | 1984 |

|

SU1182526A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для распределения заданий между ЭВМ | 1985 |

|

SU1282129A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Устройство для имитации объекта контроля | 1984 |

|

SU1188743A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1277111A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1508218A1 |

| Устройство для обмена информацией | 1989 |

|

SU1695316A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных комплексов. Цель изобретения - расширение области применения устройства за счет перераспределения заданий. Устройство для распределения заданий между ЭВМ содержит три канала, а в каждом канале счетчик, схему сравнения, блок регистров, два блока элементов И, четыре элемента И, элемент И-НЕ, два элемента ИЛИ. Кроме того, устройство содержит блок элементов ИЛИ, два элемента ИЛИ, элемент ИЛИ-НЕ, коммутатор, триггер, элемент задержки. Если число заданий, ожидающих обслуживания в одной из ЭВМ, превысило некоторую критическую величину, то задание из очереди к этой вычислительной машине перераспределяется в очередь к ЭВМ, имеющей минимальное число ожидающих заданий. 2 ил.

Фт.1

г

i

i i

I I

Составитель К.Сорочан Редактор Ю.Середа Техред Л. Сердюкова Корректор Т,Палий

Заказ 1785

Тираж 575

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

f.fff.Z,f.3J

Ш

Фиг. 2

Подписное

| Устройство для управления вычислительным комплексом | 1979 |

|

SU857993A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-04-11—Подача