Изобретение относится к вычисли. тельной технике и может быть использовано в многопроцессорных вычислительных системах для распределения заданий между процессорами.

Цель изобретения - повышение надежности за счет выполнения задач даже при отказе выполнявших их процессоров.

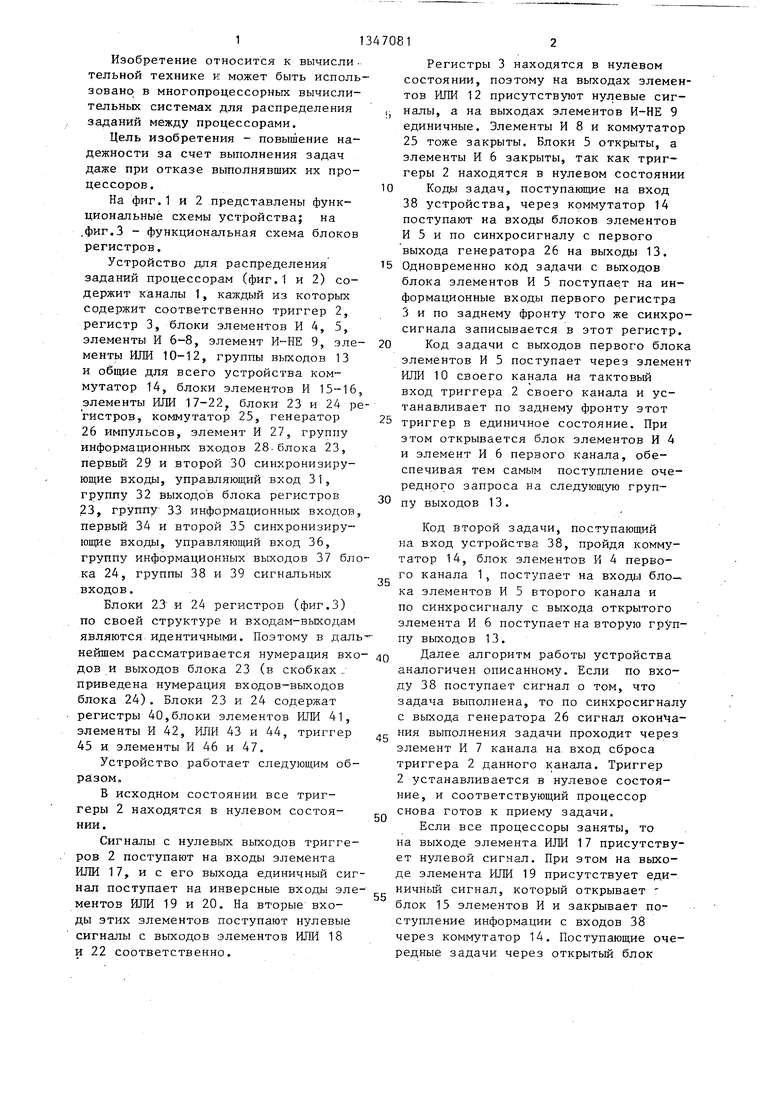

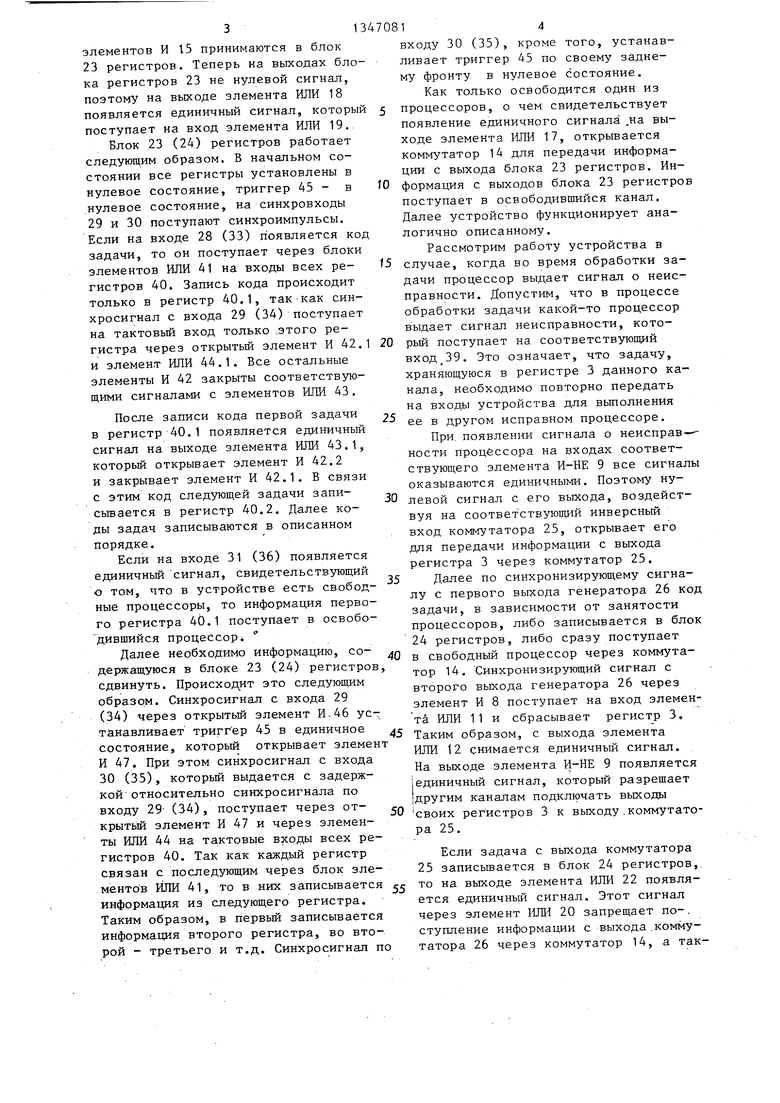

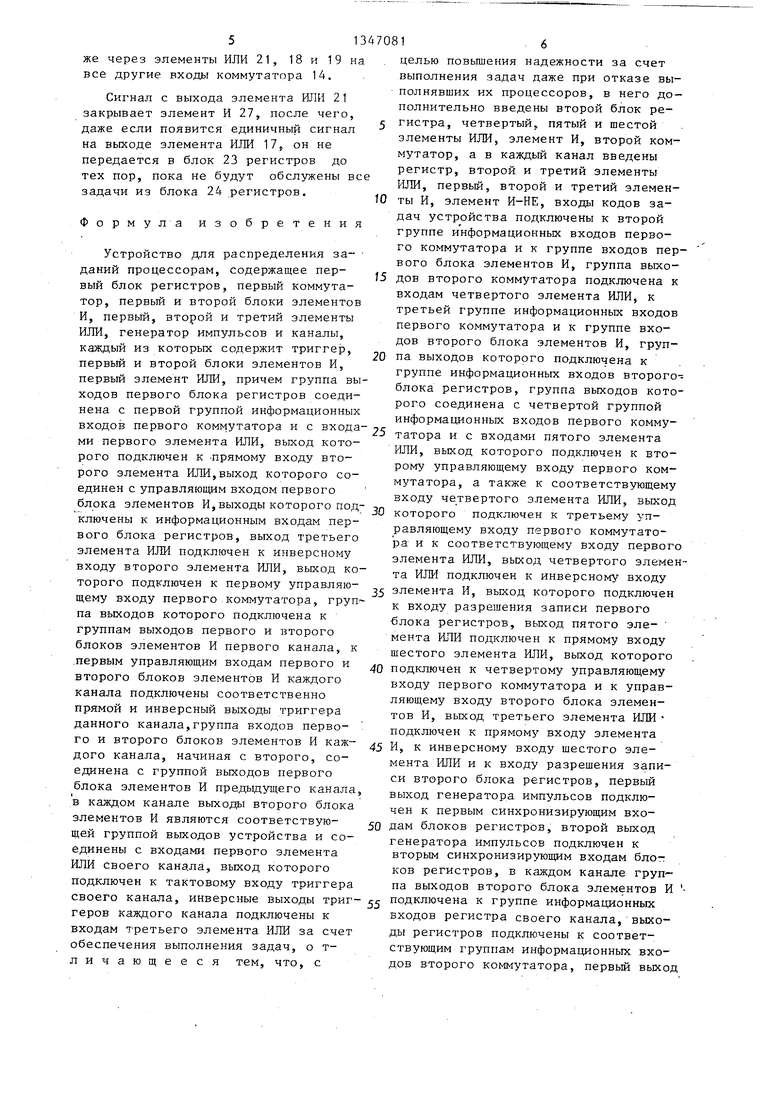

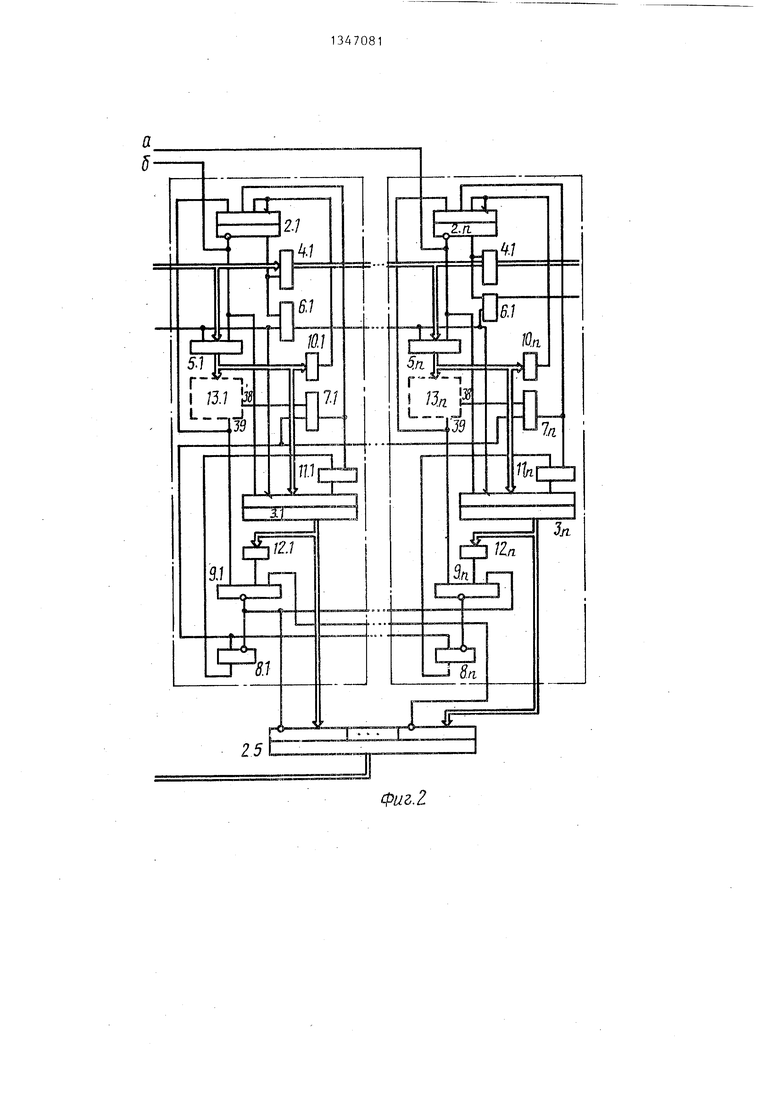

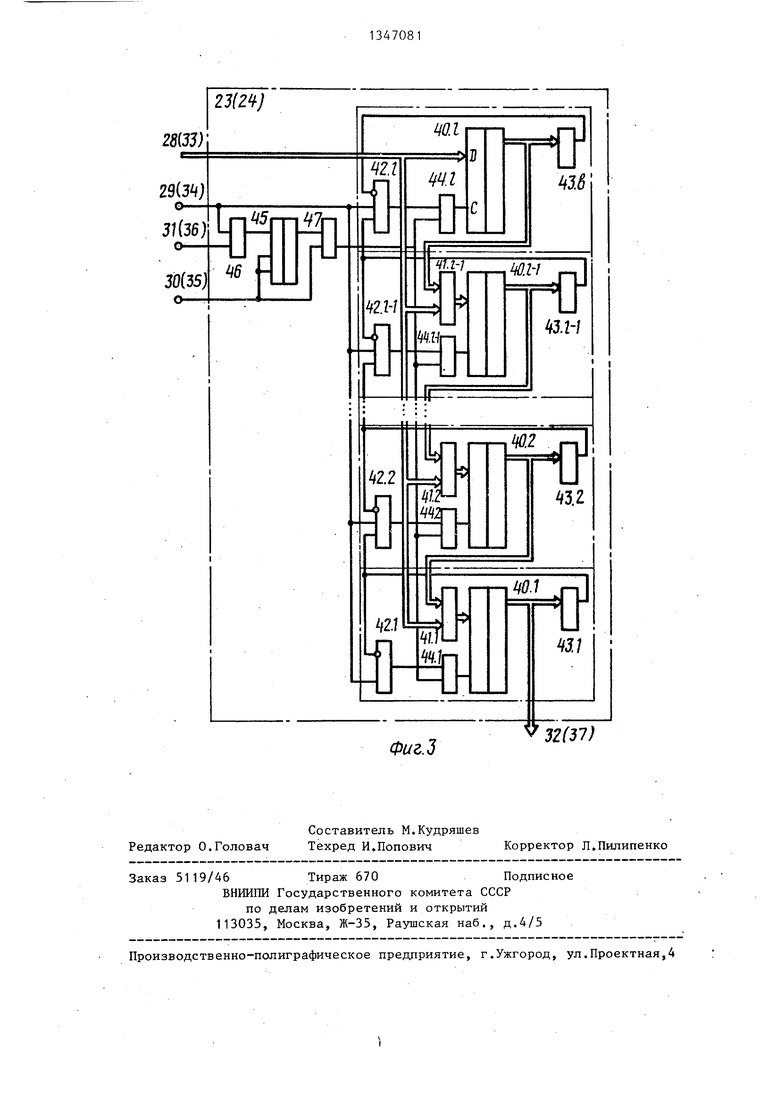

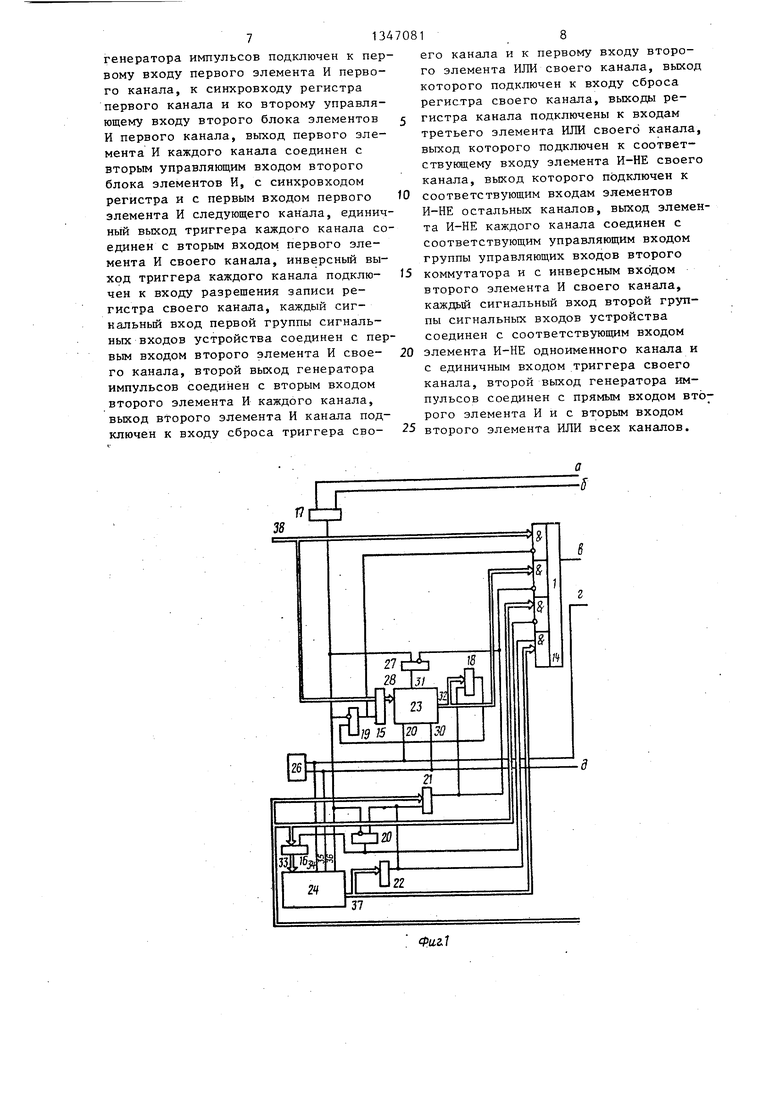

На фиг.1 и 2 представлены функциональные схемы устройства; на .фиг.З - функциональная схема блоков регистров.

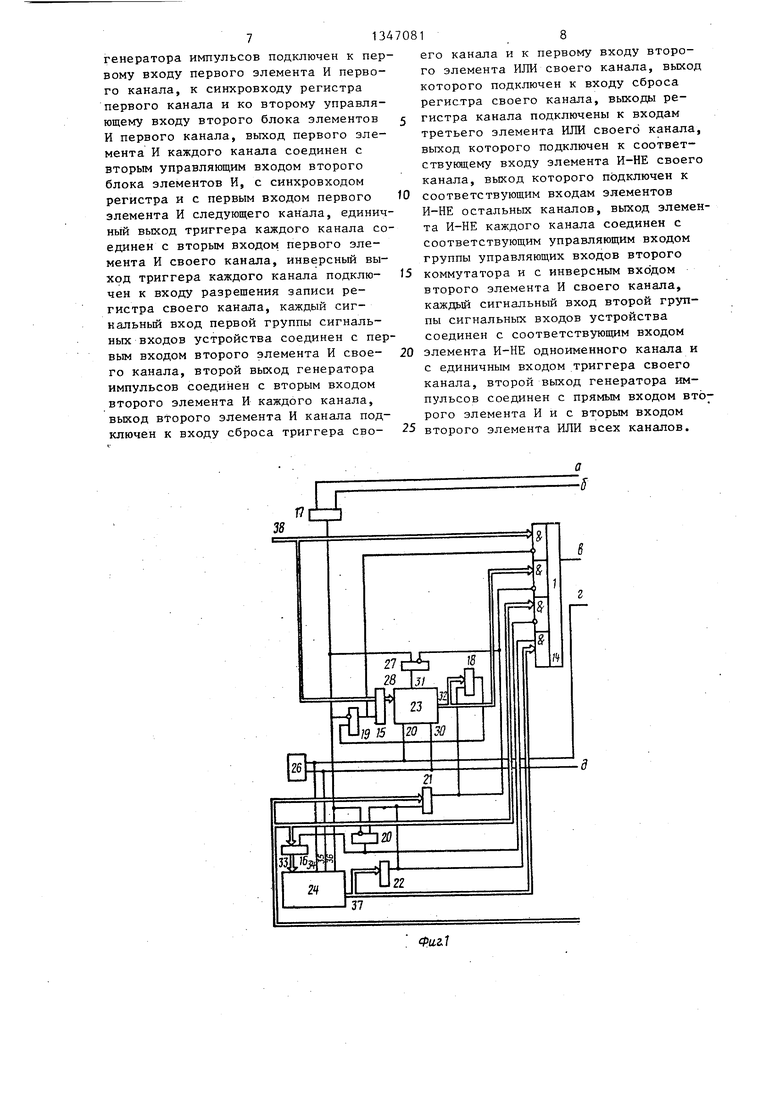

Устройство для распределения заданий процессорам (фиг. 1 и 2) содержит каналы 1, каждый из которых содержит соответственно триггер 2, регистр 3, блоки элементов И 4, 5, элементы И 6-8, элемент И-НЕ 9, элементы ИЛИ 10-12, группы выходов 13 и общие для всего устройства коммутатор 14, блоки элементов И 15-16 элементы ИЛИ 17-22, блоки 23 и 24 ргистров, коммутатор 25, генератор 26 импульсов, элемент И 27, группу информационных входов 28-блока 23, первый 29 и второй 30 синхронизирующие входы, управляющий вход 31, группу 32 выходов блока регистров 23, группу 33 информационных входов первый 34 и второй 35 синхронизирующие входы, управляющий вход 36, группу информационных выходов 37 блка 24, группы 38 и 39 сигнальных входов.

Блоки 23 и 24 регистров (фиг.З) по своей структуре и входам-выходам являются идентичными. Поэтому в дал нейшем рассматривается нумерация входов и выходов блока 23 (в скобках .. приведена нумерация входов-выходов блока 24). Блоки 23 и 24 содержат регистры 40,блоки элементов ИЛИ 41, элементы И 42, ИЛИ 43 и 44, триггер 45 и элементы И 46 и 47.

Устройство работает следующим образом

В исходном состоянии все триггеры 2 находятся в нулевом состоянии.

Сигналы с нулевых выходов триггеров 2 поступают на входы элемента ИЛИ 17, и с его выхода единичный сигнал поступает на инверсные входы элементов ИЛИ 19 и 20. На вторые входы этих элементов поступают нулевые сигналы с выходов элементов ИЛИ 18 и 22 соответственно.

5

Регистры 3 находятся в нулевом состоянии, поэтому на выходах элементов ИЛИ 12 присутствуют нулевые сиг- ij налы, а на выходах элементов И-НЕ 9 единичные. Элементы И 8 и коммутатор 25 тоже закрыты. Блоки 5 открыты, а элементы И 6 закрыты, так как триггеры 2 находятся в нулевом состоянии

0 Коды задач, поступающие на вход 38 устройства, через коммутатор 14 поступают на входы блоков элементов И 5 и по синхросигналу с первого выхода генератора 26 на выходы 13.

5 Одновременно кйд задачи с выходов блока элементов И 5 поступае.т на информационные входы первого регистра 3 и по заднему фронту того же синхросигнала записывается в этот регистр.

0 Код задачи с выходов первого блока элементов И 5 поступает через элемент ИЛИ 10 своего канала на тактовый вход триггера 2 своего канала и устанавливает по заднему фронту этот триггер в единичное состояние. При этом открывается блок элементов И 4 и элемент И 6 первого канала, обеспечивая тем самым поступление очередного запроса на следующую груп0 пу выходов 13.

Код второй задачи, поступающий на вход устройства 38, пройдя коммутатор 14, блок элементов И 4 первого канала 1, поступает на входы блока элементов И 5 второго канала и по синхросигналу с выхода открытого элемента И 6 поступает на вторую группу выходов 13.

Далее алгоритм работы устройства аналогичен описанному. Если по входу 38 поступает сигнал о том, что задача выполнена, то по синхросигналу с выхода генератора 26 сигнал окончания выполнения задачи проходит через элемент И 7 канала на вход сброса триггера 2 данного канала. Триггер 2 устанавливается в нулевое состояние, и соответствующий процессор снова готов к приему задачи.

Если все процессоры заняты, то на выходе элемента ИЛИ 17 присутствует нулевой сигнал. При этом на выходе элемента ИЛИ 19 присутствует единичный сигнал, который открывает блок 15 элементов И и закрывает поступление информации с входов 38 через коммутатор 14. Поступающие очередные задачи через открытьй блок

5

0

5

0

5

элементов И t5 принимаются в блок 23 регистров. Теперь на выходах блока регистров 23 не нулевой сигнал, поэтому на выходе элемента ИЛИ 18 появляется единичный сигнал, который поступает на вход элемента ИЛИ 19. Блок 23 (24) регистров работает следующим образом. В начальном состоянии все регистры установлены в нулевое состояние, триггер 45 - в нулевое состояние, на синхровходы

29и 30 поступают синхроимпульсы. Если на входе 28 (33) появляется код задачи, то он поступает через блоки элементов ИЛИ 41 на входы всех ре- гистров 40. Запись кода происходит только в регистр 40.1, так как синхросигнал с входа 29 (34) поступает

на тактовый вход только .этого регистра через открытый элемент И 42.1 и элемент ИЛИ 44.1. Все остальные элементы И 42 закрыты соответствующими сигналами с элементов ИЛИ 43.

После записи кода первой задачи в регистр 40.1 появляется единичный сигнал на выходе элемента ИЛИ 43.1, который открывает элемент И 42.2 и закрывает элемент И 42.1. В связи с этим код следующей задачи запи- сывается в регистр 40.2. Далее коды задач записываются в описанном порядке.

Если на входе 31 (36) появляется единичньш сигнал, свидетельствующий о том, что в устройстве есть свободные процессоры, то информация первого регистра 40.1 поступает в освобо- дивщийся процессорi

Далее необходимо информацию, со- держащуюся в блоке 23 (24) регистров сдвинуть. Происходит это следующим образом. Синхросигнал с входа 29 (34) через открытый элемент устанавливает триггер 45 в единичное состояние, который открывает элемен И 47, При этом синхросигнал с входа

30(35), которьш выдается с задержкой относительно синхросигнала по входу 29- (34), поступает через от- крытьй элемент И 47 и через элементы ИЛИ 44 на тактовые входы всех регистров 40. Так как каждый регистр связан с последующим через блок элементов ИЛИ 41, то в них записывается информация из следующего регистра. Таким образом, в первый записывается информация второго регистра, во второй - третьего и т.д. Синхросигнал п

5 ,,

л с

Q е

5

входу 30 (35), кроме того, устанавливает триггер 45 по своему заднему фронту в нулевое состояние.

Как только освободится один из процессоров, о чем свидетельствует появление единичного сигнала .на выходе элемента ИЛИ 17, открывается коммутатор 14 для передачи информации с выхода блока 23 регистров. Информация с выходов блока 23 регистров поступает в освободившийся канал. Далее устройство функционирует аналогично описанному.

Рассмотрим работу устройства в случае, когда во время обработки задачи процессор выдает сигнал о неисправности. Допустим, что в процессе обработки задачи какой-то процессор в ыдает сигнал неисправности, который поступает на cooтвeтcтвyюш й . Это означает, что задачу, храняющуюся в регистре 3 данного канала, необходимо повторно передать на входы устройства для выполнения ее в другом исправном процессоре.

При. появлении сигнала о неисправности процессора на входах соответствующего элемента И-НЕ 9 все сигналы оказываются единичными. Поэтому нулевой сигнал с его выхода, воздействуя на соответствующий инверсный вход коммутатора 25, открывает его для передачи информации с выхода регистра 3 через коммутатор 25.

Далее по синхронизирующему сигналу с первого выхода генератора 26 код задачи, в зависимости от занятости процессоров, либо записывается в блок

24регистров, либо сразу поступает

в свободный процессор через коммутатор 14. Синхронизирующий сигнал с второго выхода генератора 26 через элемент И 8 поступает на вход элемента ИЛИ 11 и сбрасывает регистр 3. Таким образом, с выхода элемента ИЛИ 12 снимается единичный сигнал. На выходе элемента И-НЕ 9 появляется единичный сигнал, который разрещает другим каналам подключать выходы своих регистров 3 к выходу.коммутатора 25.

Если задача с выхода коммутатора

25записывается в блок 24 регистров,, то на выходе элемента ИЛИ 22 появляется единичный сигнал. Этот сигнал через элемент ИЛИ 20 запрещает по-, стуштение информации с выхода .коммутатора 26 через коммутатор 14, а также через элементы ИЛИ 21, 18 и 19 все другие входы коммутатора 14.

Сигнал с выхода элемента ИЛИ 21 закрывает элемент И 27, после чего, даже если появится единичный сигнал на выходе элемента ИЛИ 17, он не передается в блок 23 регистров до тех пор, пока не будут обслужены все задачи из блока 24 регистров.

Формула изобретения

Устройство для распределения заданий процессорам, содержащее первый блок регистров, первый коммутатор, первый и второй блоки элементов И, первый, второй и третий элементы ИЛИ, генератор импульсов и каналы, каждый из которых содержит триггер, первый и второй блоки элементов И, первый элемент ИЛИ, причем группа выходов первого блока регистров соединена с первой группой информационных входов первого коммутатора и с входа ми первого элемента ИЛИ, выход которого подключен к -прямому входу второго элемента ИЛИ,выход которого соединен с управляющим входом первого блока элементов И, выходы которого под ключены к информационным входам первого блока регистров, выход третьего элемента ИЛИ подключен к инверсному

целью повышения надежности за счет выполнения задач даже при отказе выполнявших их процессоров, в него дополнительно введены второй блок регистра, четвертый пятый и шестой элементы ИЛИ, элемент И, второй коммутатор, а в каждый канал введены регистр, второй и третий элементы ИЛИ, первый, второй и третий элементы И, элемент И-НЕ, входы кодов задач устройства подключены к второй группе информационных входов первого коммутатора и к группе входов пер вого блока элементов И, группа выходов второго коммутатора подключена к входам четвертого элемента ИЛИ, к третьей группе информационных входов первого коммутатора и к группе входов второго блока элементов И, группа выходов которого подключена к группе информационных входов второго блока регистров, группа выходов кото рого соединена с четвертой группой информационных входов первого коммутатора и с входами пятого элемента ИЛИ, выход которого подключен к второму управляющему входу первого коммутатора, а также к соответствующему входу че твертого элемента ИЛИ, выход которого подключен к третьему управляющему входу первого коммутатора и к соответствующему входу первого элемента ИЛИ, выход четвертого элемен та ИЛИ подключен к инверсному входу

входу второго элемента ИЛИ, выход которого подключен к первому управляю- элемента И, выход которого подключен

щему входу первого, коммутатора, груп,- входу разрешения записи первого

блока регистров, выход пятого эле- мента ИЛИ подключен к прямому входу шестого элемента ИЛИ, выход которого 40 подключен к четвертому управляющему входу первого коммутатора и к управляющему входу второго блока элементов И, выход третьего элемента ИЛИ подключен к прямому входу элемента 45 И, к инверсному входу шестого элемента ИЛИ и к входу разрешения запипа выходов которого подключена к группам выходов первого и второго блоков элементов И первого канала, к .первым управляющим входам первого и второго блоков элементов И каждого канала подключены соответственно прямой и инверсный выходы триггера данного канала,группа входов перво- го и второго блоков элементов И каждого канала, начиная с второго, соединена с группой выходов первого блока элементов И предыдущего канала, в каждом канале вьгходы второго блока элементов И являются соответствующей группой выходов устройства и соединены с входами первого элемента ИЛИ своего кана.ла, выход которого подключен к тактовому входу триггера

си второго блока регистров, первый выход генератора импульсов подключен к первым синхронизирующим вхо- 50 дам блоков регистров, второй выход генератора импульсов подключен к вторым синхронизирующим входам бло-г ков регистров, в каждом канале группа выходов второго блока элементов И

своего канала, инверсные выходы триг- подключена к группе информационных

геров каждого канала подключены к входам третьего элемента ИЛИ за счет обеспечения выполнения задач, о т- личающе е ся тем, что, с

7081

fO

15

20

25 JQ

целью повышения надежности за счет выполнения задач даже при отказе выполнявших их процессоров, в него дополнительно введены второй блок регистра, четвертый пятый и шестой элементы ИЛИ, элемент И, второй коммутатор, а в каждый канал введены регистр, второй и третий элементы ИЛИ, первый, второй и третий элементы И, элемент И-НЕ, входы кодов задач устройства подключены к второй группе информационных входов первого коммутатора и к группе входов первого блока элементов И, группа выходов второго коммутатора подключена к входам четвертого элемента ИЛИ, к третьей группе информационных входов первого коммутатора и к группе входов второго блока элементов И, группа выходов которого подключена к группе информационных входов второго- блока регистров, группа выходов которого соединена с четвертой группой информационных входов первого коммутатора и с входами пятого элемента ИЛИ, выход которого подключен к второму управляющему входу первого коммутатора, а также к соответствующему входу че твертого элемента ИЛИ, выход которого подключен к третьему управляющему входу первого коммутатора и к соответствующему входу первого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к инверсному входу

си второго блока регистров, первый выход генератора импульсов подключен к первым синхронизирующим вхо- 50 дам блоков регистров, второй выход генератора импульсов подключен к вторым синхронизирующим входам бло-г ков регистров, в каждом канале группа выходов второго блока элементов И

входов регистра своего канала, выходы регистров подключены к соответствующим группам информационных входов второго коммутатора, первый выход

генератора импульсов подключен к первому входу первого элемента И первого канала, к синхровходу регистра первого канала и ко второму управляющему входу второго блока элементов И первого канала, выход первого элемента И каждого канала соединен с вторым управляющим входом второго блока элементов И, с синхровходом регистра и с первым входом первого элемента И следующего канала, единичный выход триггера каждого канала соединен с вторым входом первого элемента И своего канала, инверсный выход триггера каждого канала подключен к входу разрешения записи регистра своего канала, каждый сигнальный вход первой группы сигнальных входов устройства соединен с первым входом второго элемента И своего канала, второй выход генератора импульсов соединен с вторым входом второго элемента И каждого канала, выход второго элемента И канала подключен к входу сброса триггера своего канала и к первому входу второго элемента ИЛИ своего канала, выход которого подключен к входу сброса регистра своего канала, выходы регистра канала подключены к входам третьего элемента ИЛИ своего канала, выход которого подключен к соответствующему входу элемента И-НЕ своего канала, выход которого подключен к

соответствующим входам элементов

И-НЕ остальных каналов, выход элемента И-НЕ каждого канала соединен с соответствующим управляющим входом группы управляющих входов второго

коммутатора и с инверсным входом второго элемента И своего канала, каждый сигнальный вход второй группы сигнальных входов устройства соединен с соответствующим входом

элемента И-НЕ одноименного канала и с единичным входом триггера своего канала, второй выход генератора импульсов соединен с прямым входом второго элемента И и с вторым входом

второго элемента ИЛИ всех каналов.

- 2

Фиг/

Я

Фиг. 2

.J

V П{Ъ1}

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1985 |

|

SU1277111A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1543404A1 |

| Многопроцессорная система | 1987 |

|

SU1494005A1 |

| Многопроцессорная система | 1989 |

|

SU1695318A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1751760A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1347080A1 |

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах. Цель изобретения - повышение надежности за счет обеспечения выполнения задач даже при отказе выполнявших их процессоров. Поставленная цель достигается тем, что в устройство для распределения заданий процессорам дополнительно введены блок регистров, коммутатор, элементы ИЛИ, И, а в каждый канал-регистр - элементы ИЛИ, И, И-НЕ. В устройстве обеспечивается выполнение задач даже при отказе выполнявших их процессоров, что достигается путем введения технических средств для хранения кодов задач до момента их завершения, а также перераспределения задач между процессорами в случае отказов одного или нескольких из них и присвоения отказным задачам максимальных приоритетов. 3 ил. (Л 00 4 1 О 00

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1111165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-23—Публикация

1985-11-25—Подача