Изобретение относится к вычисли- тельной технике и может быть использовано в отказоустойчивых многопроцессорных системах для распределения задач между процессорами.

Известно устройство, содержащее процессоры, регистр готовности процессоров, блок элементов И, первую и вторую группы элементов ИЛИ, блок регистров, первую, вторую и третью группы элементов И, первый, второй и третий элементы ИЛИ, элемент И f . Недостатком этого устройства является большой объем оборудования. Наиболее близким по технической сущности к предлагаемой системе является устройство для распределения заданий процессорам, содержащее блок регистров, блок элементов ИЛИ, элемент ИЛИ, элемент И-НЕ, элемент И п каналов, в каждом канале первый и второй триггеры, первый и второй блоки элементов И, первый и второй элементы И, элемент ИЛИ-НЕ, коммутатор, элемент сравнения, регистр, третий - восьмой элементы И, первый и второй элементы ИЛИ и одновиб- ратор

Недостатком этого устройства является низкая эффективность использования оборудования, которая заключается в том, что при отказе одного из процессоров канала из конфигурации выводится целый канал., , хотя в канале содержится еще один исправный процессор. Таким образом, исправный процессор не занят производительной работой до тех пор, пока отказавший в данном канале процессор

0

5

не будет восстановлен. В то же вре- . мя в системе может быть другой канал с аналогичной ситуаций, Два исправных процессора из двух кана- 5 лов, выведенных из конфигурации, могли бы составить работоспособную пару, однако в данном устройстве это не реализуется. Вследствие этого при появлении отказов процессоров снижается производительность системы. Низкая надежность функционирования известного устройства объясняется тем, что отказ каждого процессора ведет за собой вывод из конфигурации системы еще одного исправного процессора. Таким образом, если в каждом канале устройства откажут по одному процессору, то устройство переходит в состояние полного отказа, хотя в нем есть исправные процессоры. Это приводит к высокой вероятности отказа устройства в целом.

Целью изобретения является повышение надежности за счет организации параллельного функционирования произвольных пар исправных процессоров.

В предлагаемой системе исключена жесткая разбивка процессоров на пары. При поступлении задачи на обслуживание ей выделяются два любых свободных процессора системы. ЛЙя того, чтобы в последствии определить какие из процессоров решали одну и- ту же задачу, в каналы процессоров записывается код решаемой задачи. По окончании решения задачи в процессорах через общий коммутатор системы выдаются код результата решения и

S

код задачи одного из процессоров. Эти коды поступают для сравнения во все.каналы. Если в каком-либо из каналов совпал код результата решения с тем, который выдается через коммутатор, то считается, что задача решена правильно, так как вероятность выдачи процессорами одного кода в разные задачи пренебрежимо мала. В этом случае процессоры возвращаются в исходное состояние. Если выдаваемый через коммутатор код результата решения задачи не совпал ни с одним из кодов, выдаваемых другими процессорами, то считается, что задача не решена. В этом случае на основе результатов сравнения кодов задач определяется пара процессоров,

которая решала эту задачу, после чего к этой паре подключается еще один процессор, который не занят обслужи- ванием, и задача поступает на повторное решение. После повторного решения задачи по мажоритарному принципу два из трех определяется правиль- ный результат решения задачи и отказавший процессор. Отказавший процессор выводится из конфигурации системы, а два других процессора переводятся в исходное состояние, после чего они готовы к решению новых задач.

На фиг.1 приведена функциональная схема предлагаемой системы , на фиг.2- функциональная схема блока регистPOBJ на фиг.З - функциональная схема блока приоритета.

Многопроцессорная система содержит блок 1 регистров, блок 2 приоритета, второй 3 и первый 4 коммутато- ры, выходы 5..п блока приоритета 2, второй 6, третий 7, первый 8 и четвертый 9 пороговые элементы, эле мент И 10, элементы И-НЕ 11, выходы

10

5

20

второй одновибратор 33.К, первый 34.К, четвертый 35.К, третий Зб.К и второй 37.К управляющие входы п цессора 40.К, информационные вход 38.К и выход 39.К процессора 40.К процессор 40. К, информационные вх 41 и выход 42 блока 1 регистров, равляющий выход 43 и третий управ ющий вход 44 блока 1 регистров, в 45 синхронизации, в каждом канале системы содержится первый 46.К од вибратор, первый 47,К и второй 48 информационные выходы каналов.

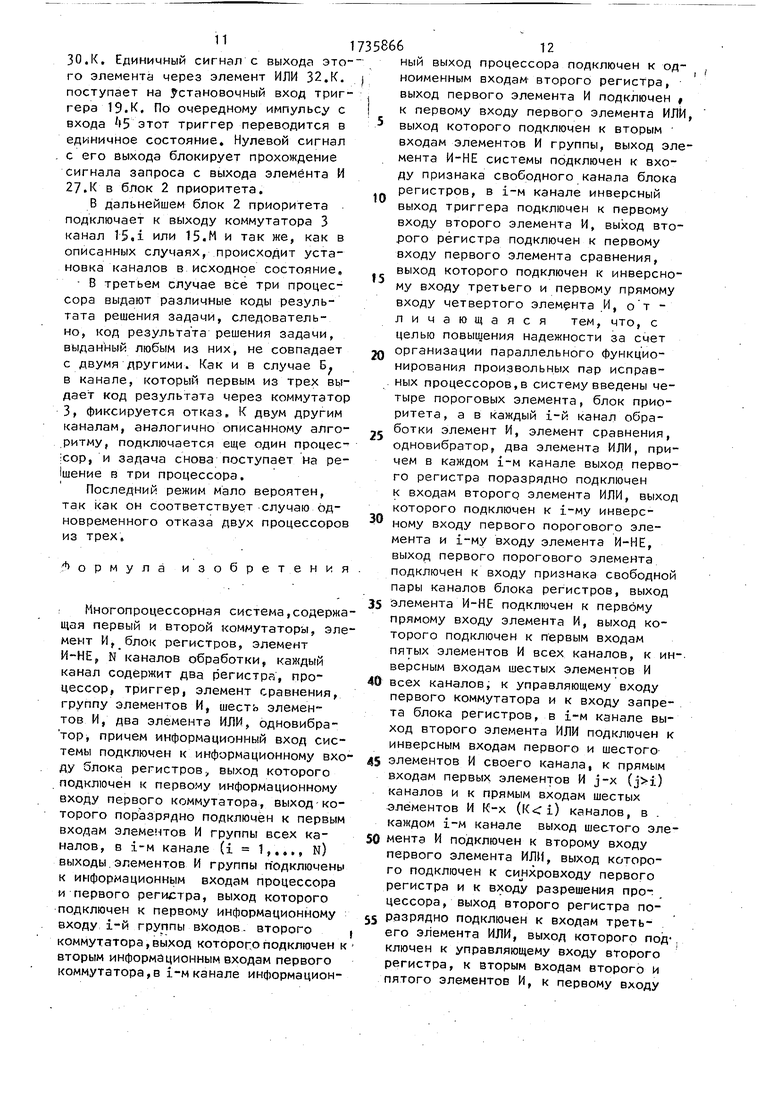

Блок 1 регистров (фиг. 2) соде жит М каналов 49.1-49.М и в каждо К-ом канале (К 1, 2, 3,..., М) гистр 50,К, блок 51.К элементов И синхровход 52.К регистра 50,К, эл менты ИЛИ 53. К и 54. К, элемент И 55.К, а также триггер 56, элемент И 57 и 58, элемент 59 задержки, элемент И 60 и элемент ИЛИ 61.

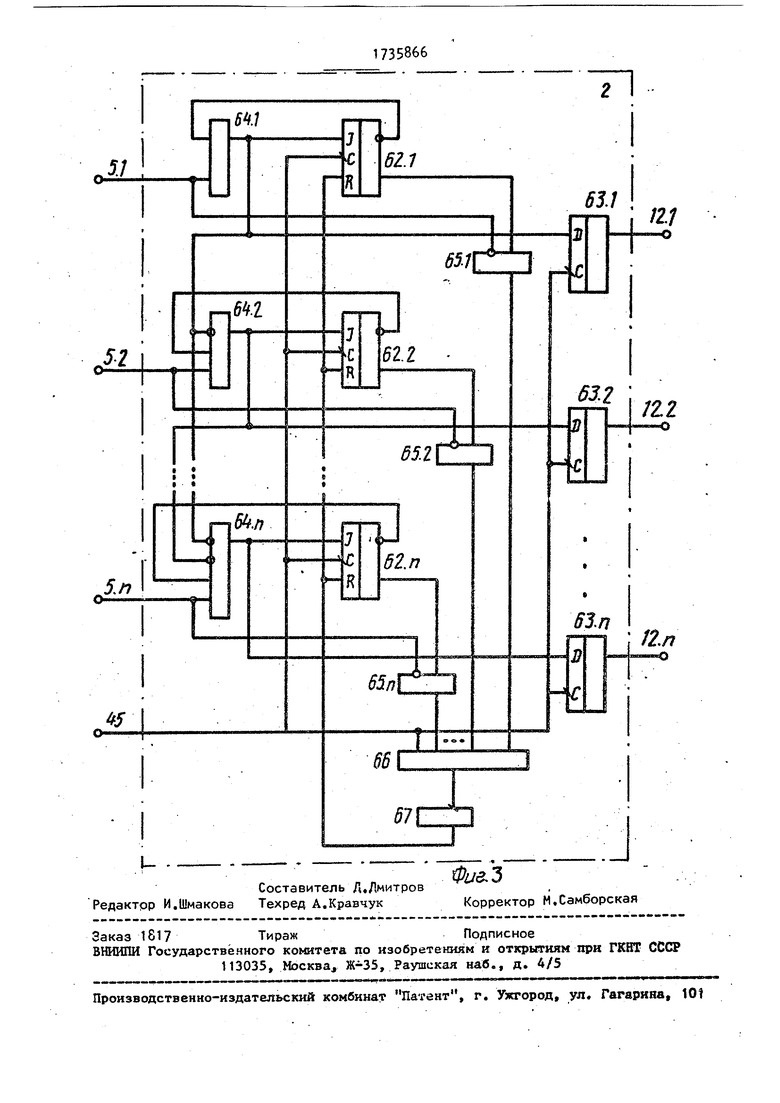

Блок 2 Приоритета (фиг. 3) сод

,е жит п -каналов и в каждом К-м (К ) канале триггеры 62.К и 63. элементы И 64.К, элемент ИЛИ 65.К а также элемент И 66 и одновибратор 67.

Система работает следующим обр зом.

В начальном состоянии блок 1 р гистров не содержит информации. Н выходах 12.1-12.п блока 2 приорит тов присутствуют нулевые сигналы.

35 В каждом К-м (К ) канале 15. регистры 16.К, 17.К и триггер 19. находятся в нулевом состоянии, про цессор 40.К находится в исходном состоянии и работоспособен. Так ка в регистрах 16.1-16,К - нулевая ин формация, то на выходе 14 мажоритарного элемента 8 присутствует ед ничный сигнал. Нулевой сигнал с вы хода элемента И 10 подключает к вы

30

40

12.1-12,п блока 2 приоритета, вход 13 45 ду коммутатора 4 выход 42 блока 1

признака свободного канала и вход 14 признака свободной пары каналов блока 1 регистров, каналы 15..ri и в каждом канале 15.К (К 1-п) первый 16.К и второй регистры, второй элемент ИЛИ 18.К, триггер 19.К, первый 20.К и второй 21.К элементы сравнения, первый 22.К, шестой 23.К, пятый 24.К, седьмой 25.К, третий 26«К и второй 27.К элементы И, блок 28,К элементов И, первый элемент ИЛИ 29.К, четвертый элемент И 30.К, третий 31.К и четвертый 32.К элементы ИЛИ, .

регистров.

Задачи поступают на вход 41 бло 1 регистров. Все поступившие в сис тему задачи фиксируются в блоке 1

50 регистров. Если в системе есть св бодные процессоры, о чем свидетель ствует единичный сигнал с выхода 1 порогового элемента 8, то задачи в даются из блока 1 регистров для ра

55 пределения. Для того, чтобы кажда задача поступила для решения в два процессора, в системе предусмотрен две схемы приоритетов. Одна из них

0

5

0

второй одновибратор 33.К, первый- 34.К, четвертый 35.К, третий Зб.К и второй 37.К управляющие входы про цессора 40.К, информационные вход 38.К и выход 39.К процессора 40.К, процессор 40. К, информационные вход 41 и выход 42 блока 1 регистров, управляющий выход 43 и третий управляющий вход 44 блока 1 регистров, вход 45 синхронизации, в каждом канале системы содержится первый 46.К одно- вибратор, первый 47,К и второй 48.К информационные выходы каналов.

Блок 1 регистров (фиг. 2) содержит М каналов 49.1-49.М и в каждом К-ом канале (К 1, 2, 3,..., М) регистр 50,К, блок 51.К элементов ИЛИ, синхровход 52.К регистра 50,К, элементы ИЛИ 53. К и 54. К, элемент И 55.К, а также триггер 56, элементы И 57 и 58, элемент 59 задержки, элемент И 60 и элемент ИЛИ 61.

Блок 2 Приоритета (фиг. 3) содере жит п -каналов и в каждом К-м (К ) канале триггеры 62.К и 63.Ку элементы И 64.К, элемент ИЛИ 65.К, а также элемент И 66 и одновибратор 67.

Система работает следующим образом.

В начальном состоянии блок 1 регистров не содержит информации. На выходах 12.1-12.п блока 2 приоритетов присутствуют нулевые сигналы.

5 В каждом К-м (К ) канале 15.К регистры 16.К, 17.К и триггер 19.К находятся в нулевом состоянии, процессор 40.К находится в исходном состоянии и работоспособен. Так как в регистрах 16.1-16,К - нулевая информация, то на выходе 14 мажоритарного элемента 8 присутствует единичный сигнал. Нулевой сигнал с выхода элемента И 10 подключает к выхо0

0

регистров.

Задачи поступают на вход 41 блока 1 регистров. Все поступившие в систему задачи фиксируются в блоке 1

регистров. Если в системе есть свободные процессоры, о чем свидетельствует единичный сигнал с выхода 14 порогового элемента 8, то задачи выдаются из блока 1 регистров для распределения. Для того, чтобы каждая задача поступила для решения в два процессора, в системе предусмотрены две схемы приоритетов. Одна из них,

образованная элементами И 22,1-22.п, выбирает первый свободный процессор, начиная с процессора с меньшим лоряд ковым номером, а другая, образованна элементами И 23.1 - 23«пг выбирает -первый свободный процессор, наминая с процессора с большим порядковым номером, Таким образом, задача, поступившая первой в систему решается в первом 40.1 и последнем 40.п процессорах. Если до окончания ее решения поступит вторая задача, то она решается во втором АО.2 и предпоследнем 40,п-1 процессорах. В случае, если к моменту поступления очередной задачи процессор 40.1 свободен, а процессор 40.п занят обслуживанием задачи или находится в неработоспособном состоянии, то очередная задача поступает для решения в процессор 40.1 и первый свободный процессор, расположенный после процессора 40,п в сторону уменьшения порядковых номеров процессоров. Таким образом, использование двух приоритетных схем, одна из которых выбирает свободный процессор сверху, а вторая - снизу, позволяет обеспечить поступление каждой задачи для решения одновременно в два процессора. Если в системе нет свободной пары процессоров, то на выходе t4 мажоритарного элемента 8 имеется нулевой сигнал, который запрещает блоку 1 регистров выдавать задачи. В этом случае задачи, поступающие на вход 41, фиксируются в блоке 1 регистров и ожидают освобождения процессоров.

Задача поступает в процессоры для решения следующим образом. Пусть схема приоритета на элементах И 22.1- 22.п определила первый свободный процессор сверху 40.К, а схема приоритета на элементах И 23. определила свободный процессор снизу 40.М (К м). При наличии в блоке 1 регистров задачи она поступает с выхода 42 через коммутатор 4 на информационные входы всех блоков элементо И 28.1-28.П, После этого на выходе 4 блока.1 регистров появляется импульсный сигнал, который проходит через элементы И 22,К и И23.М, Далее этот1 сигнал, пройдя «ерез соответствующие элементы ИЛИ .п, открывает блоки элементов И 28.К и 28.М Код задачи с выходов 36.К и 38.М блоков элементов И 28,К и 28.М соответст5

венно поступает в процессоры 40.К и 40.М, а также на информационные входы регистров 16.К и 16.М. По заднему фронту сигналов с выходов элементов ИЛИ 29.К и 29.М происходит запись кода задачи в соответствующие регистры 16.К и 16.М и прием кода задачи в процессоры 40.К и 40.М. На

Q выходах элементов ИЛИ 18.К и 18.М появляются единичные сигналы, которые свидетельствуют о том, что соот- ветствующие процессоры 40.К и 40.М заняты обслуживанием задачи.

Далее происходит процесс решения задачи- в процессорах.

После того, как процессоры решат задачу, они выставляют код результата ее решения на соответствующих вы

0 ходах 39«К и 39.М. Работа процессоров

40.1-40.ti синхронизируется теми же , импульсами, что и работа системы, поэтому для нормальной работы системы необходимо, чтобы процессоры выста

5 вили код результатов решения в паузах между импульсами с входов 45, а снимали после того, как получат сигнал о том, что код принят (поступит на соответствующий вход 37..п),

л Кроме того, два процессора, решающие одну задачу, выдают коды результата решения задачи в пределах одного такта импульсов с входа 45.

После того,как коды результатов решения задачи запишутся в регист$ ры 17.К и 17.М, появляются единичные сигналы на выходах элементов ИЛИ 31,К и 31.М, которые через элементы И 27.К, 27.М поступают в блок 2 приоритетов в качестве запросов на под0 ключение к выходу коммутатора 3. Блок 2 приоритетов анализирует запросы, поступающие от всех каналов, и подключает информационные выходы самого приоритетного канала (с мень5 шим порядковым номером) к выходу коммутатора 3. Таким образом, если нет запросов от каналов 15..K-1, к выходу коммутатора 3 подключатся выходы регистров 16.К и 17.К канала 15.К, Код с выхода регистра 16.К поступает на соответствующие входи/ блоков 20.1-20.П сравнения всех каналов, а код с выхода регистра 17.К г на соответствующие входы блоков 21.1- 21.п сравнения всех каналов.

O

5

v Далее возможна два режима работы системы: процессоры правильно решили задачу и выдали совпадающие коды

10

результатов ее решения; процессоры выдали разные коды результатов решения-задачи, т.е. один из процессоров (или оба процессора) в результате решения задачи отказал или дал сбой.

Если процессоры АО.К, АО.М выдали совпадающие коды результатов решения (режим l), то на выходах блоков 20.К, 21.К и 20.М, 21.М сравнения появляются единичные сигналы. Эти сигналы совместно с единичным CHI- налом с выхода мажоритарного элемента 9 открывают элементы И 25.К и 25.М для прохода импульса с входа А 5 Очередной импульс с входа А5 проходит через открытые элементы И 25.К, 25.М и своим задним фронтом запускает одновибраторы 33.К и 33.М.Импульсы с выходов одновибраторов 33„К, 33.М устанавливают соответствующие регистры 16.К, 17.К и 16.М, 17.М в нулевое состояние, после чего на выходах элементов ИЛИ 1Р.К, 18.М появляются нулевые сигналы, свидетель- 25 ствующие о том, что процессоры АО.К и АО.М свободные и готовы принять очередную задачу для решения.

Абонент принимает кол задачи и код результата ее решения с выходов А7.К, А7.М и А8,К, А8.М соответственно по переднему фронту импульса с выходов 35.К и 35.М.

Если процессоры АО.К и АО.М выдали несовпадающие коды результатов

ИЛИ 29.К, 29.М. Импульс с входа А5 проходит также через открытый элемент И 22,1, Далее аналогично описанному происходит запись кода нерешенной задачи из регистра 16.К в процессоры АО.К, АО.М, А0.1. Повторно задача решается в трех процессорах.

Рассмотрим, как будет решаться система после того, как процессоры АО,К, АО.М , АО.1 закончили решать задачу.

Возможны три исхода решения задачи и соответствующие им три режима . работы системы: все процессоры выдали одинаковый код результата решения задачи (в этом случае считается, что один из процессоров АО.К, АО.М при первом решении задачи дал 2о сбой), один из процессоров выдает код результатов решения, совпадающий с двумя другими; все три процессора выдали различные коды результатов решения задачи.

30

В первом случае система работает аналогично первому режиму, когда при первичном решении задачи процессоры выдают совпадающие коды результатов решения задачи,

В втором случае возможны два варианта: на выход коммутатора 3 выдается код результата, полученный исправным процессором (А)} на выход коммутатора 3 выдается код результарешения задачи (режим и), то при на- 35 та, полученный неисправным (отказавшим) процессором (Б),

В случае А (допустим отказал процессор АО.К, а через коммутатор 3 выдаются коды из канала 15.i) в каналах 40 15.1 и 15.М открыты элементы И 25.1 и 25.М соответственно, а в канале 15.К на выходе элемента И 26.К имеется единичный сигнал. Этот сигнал через элемент ИЛИ 32.К поступает на

единичный сигнал блокирует схему при- 45 вход установки в единицу триггера оритета, образованную элементами И 19,К. Очередной синхроимпульс с входа А5 проходит через открытые элеличии единичного сигнала с выхода элемента И-КЕ 11, который свидетельствует о том, что в системе есть хоть один свободный процессор, открываются элементы И 2А.К, 2А.М для прохода импульса с входа А5. На выходе элемента И 10 имеется единичный сигнал, так как коды результатов решения задачи не сравнились. Этот

23.1-23.ri, В системе работает только приоритетная схема, образованная элементами И 22,1-22,п, которая выбирает один из свободных процессоров (допустим, процессор АО.1). Кроме того, единичный сигнал с выхода элемента И 10 запрещает блоку 1 регистров выдавать код задачи через коммутатор А и разрешает проход кода задачи с выхода регистра 16.К. Очередной синхроимпульс с входа А5 проходит через открытые элементы И 2А.К, 2А.М на входы соответствующих элементов

менты И 25,1, 25.М на установку каналов 15,1, 15.М в исходное состоя50 ние, потому что задача решена. Этот же импульс своим задним фронтом устанавливает триггер 19.К в единичное состояние, фиксируя тем самым отказ процессора АО.К.

55 В случае Б (допустим, что отказал процессор АО.К и его же коды выдаются с выхода коммутатора 3) из трех каналов 15.1, 15. К и 15.М только в канале 15.К открыт элемент И

0

5

ИЛИ 29.К, 29.М. Импульс с входа А5 проходит также через открытый элемент И 22,1, Далее аналогично описанному происходит запись кода нерешенной задачи из регистра 16.К в процессоры АО.К, АО.М, А0.1. Повторно задача решается в трех процессорах.

Рассмотрим, как будет решаться система после того, как процессоры АО,К, АО.М , АО.1 закончили решать задачу.

Возможны три исхода решения задачи и соответствующие им три режима работы системы: все процессоры выдали одинаковый код результата решения задачи (в этом случае считается, что один из процессоров АО.К, АО.М при первом решении задачи дал сбой), один из процессоров выдает код результатов решения, совпадающий с двумя другими; все три процессора выдали различные коды результатов решения задачи.

В первом случае система работает аналогично первому режиму, когда при первичном решении задачи процессоры выдают совпадающие коды результатов решения задачи,

В втором случае возможны два варианта: на выход коммутатора 3 выдается код результата, полученный исправным процессором (А)} на выход коммутатора 3 выдается код результаменты И 25,1, 25.М на установку каналов 15,1, 15.М в исходное состояние, потому что задача решена. Этот же импульс своим задним фронтом устанавливает триггер 19.К в единичное состояние, фиксируя тем самым отказ процессора АО.К.

В случае Б (допустим, что отказал процессор АО.К и его же коды выдаются с выхода коммутатора 3) из трех каналов 15.1, 15. К и 15.М только в канале 15.К открыт элемент И

30.К. Единичный сигнал с выхода это го элемента через элемент ИЛИ 32.К. поступает на установочный вход триггера 19.К, По очередному импульсу с входа этот триггер переводится в единичное состояние. Нулевой сигнал с его выхода блокирует прохождение сигнала запроса с выхода элемента И 27. К в блок 2 приоритета.

В дальнейшем блок 2 приоритета подключает к выходу коммутатора 3 канал 15.1 или 15.М и так же, как в описанных случаях, происходит установка каналов в исходное состояние,

В третьем случае все три процессора выдают различные коды результата решения задачи, следовательно, код результата решения задачи, выданный любым из них, не совпадает с двумя другими. Как и в случае Б в канале, который первым из трех выдает код результата через коммутатор 3, фиксируется отказ, К двум другим каналам, аналогично описанному алгоритму, подключается еще один процессор, и задача снова поступает на ре- шение в три процессора.

Последний режим мало вероятен, так как он соответствует случаю одновременного отказа двух процессоров из трех.

о р м у л а

изобретения

Многопроцессорная система,содержащая первый и второй коммутаторы, элемент И, блок регистров, элемент И-НЈ N каналов обработки, каждый канал содержит два регистра, процессор, триггер, элемент сравнения, группу элементов И, шесть элементов И, два элемента ИЛИ, одновибра- тор, причем информационный вход системы подключен к информационному вхо- 45 элементов И своего канала, к прямым

ду блока регистров, выход которого подключен к первому информационному входу первого коммутатора, выход которого поразрядно подключен к первым входам элементов И группы всех каналов, в i-м канале (г - 1,..., N) выходы элементов И группы подключены к информационным входам процессора и первого регистра, выход которого подключен к первому информационному входу i-й группы входов второго , коммутатора,выход которого подключен к вторым информационным входам первого коммутатора,в i-м канале информационвходам первых элементов И j-x () каналов и к прямым входам шестых элементов И К-х () каналов, в каждом i-м канале выход шестого эле

50 мента И подключен к второму входу первого элемента ИЛИ, выход которого подключен к синхровходу первого регистра и к входу разрешения процессора, выход второго регистра по55 разрядно подключен к входам третьего элемента ИЛИ, выход которого под ключен к управляющему входу второго регистра, к вторым входам второго и пятого элементов И, к первому входу

5

ныи выход процессора подключен к одноименным входам второго регистра, выход первого элемента И подключен к первому входу первого элемента ИЛИ, выход которого подключен к вторым входам элементов И группы, выход элемента И-НЕ системы подключен к входу признака свободного канала блока регистров, в i-м канале инверсный выход триггера подключен к первому входу второго элемента И, выход второго регистра подключен к первому входу первого элемента сравнения, выход которого подключен к инверсному входу третьего и первому прямому входу четвертого элемента отличающаяся тем, что, с целью повышения надежности за счет организации параллельного функционирования произвольных пар исправных процессоров, в систему введены четыре пороговых элемента, блок приоритета, а в каждый i-й канал обраg. ботки элемент И, элемент сравнения, одновибратор, два элемента ИЛИ, причем в каждом i-м канале выход первого регистра поразрядно подключен к входам второго элемента ИЛИ, выход которого подключен к i-му инверсному входу первого порогового элемента и i-му входу элемента И-НЕ, выход первого порогового элемента подключен к входу признака свободной пары каналов блока регистров, выход

5 элемента И-НЕ подключен к первому прямому входу элемента И, выход которого подключен к первым входам пятых элементов И всех каналов, к инверсным входам шестых элементов И всех каналов, к управляющему входу первого коммутатора и к входу запрета блока регистров, в i-м канале выход второго элемента ИЛИ подключен к инверсным входам первого и шестого

0

0

входам первых элементов И j-x () каналов и к прямым входам шестых элементов И К-х () каналов, в каждом i-м канале выход шестого элемента И подключен к второму входу первого элемента ИЛИ, выход которого подключен к синхровходу первого регистра и к входу разрешения процессора, выход второго регистра поразрядно подключен к входам третьего элемента ИЛИ, выход которого подключен к управляющему входу второго регистра, к вторым входам второго и пятого элементов И, к первому входу

седьмого элемента И, к входу сброса процессора, выход первого регистра подключен к первым входам второго элемента сравнения, выход которого подключен к вторым входам третьего, четвертого и седьмого элементов И, к третьему входу пятого элемента И, к i-м входам второго и третьего пороговых элементов, в каждом i-м канале выход второго элемента сравнения подключен к третьему входу седьмого элемента И и к j-му входу четвертого порогового элемента, выход которого подключен к инверсному входу элемента И, к четвертым входам седьмых элементов И всех каналов, к второму прямому входу третьего и инверсному входу четвертого элементов И всех каналов, выход второго порогового элемента подключен к третьим прямым входам третьих и четвертых элементов tH всех каналов, выходы которых под- ключены к первому и второму входам четвертого элемента ИЛИ своего канала, в каждом i-м канале выход четвертого элемента ИЛИ подключен к установочному входу триггера, инверсный выход которого подключен к разрешающим входам первого и второго элементов сравнения, выход третьего порогового элемента подключен к третьему входу элемента И,в i-м ка0

5

0

S

0

нале выход пятого элемента И через первый одновибратор подключен к первому входу сброса второго регистра, второму входу сброса процессора и к третьему входу первого элемента ИЛИ, выход седьмого элемента И через второй одновибратор подключен к второму входу сброса второго регистра, к входу сброса первого регистра и к третьему входу сброса процессора, первая группа выходов второго коммутатора подключена к вторым входам первых элементов сравнения всех каналов, вторая группа выходов вто- рого коммутатора подключена к вторым входам вторых элементов сравнения всех каналов, вход синхронизации системы подключен к одноименным входам регистров и приоритета, синхровхо- дам вторых регистров всех каналов, четвертым и пятым входам пятых и седьмых элементов И всех каналов, синхровходам триггеров всех каналов, синхровходам процессоров всех каналов, в i-м канале выходы вторых элет ментов И подключены к i-м входам блока приоритета, i-e выходы которого подключены к i-м управляющим входам второго коммутатора, в i-м канале выход второго регистра подключен к второму входу i-й группы входов второго коммутатора

9985Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная система | 1989 |

|

SU1695318A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

| Многопроцессорная вычислительная система | 1991 |

|

SU1837309A1 |

| Многопроцессорная система | 1987 |

|

SU1494005A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Устройство приоритета | 1990 |

|

SU1742820A1 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1543404A1 |

Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых многопроцессорных системах для распределения задач между процессорами. Целью изобретения является повышение надежт ности за счет организации параллельного функционирования произвольных пар исправных процессоров. Поставленная цель достигается тем, что многопроцессорная система содержит блок 1 регистров, блок 2 приоритета, комму

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1111165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление к вязальным машинам для указания работающему подлежащих выполнению операций | 1927 |

|

SU14956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-23—Публикация

1989-11-09—Подача