Изобретение относится к автоматике и вычислительной технике и может быть использовано в аналоговых вычислительных машинах при моделировании объектов с запаздыванием в широком диапазоне, а также в автоматических системах регулирования технологических процессов, использующих модели объекта с регулируемым запаздыванием, например, в системах, используппих принцип упреждения запаздывания и компенсации инерционности.

Целью изобретения является расширение диапазона изменения времени за- паздывания.

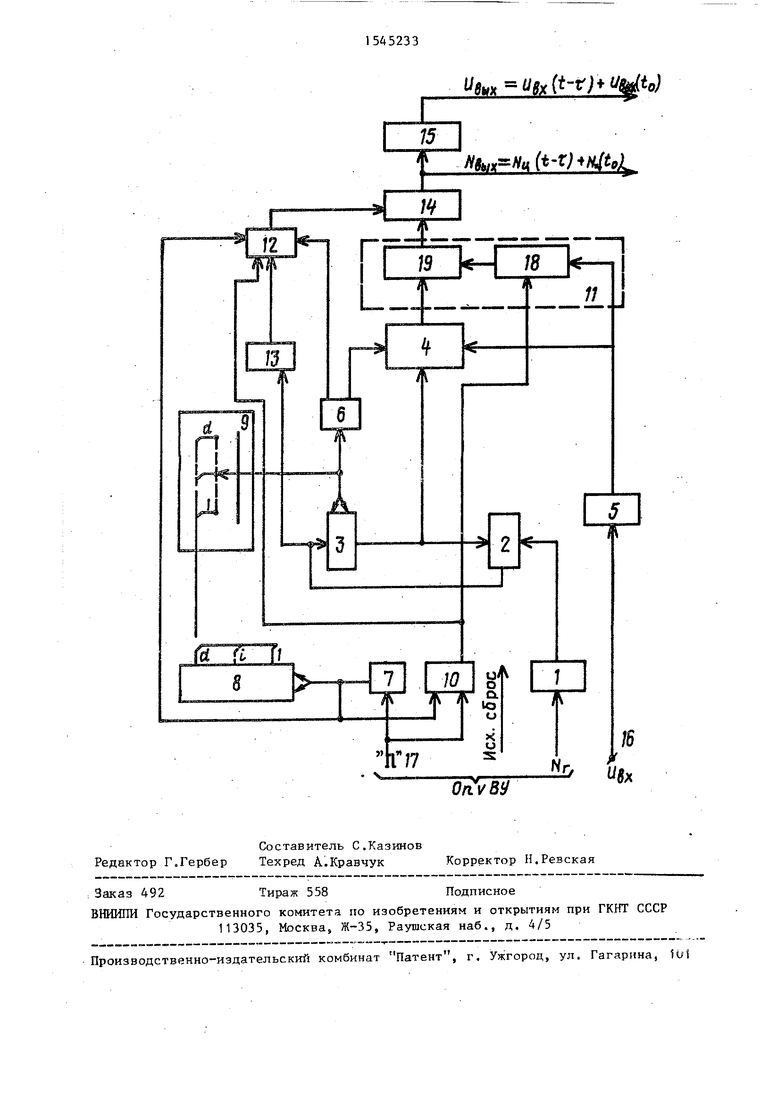

На чертеже изображена блок-схема устройства для воспроизведения запаздывающих Функций.

Устройство содержит регистр 1 ко- да задержки, блок 2 сравнения кодоч, счетчик 3 адреса, блок 4 оперативном памяти, аналого-цифровой преобразователь 5, формирователь 6 импульсов, генератор 7 опорной частоты, делитель 8 частоты, переключатель 9, первый триггер 10, коммутатор 11 кодов, коммутатор 12 управления, второй триггер 13, регистр 14, выходной пифроанало- говый преобразователь 15, вход 16 устройства и шину 17 запуска. Коммутатор 11 кодов может быть выполнен на группе элементов И 18 и группе элементов ИЛИ J9.

В основу построения устройства на- ложен принцип регулирования количества адресов блока оперативной памяти в зависимости от установленного задания времени запаздывания согласно с переключением диапазонов работы, с которым изменяется рабочая частота квантования входного сигнала с заданной кратностью, причем таким образом, чтобы при использовании времени запаздывания, соответствующего верхне- му значению диапазона, заполнялось максимальное (заданное на основном диапазоне) количество числовых линеек блока оперативной памяти, инФорма- ционная емкость которого выбрана по- стоянкой из условия неискаженной передачи самого быстродействующего аналогового сигнала в основном диапазоне и сохранения постоянной минимальной погрешности воспроизведения времени запаздывания, изменяющегося в широком диапазоне значений.

Устройство работает следующим разом.

В исходном положении генерация с выхода управляемого генератора 7 опорной частоты отсутствует, регистр 1 счетчика 3 адреса, делитель 8 частоты, первый 10 и второй 13 триггеры и регистр 14 находятся в нулевом состоянии которое они устанавливаются оператором или внешним устройством командой Исходный сброс. Аналого- цифровой преобразователь 5 работает в непрерывном автоматическом режиме, преобразуя входной аналоговый сигнал U6x в двоичный код, прохождение которого через коммутатор 11 запрещено триггером 10. Запись выходного кода преобразователя 5 в блок 4 памяти по нулевому коду счетчика 3 адреса не производится, так как отсутствуют импульсы чтения-записи с Формирователя 6, который запускается импульсами с генератора 7 через делитель 8 частоты и переключатель 9.

Перед запуском устройства в работу оператором или внешним устройством вьтюлняются две подготовительные опе- рании. В регистр 1 заносится двоичный кч I Л-.,, соответствующий приведенному

L-

з: чению времени запаздывания , и переключателем 9 выбирается поддиапазон, соответствующий заданному значению времени запаздывания.

Запуск устройства в работу осуществляется оператором или внешним устройством одновременно с запуском модели объекта (при моделировании на аналоговой матине) или при запуске адаптивной системы управления с моделью объекта командой Пуск. При этом первый триггер 10 переключается в единичное состояние, разрешая прохождение кода с выхода аналого-ииА- рового преобразователя 5 через коммутатор 11 на вход регистра 14. Одновременно с командой Пуск начинает работать генератор 7 опорной частоты, импульсы которого подаются на счетный вход делителя частоты и на вход коммутатора 12. Первый же импульс с выхода генератора 7 проходит через коммутатор 12, на первом управляющем входе которого присутствует разрешающий сигнал с выхода триггера

10,и осуществляет занесение в регистр 14 кода с выхода коммутатора

11.Двоичный код ) с выхода регистра 14 передается во внешние ииФ- ровые блоки и поступает на входы ииг4 роаналогового преобразователя 15,

515/4

аналоговый сигнал U(t0) с которо: о используется в аналоговых блоках моделирующей машины или адаптивной системы управления. Так задаются в устройстве начальные условия.

По заднему Лронту первого импульса с выхода генератора 7 триггер 10 устанавливается в нулевое состояние, запрещено прохождение кода преобразователя 5 через коммутатор I I.

Импульсы с одного из выходов делителя 8 частоты через переключатель 9 поступают на счетный вход счетчика 3 адреса и запускают Формирователь 6. Счетчик 3 последовательно Формирует адреса для блока 4 памяти, начиная с первого. По каждому адресу Формирователь 6 посылает сигналы чтения-записи. По сигналу чтения информация по выбранному адресу считывается из блока 4 оперативной памяти и через коммутатор 1) передается на нход регистра 14, но в первом пикле работы не заносится в него. то обусловлено отсутствием синхронируюпего импульса, который блокируется триггером 13, на- ходятимся в нулевом состоянии в течение всего первого иикла работы и запрещающим прохождение импуаьса с первого выхода формирователя 6 через коммутатор 12. Поэтому в первом иик3

ле работы с помощью сигнала чтения осуществляется очистка числовых линеек блока 4 памяти, а по сигналу записи информация с выхода аналого-цифрового преобразователя 5 записывается в блок 4. При коде счетчика 3 адреса, совпадающего с кодом регистра выхода блока 2 сравнения появляется импульс, который осуществляет сброс

счетчика 3 адреса и установку триггера 1 3 в единичное состояние, разрешающего прохождение синхроимпульсов через коммутатор 12. Таким образом,

начиная со второго никла считанная из блока 4 памяти информация поступает в регистр 14 кода и на его выходе реализуется зависимость N ВЬ1 NuXt- -Ј) + N(t0), а на выходе инфроайалотового преобразователя 15 - аналоговая Функция t ftbiy U6x(t-Ј) +

IW)По окончании процесса при моделировании на аналоговой матине одновре-ченно с основным процессом приходит сигнал исходного сброса, а при использовании устройства в системе правления оно работает непрерывно. При использовании устройства в автономном режиме его останов производится оператором нажатием кнопки Исходный сброс.

Hfax faft-rj+qfrfeJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1285493A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1361615A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство для считывания цветной графической информации | 1989 |

|

SU1695339A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ИНФОРМАЦИИ | 1967 |

|

SU222908A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

Цель изобретения - расширение диапазона измерения времени запаздывания. Устройство содержит генератор опорной частоты, аналого-цифровой преобразователь, подключенный входом к входу устройства, а выходом - к информационному входу блока оперативной памяти. Дополнительно введены формирователь импульсов, регистр кода задержки, переклячатель и делитель частоты.

f (-r; &

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1249546A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-23—Публикация

1985-03-05—Подача