1

(21)4436232/24-24

(22)06.06.88

(46) 28.02.90. Бюл. № 8

(71.) Сумский филиал Харьковского

политехнического института

им. В.И.Ленина

(72) А.А.Борисенко, В.А.Соловей

и В.М.Мирошниченко

(53)681.325(088.8)

(56) Авторское свидетельство СССР 531158, кл. G Ob F 15/00, 1974.

(54)ПРЕОБРАЗОВАТЕЛЬ КОДОВ

(57) Изобретение относится к вычислительной технике и автоматике и может быть использовано в системах дискретной обработки и передачи информации в качестве устройства кодирования-декодирования информации, использующего равновесные коды. Цель изобретения - повышение быстродействия преобразователя. Преобразователь кодов содержит регистр 1 текущей выборки, первый - третий счетчики 2-4, формирователь 5 кодов, блок 6 синхронизации, сумматор 7, блок 8 сравнения, первый и второй регистры 9 и 10 числа, первый - шестой входы 11 16 и первый - третий выходы 17 - 19. Блок 6 синхронизации содержит триггер, элемент ИЛИ-НЕ, элемент ИЛИ, первый - четвертый входы и первый - четвертый выходы. 1 з.п. ф-лы, 2 ил.

Изобретение относится к автоматике и вычислительной технике и может быть спользовано в системах дискретной обработки и передачи информации в качестве устройства кодирования-декодирования информации, использующего равновесные коды.

Цель изобретения - повышение быстродействия преобразователя.JQ

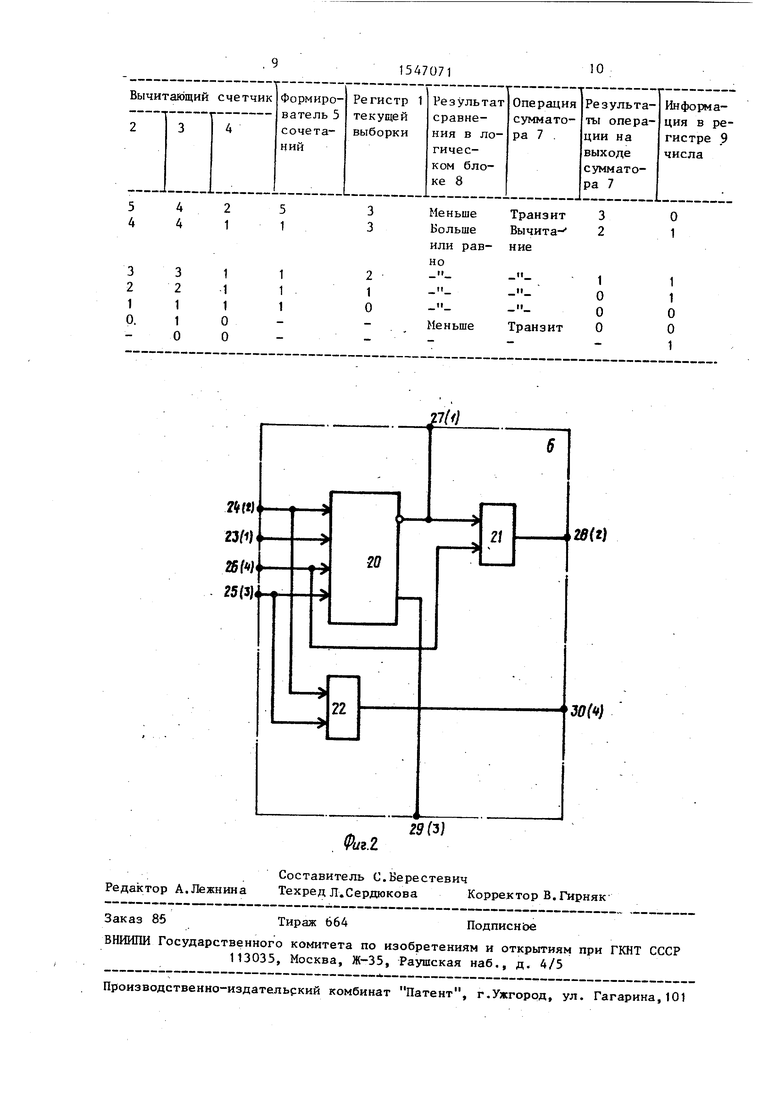

На фиг. 1 представлена функциоальная схема преобразователя кодов; а фиг. 2 - схема блока синхронизаии преобразователя.

Нреобразоватнль кодов (фиг. 1) со- j ержит регистр 1 текущей выборки, первый - третий счетчики 2-4, форирователь 5 кодов, блок 6 синхронизации, сумматор 7, блок 8 сравнения, первый и второй регистры 9 и 10 чис- JQ а, первый - шестой входы 11 - 16 и первый - третий выходы 17 - 19.

Блок b синхронизации (фиг. 2) содержит триггер 20, элемент ИЛИ-НЕ 21, элемент ИЛИ 22, первый - четвертый 25 входы 23 - 26 и первый - четвертый выоды 27-30 блока синхронизации.

Преобразователь кодов работает слеующим образом,

Процедура преобразования двоичного ,., кода в код с постоянным весом использует в качестве промежуточных биномиальный код. Биномиальное двоичное число характеризуется наличием К единиц или n-К нулей в старших разрядах перед младшей единицей. Диапазон -представления биномиальных чисел . Например, для и

числа 00110, 001111, 1111 являются биномиальными.40

Перевод исходного двоичного числа в биномиальное использует принцип поразрядного взвешивания. Вес каждого разряда биномиального числа определяется величиной сочетания С . ,

где q. - число единиц в предшествую- щих разрядах; ,1,2...,п-1. Сочетания формируются формирователем 5, который при подаче на одну группу BXOVQ дов значения п, а на другую значения

о

К формирует на выходе значение С h. В качестве такого формирователя может быть использовано ПЗУ. Для подсчета числа разрядов n-1-i, числа единиц и числа нулей (K-q-), (п-К) использ уются вычитающие двоичные счетчики 2,3 и 4. Сравнивают переводимое число с весом текущего разряда. Опре35

Q

5

.,

0

Q

5

деляют разность между этими числами. С этой целью применяют сумматор 7. При положительном значении разности или при равенстве этого числа присваивают разряду значение 1, при отрицательном - значение О. Эту функцию выполняет блок 8 сравнения, который сравнивает кодовые комбинации на двух группах входов и выдает сигналы Больше или равно или Меньше. В качестве блока 8 может быть использован цифровой компаратор.

Определяют остаток полученной разности, который при положительном ее значении равен абсолютной величине этой разности, а при отрицательном - исходному значению переводимого числа, и сравнивают с весом следующего разряда. Эту процедуру выполняют до тех пор, пока кодовая комбинация не станет удовлетворять условиям биномиального числа.

Для получения кода с постоянным весом к биномиальному коду справа дописывают нули, если в нем содержится К единиц, или единицы, если в нем содержится (n-К) нулей, до тех пор, пока разрядность кода не станет рав- .ной п. Выходные кодовые комбинации накапливаются в регистрах 9 и 10 числа, представляющих собой сдвиговые регистры.

Подробно работу преобразователя рассмотрим на примере перевода двоичного кода 011 числа 3 в шести разрядный код с постоянным весом () с числом единиц .

-Сигналом установки по входу 13 преобразователя выполняются следующие операции. По входу 1 в регистр 1 текущей выборки записывается входная кодовая комбинация 011; по входу 14 преобразователя в счетчик 2 - число п-1, в данном случае по входу 15 в счетчик 3 - число по входу 16 в счетчик 4 - число (п-К). Обнуляются регистры 9 и 10 числа.

С выхода регистра 1 текущей выборки входной двоичный код поступает на первый вход сумматора 7 и второй вход блока 8. С выхода счетчиков 2 и 3 текущие значения и поступают на входы формирователя 5. При этом на выходе формирователя 5 появляется значение сочетания , которое поступает на второй вход сумматора 7 и первый вход блока 8. Так как на втором входе блока 8 находится исходное

число 3, а на первом входе - число 5 блок Ъ формирует сигнал Меньше (), который поступает на соответсвующий вход блока b синхронизации, т.е. на информационный вход триггера 20. Отрицательный фронт синхросигнала записывает сигнал Меньше в триггер 20 и открывает элемент ИЛИ- НЕ 21. Таким образом, сигнал с инверсного выхода триггера 20 через элемент ИЛИ-НЕ 21 поступает на третий (управляющий) вход сумматора 7 в виде команды Транзит, что соответствует транзитной передаче двоичного кода с первого входа сумматора 7 на выход без изменения. Одновременно сигнал с инверсного выхода триггера 20 формирует О в первом разряде регистра 9 числа и запрещает выборку счетчика 3. Сигнал с прямого выхода триггера 20 разрешает выборку счетчика 4.

Положительным фронтом синхросигнала на входе 12 преобразователя в регистр 1 текущей выборки с выхода сумматора 7 записывается двоичный код числа 3, т.е. 011. В регистр 9 числа записывается ранее сформированный сигнал О. Одновременно уменьшается на 1 содержимое счетчика 2, т.е. и счетчика 4, т.е. . Содержимое счетчика 3 остается без изменения, т.е.-равно 4. На этом завершается первый этап сравнения (взвешивания) входного двоичного кода и веса старшего разряда биномиального числа. Вес разряда числа больше зе- личины входного кода и в регистре 9 числа сформирован первый нуль.

Теперь на первый вход формирователя 5 со счетчика 2 поступает уменьшенное значение (п-1), равное 4, а состояние другого входа от счетчика 3 не изменяется, т.е. . Таким образом, на выходе формирователя 5 появ4

ляется число . С выхода регистра 1 текущей выборки на первый вход сумматора 7 и на второй вход блока 8 поступает число 3, а с выхода формирователя 5 на второй вход сумматора 7 и первый вход блока 8 - число 1. При этом блок 8 выдает на первый вход блока 6 синхронизации, т.е. на информационный вход триггера 20, сигнал Больше или равно ().

Отрицательный фронт синхросигнала, по входу 12 преобразователя записывает сигнал Больше или равно в ;

5

триггер 20 и открывает элемент ИЛИ- НЕ 21, Таким образом, сигнал с инверсного выхода триггера 20 поступает на третий (управляющий) вход сум.- матора 7 в виде команды Вычитание, т.е. на выходе сумматора 7 имеется разность двоичного кода числа 3 с первого входа и числа 1 с второго 0 входа, т.е. . Одновременно этот сигнал формирует 1 на входе регистра 9 числа и разрешает выборку счетчика 3. Сигнал с прямого выхода триггера 20 запрещает выборку вычитающего счетчика 4.

Положительным фронтом синхросигнала на входе 12 преобразователя в регистр 1 текущей выборки с выхода сумматора 7 записывается число 2. В регистр 9 числа записывается ранее сформированная 1. Одновременно уменьшается на 1 содержимое счетчика 2, т.е. , и счетчика 3, т.е. . Содержимое счетчика 4 остается без изменения, т.е. равно 1. На этом завершается второй этап сравнения (взвешивания) входного двоичного кода и веса следующего разряда биномиального числа. Вес разряда числа 0 меньше и в регистре 9 числа второй сформирована единица.

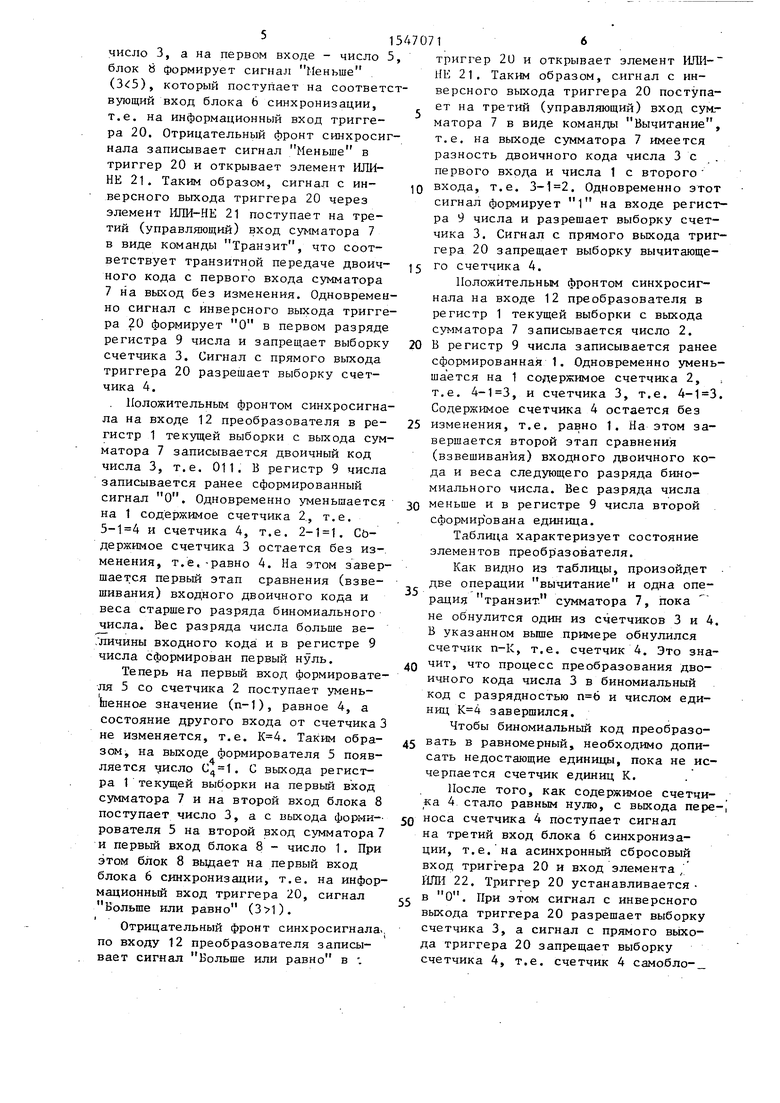

Таблица характеризует состояние элементов преобразователя.

Как видно из таблицы, произойдет две операции вычитание и одна опе0

5

5

рация транзит сумматора 7, пока

0

не обнулится один из счетчиков 3 и 4. В указанном выше примере обнулился счетчик п-К, т.е. счетчик 4. Это значит, что процесс преобразования двоичного кода числа 3 в биномиальный код с разрядностью и числом единиц завершился.

Чтобы биномиальный код преобразо- 5 вать в равномерный, необходимо дописать недостающие единицы, пока не исчерпается счетчик единиц К.

После того, как содержимое счетчика 4 стало равным нулю, с выхода пере-, носа счетчика 4 поступает сигнал на третий вход блока 6 синхронизации, т.е. на асинхронный сбросовый вход триггера 20 и вход элемента , ИЛИ 22. Триггер 20 устанавливается в О. При этом сигнал с инверсного выхода триггера 20 разрешает выборку счетчика 3, а сигнал с прямого выхода триггера 20 запрещает выборку счетчика 4, т.е. счетчик 4 самобло-

0

5

кируется на нулевом содержимом. Таким образом, по каждому синхронизирующему импульсу по входу 12 преобразователя будет уменьшать свое содержимое счетчик 3 и в регистр 9 числа будут последовательно заноситься единицы до тех пор, пока счетчик 3 не обну- лится. Как только содержимое счетчи- |ка 3 станет равным нулю, с его выхода переноса сигнал поступит на второй вход блока 6 синхронизации, т.е. на другой вход элемента ИЛИ 22, Сигналы переноса со счетчиков 3 и 4 откроют элемент ИЛИ 22 и/сигнал с его выхода поступит на шестой выход блока 6 синхронизации, т.е. на выход 19 преобразователя,, свидетельствуя о конце работы преобразователя. ПРИ этом в ое- гистр 9 числа будет числовая комбинация 011101, В регистре 0 числа будет шесть единиц 111,11 1 по числу тактов преобразователя, так как на его вход постоянно заведена единица. Это маска значимости, т.е„ только 6 разрядов выходного кода действительны. Маска значимости соответствует числу разрядов выходного кода.

Таким образом, число тактов работы преобразователя, определяющее его быстродействие, не зависит от веса разрядов исходього двоичного числа и определяется числом разрядов кода с постоянным весом п. За счет поразрядного взвешивания повышается быстродействие преобразователя. Формула изобретения 1. Преобразователь кодов, содержащий регистр текущей выборки, первый вход которого является одноименным входом преобразователя, выход соединен с первым входом сумматора, блок сравнения, первый счетчик, первый вход которого является вторым входом преобразователя, и первый регистр числа, выход которого является первым выходом преобразователя, отличающийся тем, что, с целью повышения быстродействия преобразователя, в него введен второй регистр числа, блок синхронизации, второй и третий счетчики и формирователь кодов, выход которого соединен с вторым входом сумматора и первым входом блока сравнения, выход которого соединен с первым входом блока синхронизации, первый выход КОТОРОГО соединен с первыми входами первого регистра числа и второго счетчика,

5

0

5

0

5

0

5

0

первый выход которого соединен с вторым входом блока синхронизации, второй выход которого соединен с третьим входом сумматора, выход первого счетчика и второй выход второго счетчика соединены с первым и вторым входами формирователя кодов соответственно, второй вход блока сравнения подключен к выходу регистра текущей выборки, выход сумматора соединен с вторым входом регистра текущей выборки, выход третьего счетчика соединен с третьим входом блока синхронизации, третий выход которого соединен с первым входом третьего счетчика, вторые входы второго и третьего счетчиков, четвертый вход блока синхронизации, третий вход регистра текущей выборки, второй вход первого регистра числа и первый вход второго регистра числа подключены к второму входу преобразователя, четвертый вход регистра текущей выборки, вторые входы первого счетчика и второго регистра числа и третьи входы второго и третьего счетчиков и первого регистра числа объединены и являются третьим входом преобразователя, третий вход первого счетчика и четвертые входы второго и третьего счетчиков являются соответственно четвертым - шестым входами преобразователя, выход второго регистра числа и четвертый выход блока синхронизации являются вторым и третьим выходами преобразователя соответственно. 2. Преобразователь по п. отличающийся тем, что блок синхронизации содержит триггер, элемент ИЛИ и элемент ИЛИ-НЕ, первые входы триггера и элемента ИЛИ объединены и являются вторым входом блока синхронизации, инверсный выход триггера соединен с первым входом элемента ИЛИ-НЕ и является первым выходом блока синхронизации, вторые входы триггера и элемента ИЛИ-НЕ объединены и являются четвертым входом блока синхронизации, третий вход триггера и второй вход элемента ИЛИ объединены и являются третьим входом блока синхронизации, четвертый вход триггера является первым входом блока синхронизации, выход элемента ИЛИ-НЕ, прямой выход триггера и выход элемента ИЛИ являются соответственно вторым, третьим и четвертый: выходами блока синхронизации.

ZW

гт %№

25(3)

21

2ffM

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в системах дискретной обработки и передачи информации в качестве устройства кодирования - декодирования информации, использующего равновесные коды. Цель изобретения - повышение быстродействия преобразователя. Преобразователь кодов содержит регистр 1 текущей выборки, первый - третий счетчики 2-4, формирователь 5 кодов, блок 6 синхронизации, сумматор 7, блок 8 сравнения и первый и второй регистры 9, 10 числа, первый - шестой входы 11-16 и первый - третий выходы 17-19. Блок 6 синхронизации содержит триггер, элемент ИЛИ-НЕ и элемент ИЛИ, первый - четвертый входы и первый - четвертый выходы. 1 з.п. ф-лы, 2 ил.

22

30(f)

Авторы

Даты

1990-02-28—Публикация

1988-06-06—Подача