элемента И соединен с S-входом перво- 2Q но объединены и являются входом дего триггера, прямой выход которого соединен с первым входом управления второго коммутатора, инверсный выход первого триггера соединен с первым входом третьего элемента ИЛИ, выход 25 которого соединен с первым и вторым входами третьего коммутатора и вторым входом третьего элемента И, выход которого соединен с установочным входом регистра и является вторым выходом 30 преобразователя, выход первого элемента ИЛИ соединен с S-входом второго триггера, прямой выход третьего триггера соединен с вторым входом второго

шифратора.

3. Преобразователь по п. 1, отличающийся тем, что блок регистровых признаков выполнен на эл ментах ИЛИ, триггерах и элементах И, выход первого элемента И соединен с S-входом первого триггера и первыми входами первого и второго элементов ИЛИ, выходы которых соединены с R-входами соответственно второго и третьего триггеров, выход второго элемента И соединен с S-входом второго триггера, вторым входом второго

шифратора.

3. Преобразователь по п. 1, отличающийся тем, что блок регистровых признаков выполнен на элментах ИЛИ, триггерах и элементах И, выход первого элемента И соединен с S-входом первого триггера и первыми входами первого и второго элементов ИЛИ, выходы которых соединены с R-входами соответственно второго и третьего триггеров, выход второго элемента И соединен с S-входом второго триггера, вторым входом второго

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для приема и обработки информации | 1987 |

|

SU1444856A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444782A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для преобразования последовательныхМНОгОРЕгиСТРОВыХ КОдОВ B пАРАллЕльНыЕ СКОНТРОлЕМ | 1979 |

|

SU840877A1 |

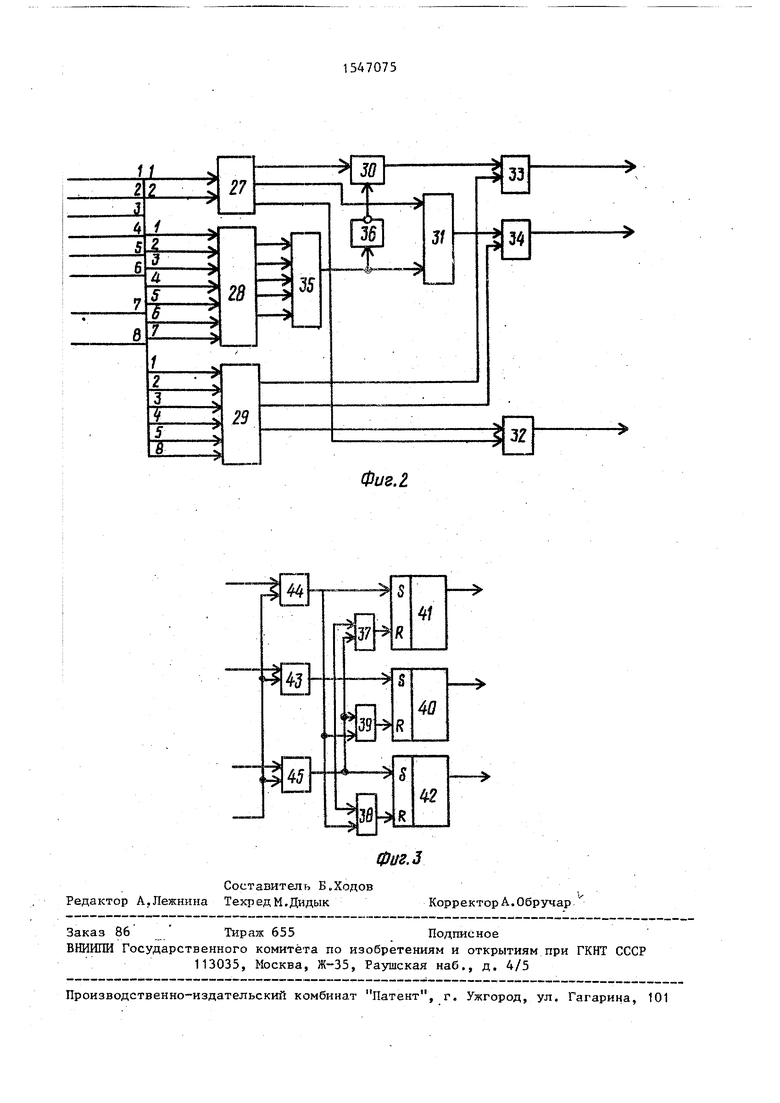

Изобретение относится к вычислительной технике и может быть использовано в устройствах для передачи данных. Изобретение позволяет проводить, кроме прямого преобразования безрегистровых кодов в многорегистровые, также и обратное преобразование многорегистровых кодов в безрегистровые, чем обеспечивается расширение области использования преобразователя кодов. Преобразователь кодов содержит генератор 1 импульсов, элементы И 2-5, элементы ИЛИ 6,7 и 8, триггеры 9,10 и 11, коммутаторы 12,18 и 19, регистр 13, дешифратор 14, блок 15 сравнения, элемент НЕ 16, распределитель 17 импульсов, блок 20 памяти и блок 21 регистровых признаков. Дешифратор 14 содержит формирователи сигналов, элемент И, элементы ИЛИ и элемент НЕ. Блок 21 регистровых признаков содержит элементы ИЛИ, триггеры и элементы И. 2 з.п. ф-лы, 3 ил.

элемента ИЛИ и вторым входом управле- ,с элемента ИЛИ и первым входом третьего

ния второго коммутатора, инверсный выход третьего триггера соединен с вторым входом третьего элемента ИЛИ и первым и вторым входами управления

элемента ИЛИ, выход которого соединен с R-входом первого триггера, выход третьего элемента И соединен с S-входом третьего триггера и вторыми

первого коммутатора, S и R-входы тре- 0 входами первого и третьего элементов

ИЛИ, первые входы первого, второго и третьего элементов И являются соответственно первым, вторым и третьим входами блока, вторые входы первого,

тьего триггера являются соответственно первым и вторым входами управления преобразователя.

динены и являются четвертым входом блока, выходы первого, второго и тре тьего триггеров являются соответственно первым, вторым и третьим выход

соединены с первыми входами соответст-jQ ми блока.

элемента ИЛИ, выход которого соединен с R-входом первого триггера, выход третьего элемента И соединен с S-входом третьего триггера и вторыми

второго и третьего элементов И объ-

динены и являются четвертым входом блока, выходы первого, второго и третьего триггеров являются соответственно первым, вторым и третьим выходаСоставитель Б„Ходов Редактор А.Лежнина ТехредМ.Дидык

Фив. 2

фиг.З

Корректор А. Обручар

Авторы

Даты

1990-02-28—Публикация

1987-08-18—Подача