Фиг.1

315

Изобретение относится к электросвязи и может быть использовано в системах передачи цифровой информации.

Целью изобретения является повышение достоверности устройства.

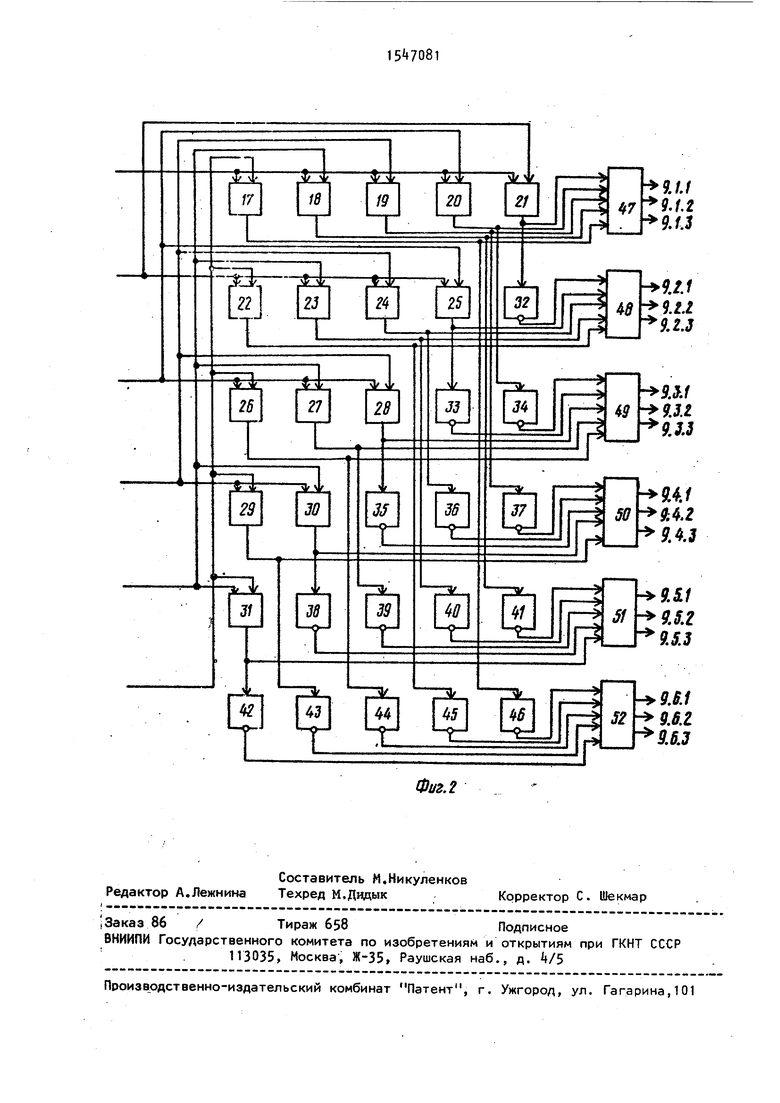

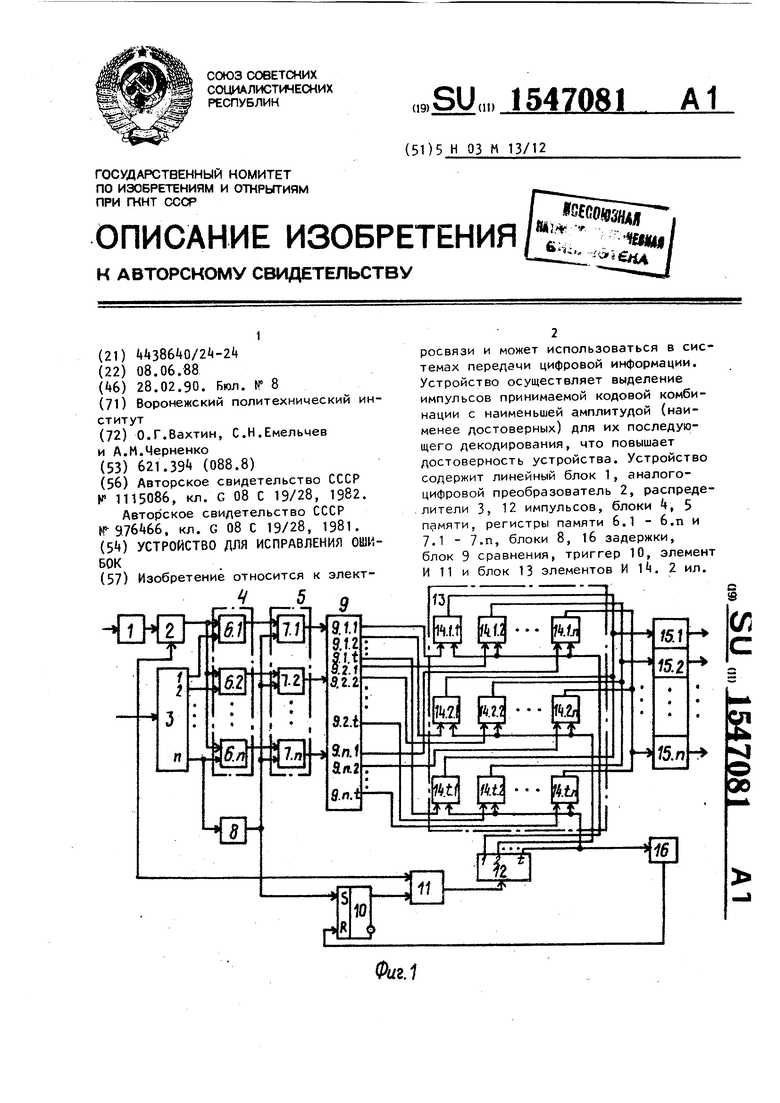

На фиг.1 изображена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока сравнения.

Устройство содержит (фиг.1) линейный блок t, аналого-цифровой преобразователь 2, первый распределитель 3 импульсов, пе.рвый и второй блоки Ь и 5 памяти, выполненные на регистрах 6 и 7 памяти, первый блок 8 задержки, блок 9 сравнения, триггер 10, элемент И 11, второй распределитель 12 импульсов, блок(матрица) 13 элементов И 1, формирователи 15 импульсов и второй блок 16 задержки .

Блок сравнения содержит (фиг.2) элементы 17 - ЗТ сравнения (выделения большего числа), элементы НЕ 32- 46 дешифраторы 7 - 52.

Устройство работает следующим образом.

На информационный вход устройства поступает аналоговое напряжение с выхода приемника двоичных сигналов, а на управляющий вход устройства подаются импульсы управления с выхода генератора тактовых импульсов первой решающей схемы приемника двоичных сигналов.

Аналоговое напряжение поступает на вход блока 1, в котором биполярное напряжение преобразуется в од- нополярное, после чего с выхода блока 1 попадает на информационный вход преобразователя 2, к управляющему входу которого подключен выход тактового генератора приемника двоичных сигналов. Передний фронт тактового импульса, формирующего очередной символ кодовой комбинации, воздействуя на управляющий вход преобразователя 2, преобразует аналоговое напряжение в цифровую форму. Кодовая комбинация соответствующего уровня аналогового сигнала поступает на информационные входы регистров 6, число которых равно числу символов кодовой комбинации сообщения. На управляющие входы регистров 6 поступаю импульсы с выходов первого распределителя 3 импульсов, на вход которого

5

0

5

0

5

0

5

0

5

подаются тактовые импульсы. Тактовый импульс, формирующий первый символ кодовой комбинации сообщения, поступает на первый выход распределителя 3 импульсов. Задний фронт импульса на первом выходе распределителя 3 позволяет записать информацию с выхода преобразователя 2 в регистр 6.1. Тактовый импульс, формирующий второй символ комбинации, передним фронтом воздействует на преобразователь 2, что позволяет на его выходе зафиксировать уровень сигнала, соответствующий моменту действия переднего фронта тактового импульса, а задний фронт второго тактового импульса, поступившего на второй выход распределителя 3, осуществляет запись этой информации в регистр 6.2. Тактовый импульс, формирующий последний символ комбинации, запишет информацию об уровне последнего символа в регистр 6.п. Тактовый импульс последнего символа является управляющим импульсом записи информации в регистры 7.1 - 7.п. Этот импульс с последнего выхода распределителя 3 задерживается в блоке 8 на время, большее длительности тактового импульса, но меньшее периода следования тактовых импульсов, что позволяет переписать информацию из регистров 6 в регистры 7 до появления тактового импульса, формирующего первый символ последующей кодовой комбинации сообщения.

Значения уровней напряжения символов комбинации, записанные в регистрах 7, поступают на входы блока 9 сравнения, в котором значения уровней сравниваются попарно между собой. На выходах 9.1.1 - 9.1.t формируется информация об относительном значении уровня, хранящегося в регистре 7.1, на выходах 9.2.1 - 9.2.t - информация о значении уровня, хранящегося в регистре 7.2, и т.д. Появление логической единицы на одном из выходов 6.1.1, 6.2.1, ..., 6.п.1 указывает на самое малое значение уровня символа, хранящегося в соответствующем регистре. Сигнал логической единицы на одном из выходов 9.1.2, 9.2.2, ..., 9.п.2 указывает на второе по малости значение уровня символа, а сигнал логической единицы на выходах 9.1.t, 9.2.t, ..., 9.n.t - на t-e по малости значение уровня. Так, если имеют место сигналы логической

единицы на выходах 9.1.2, 9.2.t, 9.п.1, это означает, что в регистре 7.п хранится самое малое значение уровня, а в регистре 7.2 - t-e по малости значение уровня.

Исходя из положения, что вероятность регистрации искаженного символа тем больше, чем меньше абсолютное значение уровня напряжения на выходе приемника двоичных сигналов, выбран алгоритм приоритетного анализа символов в блоке формирования полинома ошибок (БФПО) путем анализа символов кодовой комбинации, уровни которых наиболее близки к нулевому. Так, в указанном выше примере в первую строку матрицы памяти БФПО должет быть помещен последний символ кодовой комбинации, во вторую строку - первый символ, а в t-ю строку - второй символ. Для записи в матрицу памяти БФПО информации в указанной последовательности необходимо, чтобы управляющие импульсы из формирователей 15 в буферный накопитель поступали в той же самой последовательности.

В указанном примере сигналы логической единицы имеют место на входах элементов 14.1.п, 14.2.1, ..., 14.t.2. Тактовый импульс с последнего выхода распределителя 3 через блок 8 задержки опрокидывает триггер 10, сигнал логической единицы с прямого выхода которого поступает на вход элемента И 11. Тактовые импульсы через элемент И 11 подаются на вход распределителя 12 импульсов, первый тактовый импульс появляется на первом выходе распределителя 12, а следовательно, и на вторых входах элементов И 14 первой строки матрицы 13. Поскольку в данном случае в первой строке матрицы 13 сигнал логической единицы присутствует только на входе элемента И 14.1.п, то импульс с первого выхода распределителя 12 формирует сигнал логической единицы на выходе элемента И 14.1.п, который воздействует на n-й формирователь 15, сигнал с выхода которого указывает , что в матрицу памяти БФПО в первую строку должен быть записан n-й символ кодовой комбинации сообщения. Тактовый импульс, формирующий второй символ последующей кодовой комбинации, поступает на второй выход распределителя 12 импульсов, что приводит к появлению сигнала

0

0

логической единицы на выходе одного из элементов И 14.2.1 второй строки матрицы 13. Этот сигнал воздействует на первый формирователь 15, что приводит к записи во вторую строку матрицы памяти БФПО первого символа кодовой комбинации сообщения. Импульс напряжения с t-ro выхода распределителя 12 импульсов формирует сигнал логической единицы, обеспечивающий запись в t-ю строку матрицы памяти БФПО второго символа кодовой комбинации сообщения. Поскольку txn, то 5 запись информации в матрицу памяти БФПО осуществится раньше, чем заполнится блок 6 памяти значениями символов следующей кодовой комбинации. Импульс напряжения с последнего выхода распределителя 12 через блок 16 задержки поступает на вход триггера 10, опрокидывая его и закрывая элемент И 11. Устройство вновь готово к анализу следующей кодовой 5 комбинации.

На фиг.2 приведена функциональная схема блока 9 сравнения для случая и .

Значения уровней символов кодовой Q комбинации сообщения, хранящиеся в двоичной форме s регистрах 7.1 - 7.6, сравниваются между собой. Для этого значения уровней символов попарно поступают на входы элементов выделения большего числа. 5 Если в таких элементах 17 31 на первые (левые) входы подать число А, а на вторые входы (правые) - число В, то на их выходах появится сигнал логической единицы при условии . В противном случае на выходе имеет место логический ноль. В элементах 17-21 происходит сравнение значения уровня первого символа комбинации со значениями уровней всех остальных символов. В элементах 22 - 25 сравниваются уровни второго символа с уровнями третьего и т.д. символов. Результат сравнения уровня второго символа с первым представляет собой инверсию (элемент НЕ 32) результата сравнения уровня первого символа с вторым в элементе 21. Результаты сравнения уровня первого символа комбинации с уровнями остальных 5 символов поступают на входы дешифратора 47, результаты сравнения уровня второго символа с уровнями остальных символов - на входы дешифра0

5

Тора 8 и т.д. Число логических единиц на входах дешифраторов 7 - 52 Определяет место каждого символа в последовательности по достоверности приема. Если на входах какого-либо из дешифраторов 7 - 52 имеют место |олько логические нули, то это озна8

чает, что достоверность приема соот- нетствующего символа самая малая. юлее высокой достоверностью обладает символ, результат сравнения которого содержит одну логическую единицу. Самая высокая достоверность у то го символа, у которого результат сравнения содержит все единицы. Постольку интерес представляют только t наименее достоверных символов (в данном случае ), то число выходов каждого из дешифраторов А - 52 равно t.

Применение предлагаемого устройства позволяет увеличить достоверность Приема кодовых комбинаций сообщения, поскольку в каналах с замираниями Исключается ситуация переполнения Счетчика стираний, которая приводит к запрету анализа ошибок в кодовой Комбинации.

формула изобретения

Устройство для исправления ошибок, (содержащее линейный блок, вход которого является информационным входом

1C

2С

30

введены распределители импульсов формирователи импульсов7, блоки з жки, блок сравнения, блок элемен И, триггер и элемент И, первый в которого объединен с управляющим дом аналого-цифрового преобразов ля, входом первого распределител импульсов и является управляющим дом устройства, выход аналого-ци вого преобразователя соединен с формационными входами первого бл памяти, выходы которого соединен одноименными информационными вхо второго блока памяти, выходы кот рого соединены с одноименными вх дами блока сравнения, выходы кот го соединены с соответствующими выми входами блока элементов И, ходы первого распределителя импу соединены с одноименными управля ми входами первого блока памяти, и выход первого блока задержки п ключены соответственно к последн выходу первого распределителя им сов и к управляющим входам второ блока памяти и входу установки в триггера, выход триггера соедине вторым входом элемента И, выход рого соединен с входом второго р пределителя импульсов, выходы ко рого соединены с соответствующим вторыми входами блока элементов выходы которого соединены с вход ми одноименных формирователей им

устройства, выход линейного блока пульсов, выходы которых являются

8

C

С

0

введены распределители импульсов, формирователи импульсов7, блоки задержки, блок сравнения, блок элементов И, триггер и элемент И, первый вход которого объединен с управляющим входом аналого-цифрового преобразователя, входом первого распределителя импульсов и является управляющим входом устройства, выход аналого-цифрового преобразователя соединен с информационными входами первого блока памяти, выходы которого соединены с одноименными информационными входами второго блока памяти, выходы которого соединены с одноименными входами блока сравнения, выходы которого соединены с соответствующими первыми входами блока элементов И, выходы первого распределителя импульсов соединены с одноименными управлявшими входами первого блока памяти, ЕХОД и выход первого блока задержки подключены соответственно к последнему выходу первого распределителя импульсов и к управляющим входам второго блока памяти и входу установки в 1 триггера, выход триггера соединен с вторым входом элемента И, выход которого соединен с входом второго распределителя импульсов, выходы которого соединены с соответствующими вторыми входами блока элементов И,, выходы которого соединены с входами одноименных формирователей им5 пульсов, выходы которых являются

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для моделирования канала связи | 1983 |

|

SU1132294A1 |

| Устройство для тренировки памяти обучаемого | 1987 |

|

SU1545236A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для коммутации информационных каналов | 1981 |

|

SU1003123A1 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1259285A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| НЕЧЕТКИЙ ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1995 |

|

RU2110090C1 |

Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации. Устройство осуществляет выделение импульсов принимаемой кодовой комбинации с наименьшей амплитудой (наименее достоверных) для их последующего декодирования, что повышает достоверность устройства. Устройство содержит линейный блок 1, аналого-цифровой преобразователь 2, распределители 3,12 импульсов, блоки 4,5 памяти, регистры памяти 6.1-6.N и 7.1-7.N, блоки 8,16 задержки, блок 9 сравнения, триггер 10, элемент И 11 и блок 13 элементов И 14. 2 ил.

динен с информационным входом аналого-цифрового преобразователя, первый и второй блоки памяти, отличающееся тем, что, с целью повышения достоверности устройства, в него

выходами устройства, вход и выход второго блока задержки подключены соответственно к последнему выходу второго распределителя импульсов и входу установки в 0й триггера.

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1115086A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для приема и передачи избыточных сигналов | 1981 |

|

SU976466A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-02-28—Публикация

1988-06-08—Подача