Изобретение относится к вычисли- тельной технике, в частности к аппаратуре контроля логических вычислительных машин, и может быть использовано в электронике для контроля ло- гических микросхем средней и большей степени интеграции, а также в составе автоматических комплексов и автоматизированных систем управления производства ТЭЗов, контроллеров и других л9гических узлов.

Цель изобретения - повьппение достоверности контроля и производительг ности.

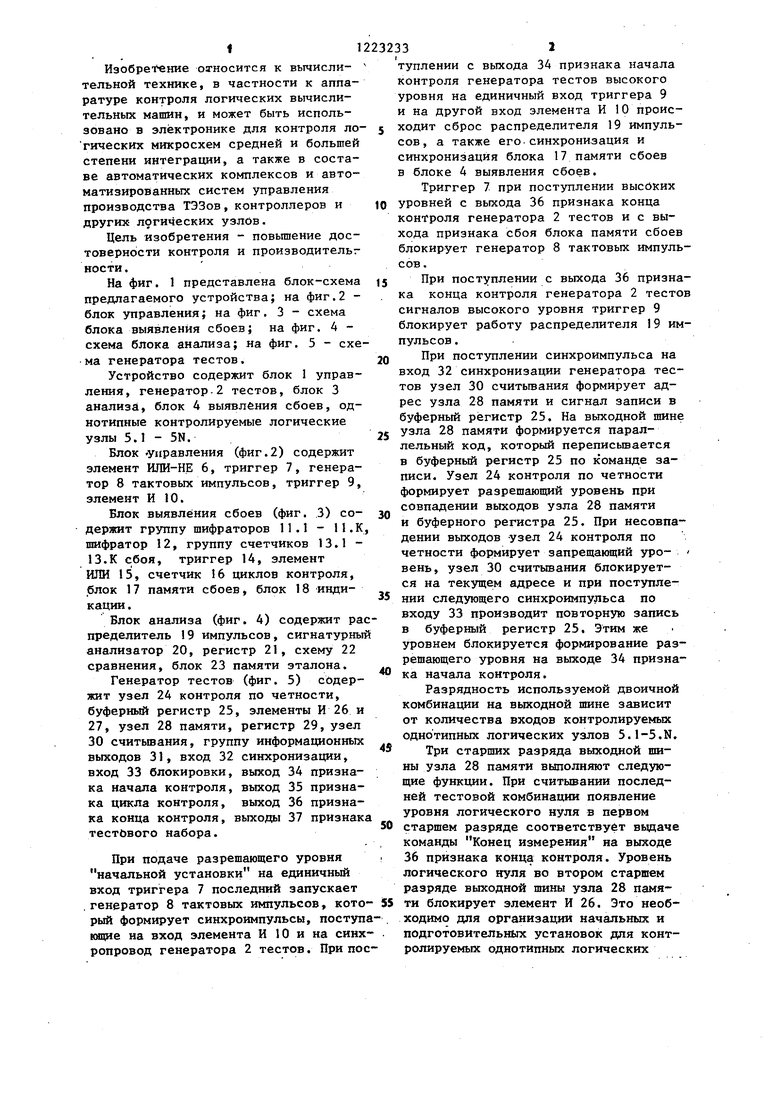

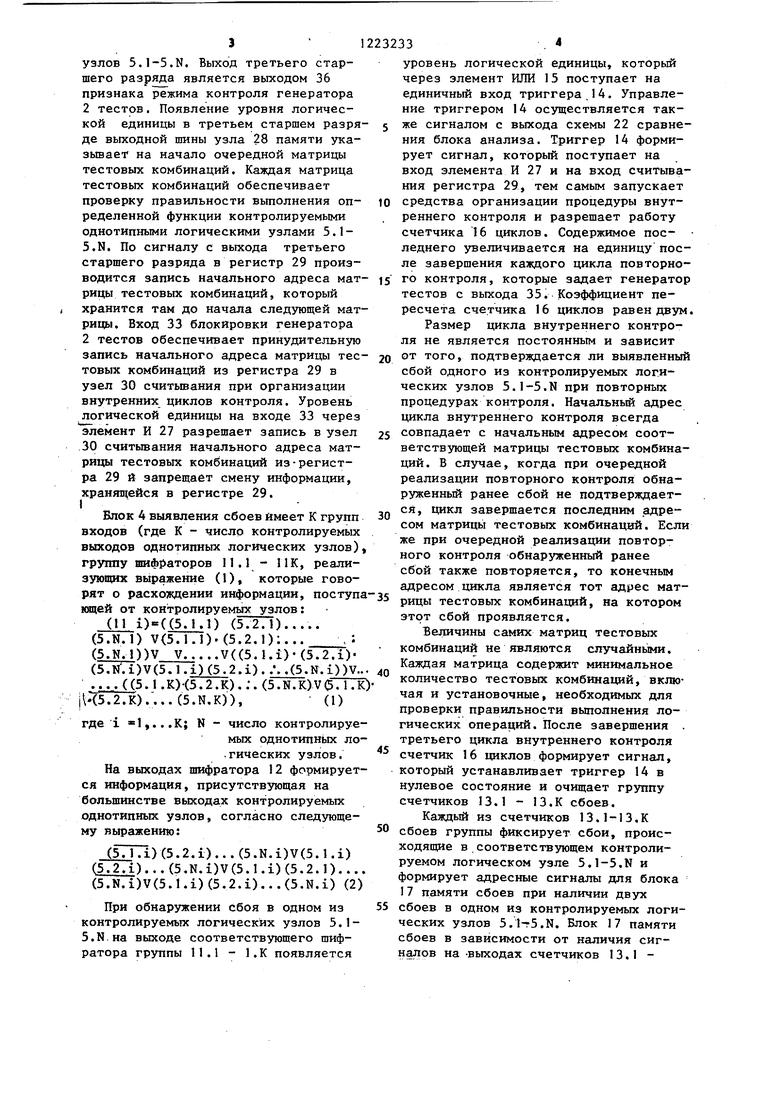

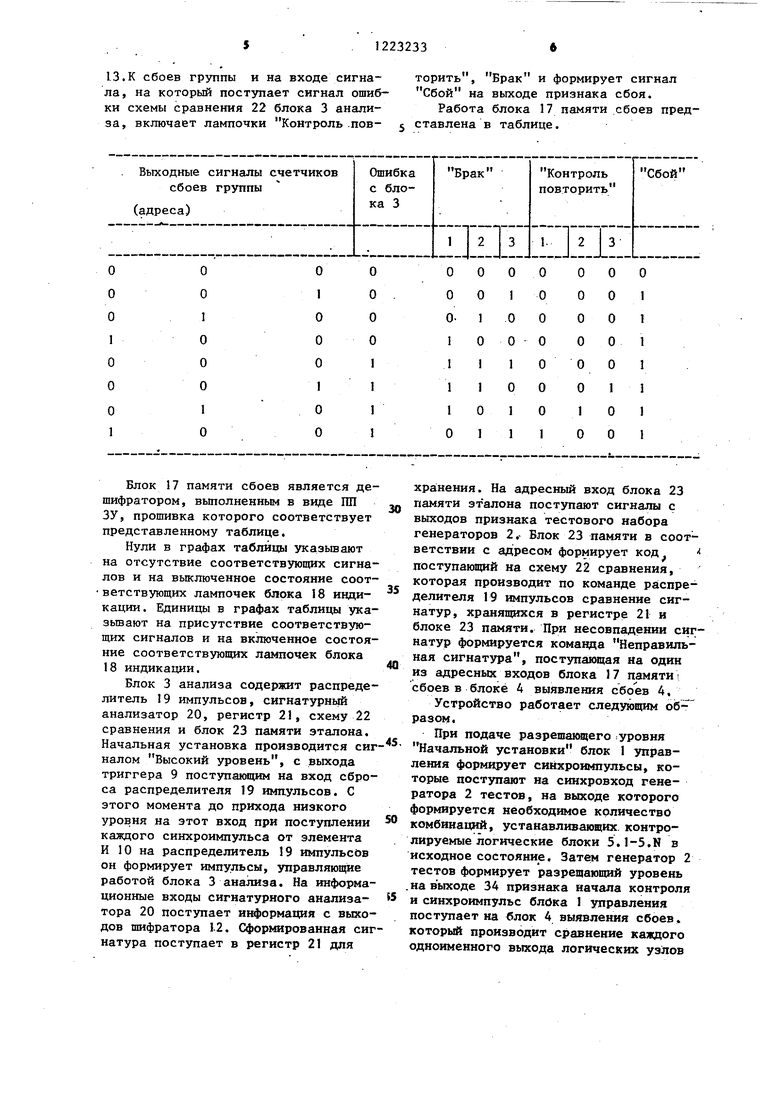

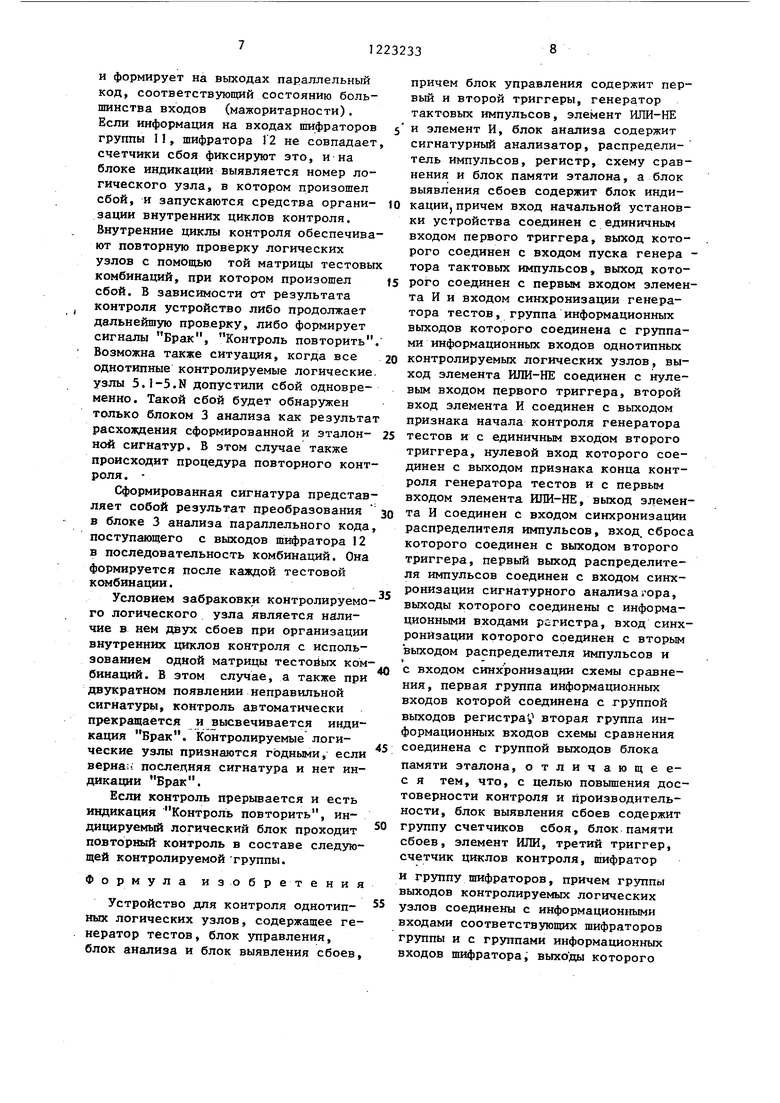

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - блок управления; на фиг. 3 - схема блока выявления сбоев; на фиг. 4 - схема блока анализа; на фиг. 5 - схема генератора тестов.

Устройство содержит блок 1 управления, генератор.2 тестов, блок 3 анализа, блок 4 выявления сбоев, однотипные контролируемые логические узлы 5.1 - 5N.

Блок -управления (фиг.2) содержит элемент Ш1И-НЕ 6, триггер 7, генератор 8 тактовых импульсов, триггер 9, элемент И 10.

Блок выявления сбоев (фиг. 3) содержит группу шифраторов 11.1 - П.К шифратор 12, группу счетчиков 13.1 - 13.К сбоя, триггер 14, элемент ИЛИ 15, счетчик 16 циклов контроля, блок 17 памяти сбоев, блок 18 индикации .

Блок анализа (фиг. 4) содержит рапределитель 19 импульсов, сигнатурны анализатор 20, регистр 21, схему 22 сравнения, блок 23 памяти эталона.

Генератор тестов (фиг. 5) содержит узел 24 контроля по четности, буферный регистр 25, элементы И 26 и 27, узел 28 памяти, регистр 29, узел 30 считывания, группу информационных выходов 31, вход 32 синхронизации, вход 33 блокировки, выход 34 признака начала контроля, выход 35 признака цикла контроля, выход 36 признака конца контроля, выходы 37 признак тестового набора.

При подаче разрешающего уровня начальной установки на единичный вход триггера 7 последний запускает . генератор 8 тактовых импульсов, который формирует синхроимпульсы, поступ кяцие на вход элемента И 10 и на синх ропровод генератора 2 тестов. При поступлении с выхода 34 признака начала контроля генератора тестов высокого уровня на единичный вход триггера 9 и на другой вход элемента И 10 происходит сброс распределителя 19 импульсов, а также его.синхронизация и синхронизация блока 17 памяти сбоев в блоке 4 выявления сбоев.

Триггер 7 при поступлении высйких

уровней с выхода 36 признака конца контроля генератора 2 тестов и с выхода признака сбоя блока памяти сбоев блокирует генератор 8 тактовых импульсов .

При поступлении с выхода 36 признака конца контроля генератора 2 тестов сигналов высокого уровня триггер 9 блокирует работу распределителя 19 импульсов .

При поступлении синхроимпульса на вход 32 синхронизации генератора тестов узел 30 считывания формирует адрес узла 28 памяти и сигнал записи в буферный регистр 25. На выходной шине

узла 28 памяти формируется параллельный код, который переписьшается в буферный регистр 25 по команде записи. Узел 24 контроля по четности формирует разрешающий уровень при совпадении выходов узла 28 памяти и буферного регистра 25. При несовпадении выходов узел 24 контроля по четности формирует запрещакнций уро- - вень, узел 30 считывания блокируется на текущем адресе и при поступлеНИИ следующего синхроимпульса по входу 33 производит повторную запись в буферный регистр 25. Этим же уровнем блокируется формирование разрешающего уровня на выходе 34 признака начала контроля.

Разрядность используемой двоичной комбинации на выходной шине зависит от количества входов контролируемых однотипных логических узлов 5.1-5.N.

Три старпшх разряда выходной шины узла 28 памяти выполняют следующие функции. При считывании последней тестовой комбинации появление уровня логического нуля в первом

старшем разряде соответствует вьщаче команды Конец измерения на выходе

36 признака конца контроля. Уровень логического нуля во втором старшем разряде выходной шины узла 28 памяти блокирует элемент И 26. Это необходимо для организации начальных и подготовительных установок для контролируемых однотипных логических

узлов 5.1-5.N. Выход третьего старшего разряда является выходом 36 признака режима контроля генератора 2 тестов. Появление уровня логической единицы в третьем старшем разряде выходной шины узла 28 памяти ука- зьшает на начало очередной матрицы тестовых комбинаций. Каждая матрица тестовых комбинаций обеспечивает проверку правильности вьтолнения определенной функции контролируемыми однотипными логическими узлами 5.1- 5.N. По сигналу с выхода третьего старшего разряда в регистр 29 производится запись начального адреса матрицы тестовых комбинаций, который хранится там до начала следующей матрицы. Вход 33 блокировки генератора 2 тестов обеспечивает принудительную запись начального адреса матрицы тестовых комбинаций из регистра 29 в узел 30 считьгоания при организации внутренних циклов контроля. Уровень логической единицы на входе 33 через элемент И 27 разрешает запись в узел 30 считывания начального адреса матрицы тестовых комбинаций из-регистра 29 и запрещает смену информации,

храня)ейся в регистре 29. I

Блок 4 выявления сбоев имеет К групп

входов (где К - число контролируемых выходов однотипных логических узлов) группу шиф1)аторов 11.1 - ПК, реализующих выражение (1), которые говорят о расхождении информации, поступа кяцей от контролируемых узлов: (И i)-((5.1.1) (5.2.1).....

(5.N.I) V(5.1.1)(5.2.l):....:

(5.N.1))V VV((5.1.i)-(5.2.1)

(5.N .i)V(5.1 .i)(5.2.i) . .. .(5.N. i))V.. ...... ((5.1.K)-(5.2.K).:.(5.N.K)V(gTT7K

.2.K).... (5.N.K)), (1)

где i ,...K; N - число контролируемых однотипньк ло- гических узлов.

На выходах шифратора 12 формируется информация, присутствующая на большинстве выходах контролируемых однотипных узлов, согласно следующему выражению:

JsTTTi) (3.2. i) .. . (5 .N. i) V(5.1. i)

(5.2.i)...(5.N.i)V(5.1.i)(5.2.1)

(5.N.i)V(5.1.i)(5.2.i)...(5.N.i) (2)

При обнаружении сбоя в одном из контролируемых логических узлов 5.1- 5.N,Ha выходе соответствующего шифратора группы 11.1 - 1.К появляется

уровень логической единицы, который через злемент ИЛИ 15 поступает на единичный вход триггера ,14. Управление триггером 14 осуществляется также сигналом с выхода схемы 22 сравнения блока анализа. Триггер 14 формирует сигнал, который поступает на вход элемента И 27 и на вход считывания регистра 29, тем самым запускает

средства организации процедуры внутреннего контроля и разрешает работу счетчика 16 циклов. Содержимое последнего увеличивается на единицу после завершения каждого цикла повторного контроля, которые задает генератор тестов с выхода 35. Коэффициент пересчета счетчика 16 циклов равен двум.

Размер цикла внутреннего контроля не является постоянным и зависит

от того, подтверждается ли выявленный сбой одного из контролируемых логических узлов 5.1-5.N при повторных процедурах контроля. Начальный адрес цикла внутреннего контроля всегда

совпадает с начальным адресом соответствующей матрицы тестовых комбинаций. В случае, когда при очередной реализации повторного контроля обнаруженный ранее сбой не подтверждается, цикл завершается последним адресом матрицы тестовых комбинаций. Если же при очередной реализации повторного контроля обнаруженный ранее сбой также повторяется, то конечным адресом цикла является тот адрес матрицы тестовых комбинаций, на котором этот сбой проявляется.

Величины самих матриц тестовых комбинаций не являются случайнь1ми. Каждая матрица содержит минимальное количество тестовых комбинаций, включая и установочные, необходимых для проверки правильности выполнения логических операций. После завершения . третьего цикла внутреннего контроля

счетчик 16 циклов формирует сигнал, который устанавливает триггер 14 в нулевое состояние и очищает группу счетчиков 13.1 - 13.К сбоев.

Каждый из счетчиков 13.1-13.К

сбоев группы фиксирует сбои, происходящие в соответствующем контролируемом логическом узле 5.1-5.N и формирует адресные сигналы для блока I7 памяти сбоев при наличии двух

сбоев в одном из контролируемых логических узлов 5.1-r5.N. Блок 17 памяти сбоев в зависимости от наличия сигналов на -выходах счетчиков 13.1

13.К сбоев группы и на входе сигнала, на который поступает сигнал ошибки схемы сравнения 22 блока 3 анализа, включает лампочки Контроль .пов

Блок 17 памяти сбоев является дешифратором, выполненным в виде ПП ЗУ, прошивка которого соответствует представленному таблице.

Нули в графах таблицы указьшают на отсутствие соответствующих сигналов и на выключенное состояние соот- ветствующих лампочек блока 18 индикации. Единицы в графах таблицы указьшают на присутствие соответствующих сигналов и на включенное состояние соответствующих лампочек блока 18 индикации.

Блок 3 анализа содержит распределитель 19 импульсов, сигнатурный анализатор 20, регистр 21, схему 22 сравнения и блок 23 памяти эталона. Начальная установка производится сиг налом Высокий уровень, с выхода триггера 9 поступающим на вход сброса распределителя 19 импульсов. С этого момента до прихода низкого уровня на этот вход при поступлении каждого синхроимпульса от элемента И 10 на распределитель 19 импульсов он формирует импульсы, управляющие работой блока 3 анализа. На информационные входы сигнатурного анализатора 20 поступает информация с выходов шифратора 12. Сформированная сигнатура поступает в регистр 21 для

торить, Брак и формирует сигнал Сбой на выходе признака сбоя.

Работа блока 17 памяти сбоев представлена в таблице.

хранения. На адресный вход блока 23 памяти эт алона поступают сигналы с выходов признака тестового набора генераторов 2.- Блок 23 памяти в соответствии с адресом формирует код поступающий на схему 22 сравнения, которая производит по команде paicnpe- делителя 19 импульсов сравнение сигнатур, храиящихся в регистре 21 и блоке 23 памяти. При несовпадении сигнатур формируется комавда Неправильная сигнатура, поступающая на один из адресных входов блока 17 памяти сбоев в блоке 4 выявления сбоев 4.

Устройство работает следующим образом.

При подаче разрешаш(его уровня Начальной установки блок 1 управления формирует синхроимпульсы, которые поступают на сиихровход генератора 2 тестов, на выходе которого формируется необходимое количество комбинаций, устанавливающих, контролируемые логические блоки 5.1-5.N в исходное состояние. Затем генератор 2 тестов формирует разрешающий уровень .нав ыходе 34 признака начала контроля и синхроимпульс блока 1 здтравления поступает на блок 4 выявления сбоев, который производит сравнение каждого одноименного выхода логических узлов

и формирует на выходах параллельный код, соответствующий состоянию большинства входов (мажоритарноети). Если информация на входах шифраторов 5 группы I1, шифратора Г2 не совпадает, счетчики сбоя фиксируют это, и на блоке индикации выявляется номер логического узла, в котором произошел сбой, и запускаются средства органи- ю зации внутренних циклов контроля. Внутренние циклы контроля обеспечивают повторную проверку логических узлов с помощью той матрицы тестовых комбинаций, при котором произошел fs сбой. В зависимости опт результата контроля устройство либо продолжает дальнейшую проверку, либо формирует сигналы Брак, Контроль повторить, Возможна также ситуация, когда все 20 однотипные контролируемые логические, узлы 5.1-5.N допустили сбой одновременно. Такой сбой будет обнаружен только блоком 3 анализа как результат расхождения сформированной и эталон- 25 ной сигнатур. В этом случае также происходит процедура повторного контроля.

Сформированная сигнатура представляет собой результат преобразования зо в блоке 3 анализа параллельного кода, поступающего с выходов шифратора 12 в последовательность комбинаций. Она формируется после каждой тестовой комбинации.

Условием забраковки контролируемого логического узла является наличие в нем двух сбоев при организации внутренних циклов контроля с использованием одной матрицы тестойьгх комбинаций. В этом случае, а также при двукратном появлении неправильной сигнатуры, контроль автоматически прекращается и высвечивается индикация Брак. Контролируемые логические узлы признаются годными, если верна: ; последняя сигнатура и нет индикации Брак,

Если контроль прерывается и есть индикация Контроль повторить, индицируемый логический блок проходит повторный контроль в составе следующей контролируемой труппы.

Формула изобретения

Устройство для контроля однотип- 5 ных логических узлов, содержащее генератор тестов, блок управления, блок анализа и блок выявления сбоев.

40

45

5 ю fs 20 25

зо

5

0

5

причем блок управления содержит первый и второй триггеры, генератор тактовых импульсов, элемент ИЛИ-НЕ и элемент И, блок анализа содержит сигнатурный анализатор, распределитель импульсов, регистр, схему сравнения и блок памяти эталона, а блок выявления сбоев содержит блок индикации, причем вход начальной установки устройства соединен с единичным входом первого триггера, выход которого соединен с входом пуска генера - тора тактовых импульсов, выход которого соединен с первьм входом элемента И и входом синхронизации генератора тестов, группа информационных выходов которого соединена с группами информационных входов однотипных контролируемых логических узлов, выход элемента ИПИ-НЕ соединен с нулевым входом первого триггера, второй вход элемента И соединен с выходом признака начала контроля генератора тестов и с единичным входом второго триггера, нулевой вход которого соединен с выходом признака конца контроля генератора тестов и с первым входом элемента ИЛИ-НЕ, выход элемента И соединен с входом синхронизации распределителя импульсов, вход, сброса которого соединен с выходом второго триггера, первый выход распределителя импульсов соединен с входом синхронизации сигнатурного анализатора, выходы которого соединены с информационными входами регистра, вход синхронизации которого соединен с вторым выходом распределителя импульсов и с входом синхронизации схемы сравнения, первая группа информационных входов которой соединена с группой выходов регистра вторая группа информационных входов схемы сравнения соединена с группой выходов блока памяти эталона, отличающее- с я тем, что, с целью повышения достоверности контроля и производительности, блок выявления сбоев содержит группу счетчиков сбоя, блок памяти сбоев, элемент ИЛИ, третий триггер, счетчик циклов контроля, шифратор

и группу шифраторов, причем группы выходов контролируемых логических узлов соединены с информационными входами соответствующих шифраторов группы и с группами информационных входов шифратора, выхода которого

соединены с информационными входами сигнатурного анализатора, выходы шифраторов группы соединены с входами элемента ИЛИ и со счетными входами соответствующих счетчиков сбоев группы, входы сбросе а которых соединены с выходом переполнения счетчика циклов контроля и с нулевым входом третьего триггера, единичный вход которого соединен с выходом элемента ИЛИ, выход трёЛего триггера Соединен с входом разрешения счетчика циклов контроля и с входом, разрешения генератора тестов, разрядные выходы счетчи- ков сбоев группы и выход схемы сравнения соединены с адресными входами блока памяти сбоев, выход признака сбоя которого соединен с вторым

Нач. уст

входом элемента ИЛИ-НЕ, вход синхронизации блока памяти сбоев соединен с выходом элемента И, группа выходов признаков номеров контролируемых однотипных логических узлов блока памяти сбоев соединена с первой группой информационных вход9в блока индикации, вторая группа информационных входов которого соединена с группой выходов признаков сбоев однотипных контролируемыхлогических узлов блока памяти сбоев, выход признака тестового набора генератора тестов соединен с адресным входом блока памяти эталона, выход признака цикла контроля генератора тестов соединен со счетным входом счетчика циклов контроля.

5.1

5. г

ff.H

фиг.1

f(j/i.H/IH-HfB

фиг.З

От 37

От luuippam. it

. фаг.5 ВНИИПИ Заказ 1715/52Тираж 671

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

гз

Н

го

ттриг.9 ffmyjr./ff фагЛ

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при тестовом диагностировании. Цель изобретения ,повьшение достоверности контроля и производительности. Устройство содерIжит блок управления, генератор тестов, блок.анализа и блок выявления . сбоев. При выявлении сбоя в одном из .контролируемых однотипных логических узлов этот сбой фиксируется блоком выявления сбоев, который осуществляет идентификацию номера отказавшего узла и типа ошибки. При этом осуществляется повторный цикл контроля для выявления подтверждения сбоя отказавшего узла. Если при очередной реализации повторного контроля обнаруженный сбой подтверждается, то конечным адресом цикла контроля будет адрес той тестовой комбинации, на которой этот сбой проявился. При-одновременном сбое во всех узлах этот сбой обнаруживает блок анализа, ра- ботающий по принципу сигнального анализатора. При этом опять происходит повторный контроль. Условием забра- ковки узлов является наличие двух сбоев при организациях циклов конт РОЛЯ. 5 ИЛг i сл

| Установка для очистки наружных поверхностей железобетонных изделий | 1977 |

|

SU683912A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-07—Публикация

1984-10-10—Подача