узел со ;ержит аналого-цифровой преобразователь, счетчик, регистры, элемент ИЛИ, блок построения вариационного ряда и дешифратор, выход аналого-цифрового преобразователя соединен с первым входом элемента ИЛИ, выходы счетчика соединены с соответствующими входами первого регистра, выход которого соединен с вторым входом элемента ИЛИ, выход элемента ИЛИ соединен с первым входом блока построю- НИН вариациойного ряда, выход которого соединен с входом второго регистра, выходы которого- соединены с соответствующими входами дешифратора, вход аналого-цифрового преобразователя и выход дешифратора являются соответственно первым входом и выходом ранжиру1сщего узла, вход счетчика, второй и третий входы блока построения вариационного ряда являются соответственно вторьтм, третьим и четвертым входами ранжирукнцего узла.

3. Устройство по n.t, о т л и ч а ю щ е е с я тем, что блок построе ния вариационного ряда содержит регистр и каналы обработки информации, каждый из которых состоит из ключей, регистров, элементов ИЛИ и элемента сравнения, выход первого элемента ИЛИ соединен с первым входом первого ключа, выход которого соединен с первым входом первого регистра, первый выход которого соединен с первым входом второго элемента ИЛИ, вторые выходыс соответствующими первыми входами элемента сравнения, первый выход

которого соединен с первым входом второго ключа, второй выход - с первым входом третьего ключа, первые выходы второго регистра соединены с соответствующими вторыми входами элемента сравнения, второй выход - с вторыми входами второго и третьего ключей, выходы второго элемента ИЛИ и tpeTbero ключа каждого предьщущего канала обработки информации соединены соответственно с вторым входом первого регистра и входом второго регистра каждого последующего канала обработки информации, выходы первого, второго ключей и первый выход элемента сравнения каждого последукидего канала обработки информации соединены соот ветственно с вторыми входами первого ключа, второго элемента ИЛИ и первым входом первого.элемента ИЛИ каждого предьщущего канала обработки информации, выход второго-элемента ИЛИ последнего канала обработки информации соединен с первым входом регистра, вход второго регистра первого канала обработки информации и выход регистра являются соответственно первым входом и выходом блока, построения вариационного ряда, вторые входы первых элементов ИЛИ канала обработки информации объединены и являются вторым входом блока построения вариационного ряда, второй вход дервого ключа последнего канала обработки информации объединен с вторым входом регистра и является третьим входом блока построения вариа- ционного ряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточной информации | 1983 |

|

SU1101873A1 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

| Устройство для приема избыточной информации | 1988 |

|

SU1557578A2 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU978373A1 |

| Устройство приема и обработки избыточных кодов | 1990 |

|

SU1823143A1 |

1. УСТРОЙСТВО ДЛЯ ПРИЕМА И ОБРАБОТКИ ИЗБЫТОЧНЫХ СИГНАЛОВ, содержащее приемник, вход которого является первым входом устройства, выход приемника соединен с первым входом первого блока памяти, пороговый блок, декодер, первый регистр и .второй блок памяти, отличающееся тем, что, с целью повьшения помехоустойчивости устройства, в него введены третий блок памяти, второй и третий регистры, ключи, генератор импульсов, счетчики, блоки сравнения, ранжирующий узел, элемент И и коммутатор, выход первого блока памяти соединен с первым входом ранжирующего узла и входом порогового блока, выход порогового блока соединен с входом первого счетчика, первый выход которого соединен с входом первого регистра, выходы первого регистра соединены с соответствующими первыми входами второго регистра, выход которого соединен с первым входом третьего регистра, выход третьего регистра соединен с входом декодера и первым входом первого ключа. выход первого .ключа является выходом устройства, выход декодера соединен с вторыми входами первого ключа пёрво-, го блока памяти и с первыми входами второго счетчика и генератора импульсов, второй выход первого счетчика соединен с вторым входом генератора импульсов, выход которого соединен с входом третьего счетчика, первый выход которого соединен с первым входом второго блока памяти, первый выход второго блока памяти соединен через четвертый счетчик с первым входом первого блока сравнения, второй выход третьего счетчика соединен с вторым 9 входом второго счетчика, выход которого соединен с вторым входом первого бпока сравнения, выход первого блока сравнения соединен с первыми входами второго ключа, третьего блока памяти § и вторым входом второго блока памяти, выход второго блока памяти соединен . с входом второго ключа, выход которого соединен с первым входом коммутатора, второй, третий и четвер:д тый входы ранжирукяцего узла являются о. соответственно вторым, третьим и чет90 9 вертым входами устройства, выход жирующего узла соединен с вторым входом третьего блока памяти, выкод которого соединен с вторым входом коммутатора, выходы коммутатора соединены с входами соот1зетствующих вторых . блоков сравнения, первые выходы которых соединены с вторыми входами третьего регистра, а вторые выходы - с соответствующими входами элемента И, выход которого соединен с вторым входом второго регистра. 2. Устройство по П.1, о т л и ч а ю щ е е с я тем, что,ранжир Ю11р1й

Изобретение относится к электросвязи и мозкет быть использовано в приемной аппаратуре систем передачи информации.

Известно устройство для приема 5 избыточных сигналов, содержащее при-, емник, пороговый блок и декодер .

Недостатком известного устройства является низкая помехоустойчивость, поскольку в нем не учитывается инфор-О мация об амплитуде символов аналогового сигнала, полученных на выходе приемника.

Наиболее близким по технической сущности к предлагаемому является устройство для приема и обработки избыточных сигналов, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входами первого блока памяти, первого порогового блока и первым, входом вычитателя, выход первого блока памяти соединен с первым входом блока управления выдачей информации, выходы и вторые входы которого соединены соответственно с первыми входами и первыми выходами блока регистров, выход первого порогового блока соединен с первым входом декодера, вторым входом вычитателя и входом регистра, выход вычитателя соединен с входом второго блока памяти, вьгходы которого соединены с соответствующими первыми входами блока усилителей, первые выходы и второй вход которого соединены соответственно с входами и выходом второго порогового блока, вторые выходы блока усилителей соединены с соответствукяцими первыми входами блока сумматоров, вторые входы которого подклю7 чены к соответствующим выходам регист jpa, выходы блока сумматоров соединены через третий пороговый блок с со.ответствующими вторыми входами декодера, выход которого соединен с вторым входом блока регистров, выход блока регистров является выходом устройства 2 .

Известное устройство также обладает низкой помехоустойчивостью, поскольку в нем недостаточно полно используется информация об амплитуде символов аналогового сигнала.

Цель изобретения - повышение помехоустойчивости приема избыточных сигналов путем учета информации об амплитуде принимаемых символов.

Указанная цель достигается тем, что в устройство для приема и обработки избыточных сигналов, содержащее приемник, вход которого является первым входом устройства, вы-ход приемника соединен с первым входом первого блока памяти, пороговый блок, декодер, первый регистр и второй блок памяти, введены третий блок памяти, .второй и третий регистры, ключи, генератор импульсов, счетчики, блоки сравнения, ранжирующий узел, элемент И и коммутатор, выход первого блока памяти соединен с первым входом . ранжирующего узла и входом порогового блока, выход порогового блока соединен с входом первого счетчика, первый выход которого соединен с входом первого регистра, выходы первого регистра соединены с соответствующими первыми входами второго регистра, выход которого соединен с первым входом третьего регистра, выход третьего регистра соединен с входом декодера и пepJзым входом первого ключа, выход первого ключа является выходом устройства, выход декодера соединен с

вторыми входами первого ключа, первого блока памяти и с первыми входами второго счетчика и генератора импульсов, второй выход первого счетчика соединен с вторым входом генератора импульсов, выход которого соединен с входом третьего счетчика, первый выход которого соединен с первым входом второго блока памяти, первый выход второго блока памяти соедине) через четвертый счетчик с первым входом первого блока сравнения, второй выход третьего счетчика соединен с вторым входом второго счётчика, выход которого соединен с вторым входо первого блока сравнения, выход первого блока сравнения соединен с первыми входами второго ключа, третьего блока памяти и вторым входом второго блока памяти, выход второго блока памяти соединен с вторым входом второго ключа, выход которого соединен с первым входом коммутатора, второй, третий и четвертый входы ранжирующего узла являются соответственно вторым, третьим и четвертым входами устройства, выход ранжирующего узла соединен с вторым входом третьего блока памяти, выход которого соедине с вторым входом коммутатора, выходы коммутатора соединены с входами соответствующих вторых блоков сравнения, первые выходы которых соединены с вторыми входами третьего регистра, а вторые выходы - с соответствующими входами элемента И, выход которого соединен с вторым входом второго регистра.

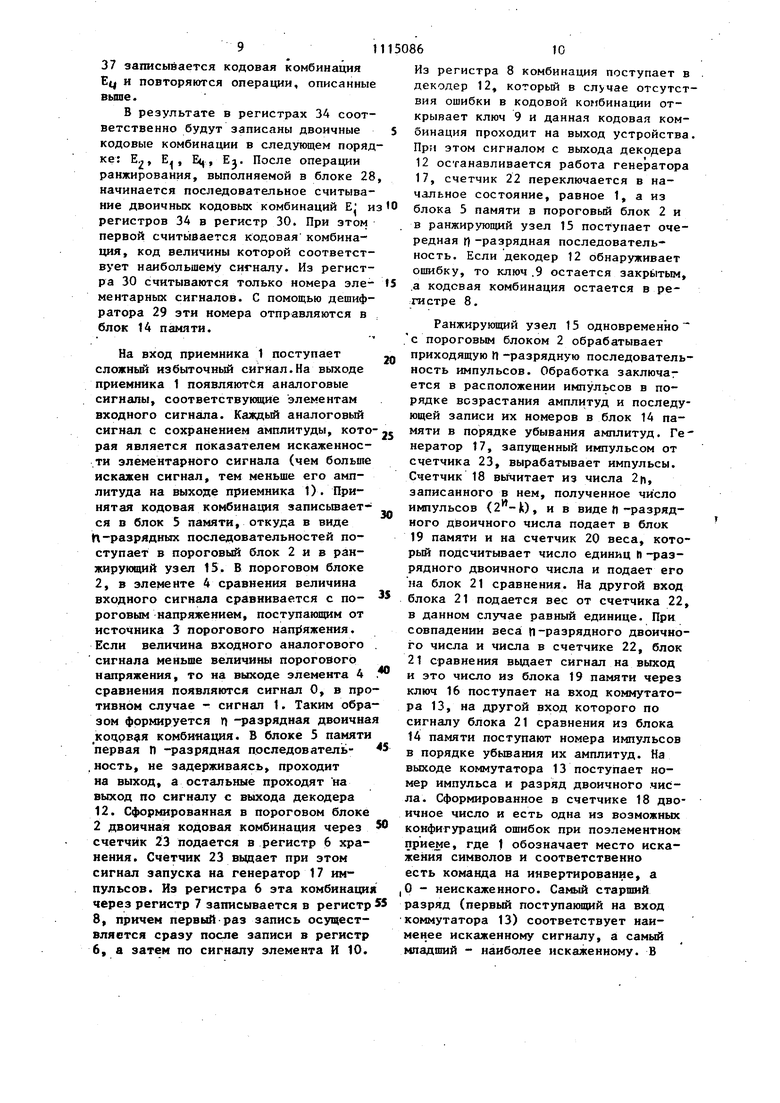

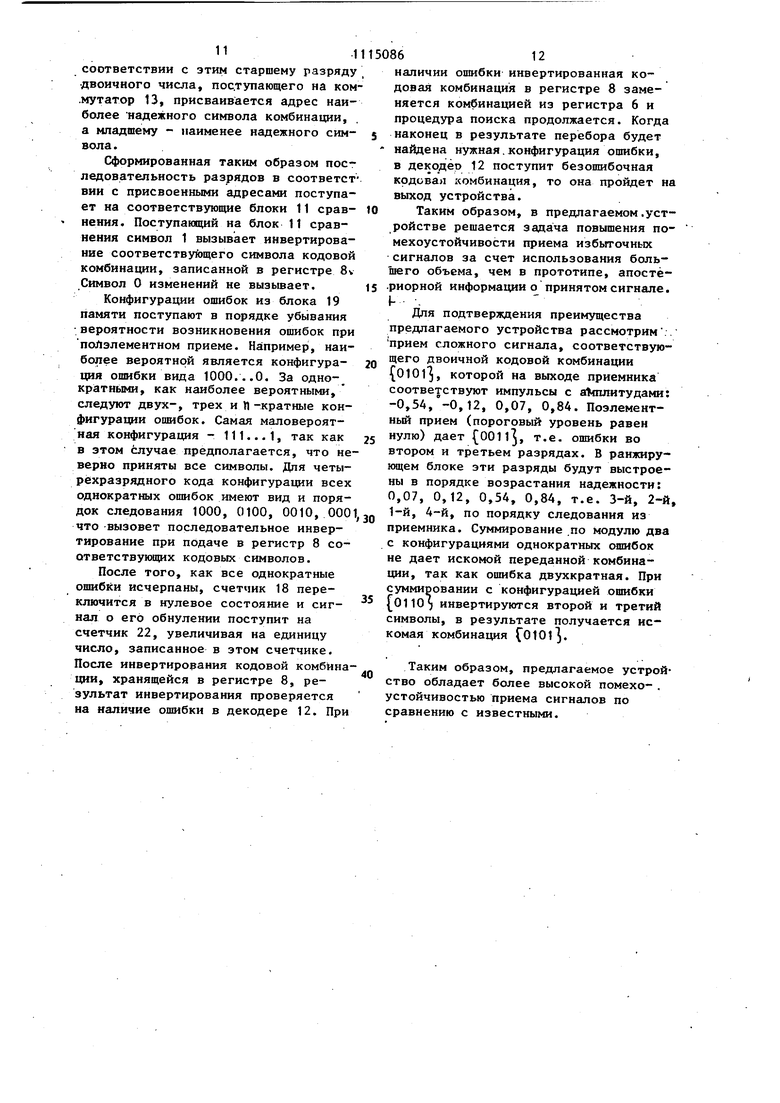

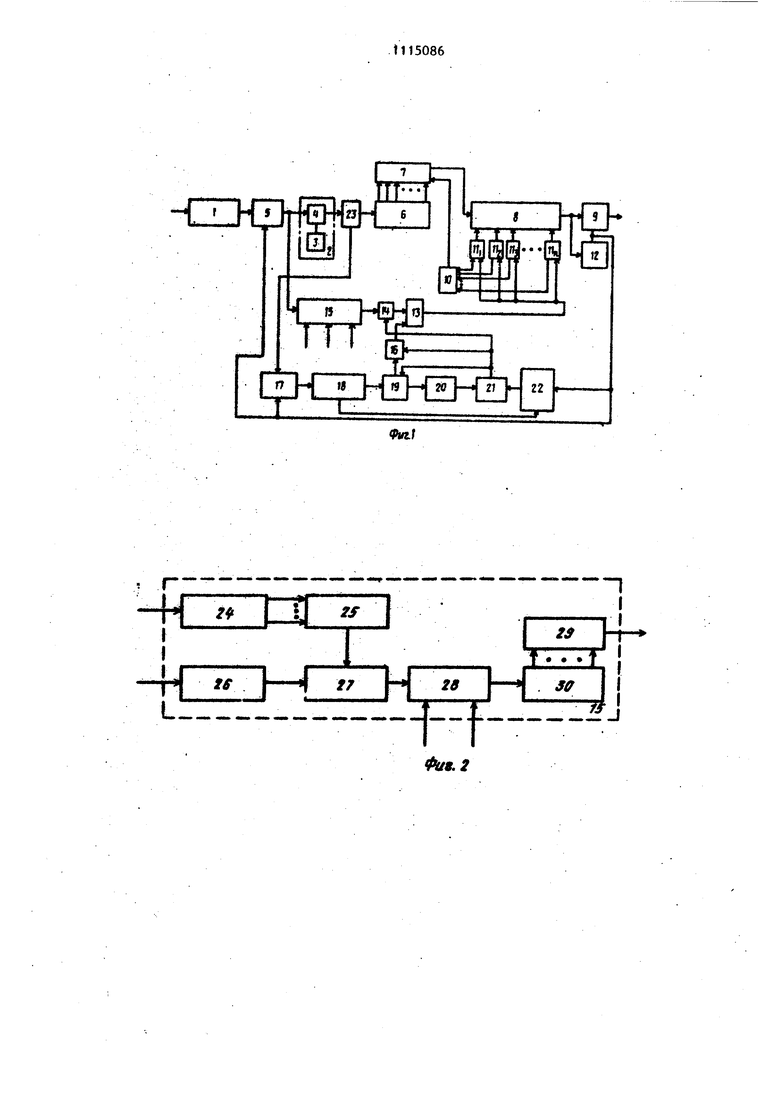

Кроме того, ранжирующий узел содержит аналого-цифровой преобразователь, счетчик, регистры, элемент ШШ блок построения вариационного ряда и дешифратор, выход аналого-цифрового преобразователя соединен с первым входом элемента ИЛИ, выходы счетчика соединены с соответствующими входами первого регистра, выход которого соединен с вторым входом элемента ИЛИ, выход элементаИЛИ соединен с первым входом блока построения вариационного ряда, выход которого соединен с входом второго регистра, выходы которого соединены с соответствующими входами дешифратора, вход аналого-цифрового преобразователя и выход дешифратора являются соответственно первым входом и выходом ранжирующего узла, вход счетчика, второй S11 и третий входы блока построения вариационного ряда являются соответственно вторым,третьим и четвертым входами ранжирующего узла. Кроме того, блок построения вариационного ряда содержит регистр и каналы обработки информации, каждый из которых состоит из ключей, регистров, элементов ИЛИ и элемента сравнения, выход цервого элемента ИЛИ соединен с первым входом первого ключа, вых(д которого соединен с первым входом первого регистра, первый выход которого соединен с первым входом второго элемента .ИЛИ, вторые вькоды - с соответствующими первыми входами элемента сравнения, первый выход которого соединен с первым входом второго ключа, второй выход - с первым входом третьего ключа, первые выходы второго регистра соединены с соответствующими вторыми входами элемента .сравнения, второй выход - с вторыми входами второго и третьего ключей, выходы второго элемента ИЛИ и третьего ключа каждого предыдущего канала обработки информации соединены соответственно с вторым входом первого регистра и входом второго регистра каждого последующего канала обработки информации, выходы первого, второго ключей и первый выход элемента сравнения каждого последующего канала обработки информации соединены .соответственно с вторыми входами первого ключа, второ го элемента ИЛИ и первым входом первого элемента ШШ каждого предыдущего канала обработки информации, выход второго элемента ИЛИ последнего каналс обработки информации соединен с первым входом регистра, вход второго регистра первого канала обработки информации и выход регистра являются соответственно первым входом и выходом блока подстроения вариационного ряда, вторые входы первых элементов ИЛИ канала обработки информации, объединены и являются вторым входом блока построения вариационного ряда, второй вход первого ключа последнего канала обработки информации объединен с вторым входом регистра и является третьим входом блока построения вариационного ряда. Сущность предлагаемого изобретения состоит в том, что информация об амплитудах выходных сигналов приемник используется для упорядочения векто6ров ошибок в соответствии с вероятностью их поянления. Это позволяет исправлять ошибки в соответствии с вероятностью их возникновения, т.е. в первую очередь исправляется наиболее вероятная однократная ошибка,затем двухкратная и т.д. На фиг.1 представлена функциональная схема устройства для приема и обработки избыточных сигналов; на фиг.2 - функциональная схема ранжирующего узла на фиг.З - функциональная схема блока построения вариационного ряда. Устройство (фиг.1) содержит приемНик 1, пороговый блок 2, состоящий из источника 3 порогового напряжения и элемента 4 сравнения, блок 5 памяти, регистры 6-8 сдвига, ключ 9, элемент И 10 и блок 11 сравнения, декодер 12, коммутатор 13, блок 14 памяти, ранжирукяций узел 15, Ключ 16, генератор 17 импульсов, вычитающий счетчик 18, блок 19 памяти, счетчик 20, блок 21 сравнения и счетчики 22 Ранжирующий узел 15 (фиг.2) содержит счетчик 24, регистр 25 сдвига, аналого-цифровой преобразователь 26, элемент ИЛИ 27, блок 28 построения вариационного ряда, дешифратор 29 и регистр 30 сдвига. Блок 28 построения вариационного ряд,а (фиг.З) содержит ключи 31, элементы ИЛИ 32 и 33, регистры 34 сдвига, элементы 35 сравнения, ключи 36, регистры 37 сдвига и ключи 38. Устройство работает следующим об- . разом.f В ранжируницем узле 15 сигнал последовательно поступает на вход аналого-цифрового преобразователя 26. Синхронно с этим сигналом из программно-временного блока на вход счетчика 24 поступают тактовые импульсы. В момент прихода первого сигнала на . вход аналого-цифрового преобразователя 26 в счетчик 24 поступает первый тактовый импульс. После приходап го импульса поступление импульсов прекращается. Двоичный код состояния счетчика 24 параллельно записывается в регистр 25 сдвига. Количество ячеек памяти в счетчике 24 и в регистре 25 равно Ц Выходные сигналы аналого-цифрового преобразователя 26 и счетчика 24 подаются на входы элемента ИЛИ 27. При этом первой через элемент ИЛИ 27 про ходит, последовательно считываясь из .регистра 25, двоичная кодовая комбинация, код которой отображает номер входного сигнала. Считывание кода номера происходит во время функциони рования аналого-цифрового преобразователя 26, выходная двоичная кодовая комбинация которого поступает на вход элемента ИЛИ 27 после передачи номера кодовой комбинации. Блок 28 построения вариационного ряда упорядочивает совокупность входных двоичных комбинаций с величинаг-ш двоичных .кодов, На пример, пусть И 4, m 16. Тогд ,--{1000 001. Е, (1010 010, ЕЗ .{0100 он, Е {0110 100. В десятичной системе счисления соответственнс получим ,1, Е 10,2, Е,3}, E 6,4j. На выходе блока 23 построения вариационного ряда дол жны быть получены комбинации Ej в следунлцем порядке: Е, Е, Е, Е, т.е. первой на выход блока 28 постро ения вариационного ряда будет выдаваться комбинация Ел, имеющая максимальный код величины входного сигнала, второй Е, третей - Ед и последней - Е. Рассмотрим работу блока 28 на дан ном примере. В течение всего времени работы блока 28, когда нет необходимости переписывать комбинации E;J из одного регистра в другой, ключи 31 закрыты. Во время переписывания информации в регистрах 34 и 37 управля ющий сигнал от программно-временного блока открывает ключи 31. В исход ном состоянии регистры 34 и 37 находятся в нулевом состоянии, ключи 36 38 закрыты, ключи 31 открыты. Первой на вход блока 28 подается двоичная комбинация Е, и записьшается в первы регистр 37. Выходы имеются не у всех ячеек памяти этого регистра, а только у левых, в которых записан код ве личины аналогового сигнала. На входы первого элемента 35 сравнения подает ся двоичный код {ЮОО, а на другие его входы - нулевой код из регистра 34. В элементе 35 сравнения указанны коды сравниваются между собой. Поскольку код, записанный в регистре 37, больше нулевого кода, записанногоВ регистре 34, то управляющий сиг кал выдается с левого выхода элемента 35 сравнения на УПРАВЛЯЮЩИЙ вход ключа 36, открывая его. В этот момент времени с программно-управляющего блока на вход элементов ИЛИ 32 подается управляющий синхроимпульс, длительность которого определяется временем переписывания двоичной кодой комбинации Е из регистра 37 через открытый ключ 36 в регистр 34. Для этого на все регистры 34 подаются тактовые импульсы с программно-вре- менного блока через открытые ключи..31-. В результате описанных действий двоичная комбинация Е переписывается из регистра 37 в регистр 34. После этого на вход элементов ИЛИ 32 подается управляющий импульс с выхода программно-временного блока. Затем в первый регистр 37 записывается двоичная кодовая комбинация Е2. В элементе ИЛИ 35 сравнения ее код сравнивается с кодом комбинации Е, храня- щейся в регистре 34. Так как число 10 больше числа 8 (E.tEj), то на левом выходе элемента 35 сравнения формируется управляющий сигнал, открывающий ключ 36, через который из регистра 37 в регистр 34 переписывается кодовая комбинация Е2, сдвигая при этом комбинацию Е через элемент ИЛИ. 33 в следующий регистр 34. Очередная двоичная кодовая комбинация EJ поступает в первый регистр 37 и в элементе 35 сравнения ее код сравнивается с кодом Е, записанным в первом регистре 34. Так как (Е.), то на правом выходе элемента 35 сравнения формируется управляющий сигнал, который открывает ключ 38 и из первого регистра 37 во второй регистр 37 переписывается комбинация ЕЗ и выполняется операция сравнения в элементе 35 кода Ет с кодом Е, записанным во втором регистре 34. Поскольку (EjxcEf), то управляю|ций сигнал элемента 35 сравнения формируется на правом выходе. По этому сигналу открывается второй ключ 38, пропуская в третий ренистр 37 кодовую комбинацию EJ. Теперь ее код сравнивается с помощью третьего элемента 35 сравнения с нулевым кодом третьего регистра 34. В результате сравнения управляющий сигнал появляется на левом выходе третьего элемента 35 сравнения, открывая ключ 36. Комбинация EJ из регистра 37 переписывается в регистр 34. Во входной регистр 37 записывается кодовая комбинация Ец и повторяются операции, описанные вьше. В результате в регистрах 34 соответственно будут записаны двоичные кодовые комбинации в следующем поряд ке: Еу, Е,, Ец, El. После операции ранжирования, выполняемой в блоке 28 начинается последовательное считывание двоичных кодовых комбинаций Е| и регистров 34 в регистр 30. При этом первой считывается кодовая комбинация, код величины которой соответствует наибольшему сигналу. Из регистра 30 считываются только номера элементарных сигналов. С помощью дешифратора 29 эти номера отправляются в блок 14 памяти. На вход приемника 1 поступает сложный избыточный сигнал.На выходе приемника 1 появляются аналоговые сигналы, соответствунлцие элементам входного сигнала. Каждый аналоговый сигнал с сохранением амплитуды, кото рая является показателем искаженности элементарного сигнала (чем больше искажен сигнал, тем меньше его амплитуда на выходе приемника 1). Принятая кодовая комбинация записывается в блок 5 памяти, откуда в виде Л-разрядных последовательностей поступает в пороговый блок 2 и в ранжирую1ций узел 15. В пороговом блоке 2, в элементе 4 сравнения величина входного сигнала сравнивается с пороговым напряжением, поступающим от источника 3 порогового напц яжения. Если величина входного аналогового сигнала меньше величины порогового напряжения, то на выходе элемента 4 сравнения появляются сигнал О, в про тивном случае - сигнал 1. Таким обра зом формируется п -разрядная двоична коцрв9я комбинация. В блоке 5 памяти первая П -разрядная последовател1 .ность, не задерживаясь, проходит на выход, а остальные проходят на выход по сигналу с выхода декодера 12. Сформированная в пороговом блоке 2 двоичная кодовая комбинация через счетчик 23 подается в регистр 6 хранения. Счетчик 23 выдает при этом сигнал запуска на генератор 17 импульсов. Из регистра 6 эта комбинаци через регистр 7 записывается в регистр 8, причем первый раз запись осуществляется сразу после записи в регистр 6, а затем по сигналу элемента И 10. 86 Из регистра 8 комбинация поступает в декодер 12, который в случае отсутствия ошибки в кодовой копбинации открывает ключ 9 и данная кодовая комбинация проходит на выход устройства. Пря этом сигналом с выхода декодера 12 останавливается работа генератора 17, счетчик 22 переключается в начальное состояние, равное 1, а из блока 5 памяти в пороговый блок 2 и в ранжир5ПОЩИЙ узел 15 поступает очередная Г) -разрядная последовательность. Если декодер 12 обнаруживает ошибку, то ключ .9 остается закрытым, а кодовая комбинация остается в регистре 8. Ранжирующий узел 15 одновременно с пороговым блоком 2 обрабатывает приходящую Ц-разрядную последовательность импульсов. Обработка заключат ется в расположении импульсов в порядке возрастания амплитуд и последующей записи их номеров в блок 14 памяти в порядке убывания амплитуд. Генератор 17, запущенный импульсом от счетчика 23, вырабатывает импульсы. Счетчик 18 вычитает из числа 2(i, записанного в нем, полученное число импульсов (), и в виде П-разрядного двоичного числа подает в блок 19 памяти и на счетчик 20 веса, который подсчитывает число единиц П-разрядного двоичного числа и подает его на блок 21 сравнения. На другой вход блока 21 подается вес от счетчика 22, в данном случае равный единице. При совпадении веса n-разрядного двоичного числа и числа в счетчике 22, блок 21 сравнения вьщает сигнал на выход и это число из блока 19 памяти через ключ 16 поступает на вход коммутатора 13, на другой вход которого по сигналу блока 21 сравнения из блока 14 памяти поступают номера импульсов в порядке убьшания их амплитуд. На выходе коммутатора 13 поступает номер импульса и разряд двоичного числа. Сформированное в счетчике 18 двоичное число и есть одна из возможных конфигураций ошибок при поэлементном приеме, где 1 обозначает место искажения символов и соответственно есть команда на инвертирование, а 0 - неискаженного. Самый старший разряд (первый поступающий на вход коммутатора 13) соответствует наименее искаженному сигналу, а самый младший - наиболее искаженному. В соответствии с этим старшему разряду двоичного числа, поступающего на ком .мутатор 13, присваивается адрес наиболее надежного символа комбинации, а младшему - наименее надежного символа . Сформированная таким образом последовательность разрядов в соответст вии с присвоенными адресами поступает на соответствуюпще блоки 11 сравнения. Поступающий на блок 11 сравнения символ 1 вызывает инвертирование соответствующего символа кодовой комбинации, записанной в регистре 8v Символ О изменений не вызьшает. Конфигурации ошибок из блока 19 памяти поступают в порядке убывания вероятности возникновения ошибок при поЛэлементном приеме. Например, наиболее вероятной является конфигурация ошибки вида 1000...0. За одно- кратными, как наиболее вероятными, следуют двух-, трех и П-кратные конфигурации ошибок. Самая маловероятная конфигурация - 111... 1, так как в этом случае предполагается, что не верно приняты все символы. Для четырёхразрядного кода конфигурации всех однократных ошибок имеют вид и порядок следования 1000, 0100, 0010, 000 что вызовет последовательное инвертирование при подаче в регистр 8 соответствующих кодовых символов. После того, как все однократные ошибки исчерпаны, счетчик 18 переключится в нулевое состояние и сигнал о его обнулении поступит на счетчик 22, увеличивая на единицу число, записанное в этом счетчике. После инвертирования кодовой комбина ции, хранящейся в регистре 8, результат инвертирования проверяется на наличие ошибки в декодере 12. При 1 8612 наличии ошибки инвертированная кодовая комбинация в регистре 8 заменяется комбинацией из регистра 6 и процедура поиска продолжается. Когда наконец в результате перебора будет найдена нужная.конфигурация ошибки, в декодер 12 поступит безошибочная кодовая комбинация, то она пройдет на выход устройства. Таким образом, в предлагаемом.устройстве решается задача повышения помехоустойчивости приема избыточных сигналов за счет использования большего объема, чем в прототипе, апостёриорной информации о принятом сигнале. Для подтверждения преимущества предлагаемого устройства рассмотрим., прием сложного сигнала, соответствующего двоичной кодовой комбинации {0101, которой на выходе приемника соответствуют импульсы с а тлитудами: -0,54, -0,12, 0,07, 0,84. Поэлементный прием (пороговый уровень равен нулю) дает (0011, т.е. ошибки во втором и третьем разрядах. В ранжирующем блоке эти разряды будут выстроены в порядке возрастания надежности: 0,07, 0,12, 0,54, 0,84, т.е. 3-й, 2-й, 1-й, 4-й, по порядку следования из приемника. Суммирование .по модулю два с конфигурациями однократных ошибок не дает искомой переданной комбинации, так как ошибка двухкратная. При суммировании с конфигурацией ошибки 0110 инвертируются второй и третий символы, в результате получается искомая комбинация (0101. Таким образом, предлагаемое устройство обладает более высокой помехо- . устойчивостью приема сигналов по сравнению с известными. : Г -fl -тН M H

Фи9.2 I1 I TV. .f H Jj

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М., Советское радио, 1968, с | |||

| Приспособление для уменьшения дымовой тяги паровоза | 1920 |

|

SU270A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для приема избыточнойиНфОРМАции | 1979 |

|

SU824263A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-09-23—Публикация

1982-11-09—Подача