гб

ел

Јь

00 00 Ј

00

Изобретение относится к вычислительной технике и технике приема/передачи данных и может применяться для повышения достоверности приема последовательной информации.

Целью изобретения является повышение достоверности устройства.

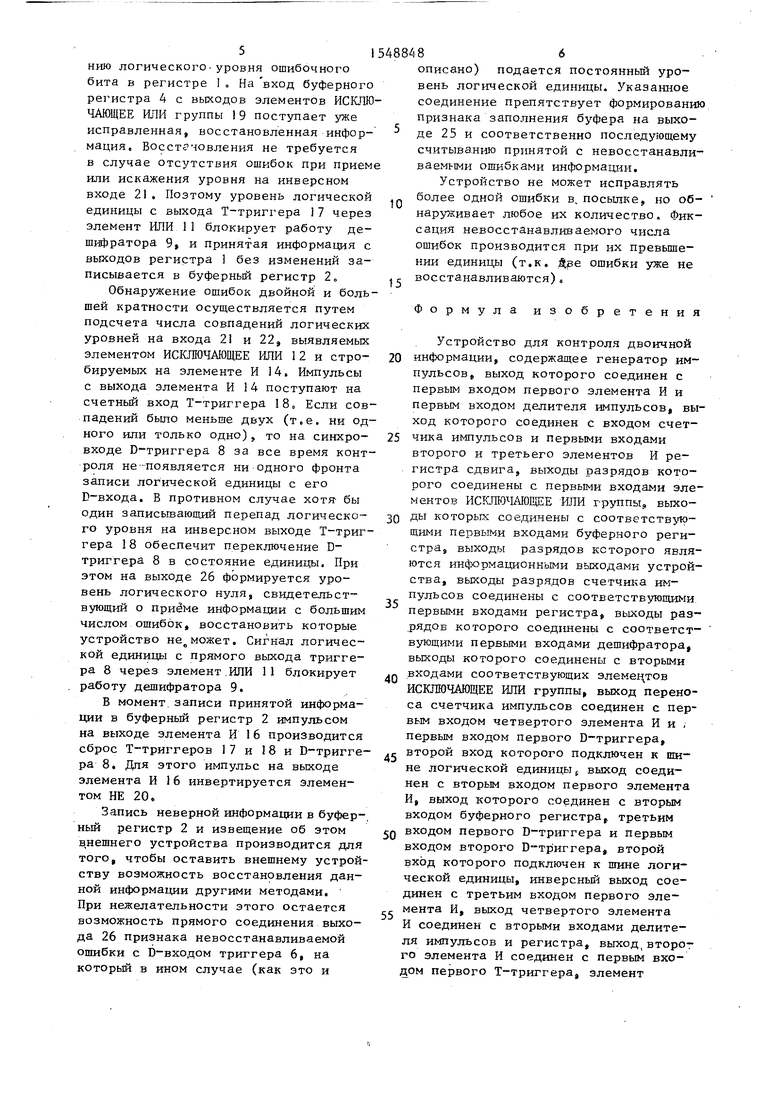

На чертеже представлена функциональная схема устройства.

Устройство для контроля двоичной информации содержит регистр 1 сдвига, буферный регистр 2, г.енератор 3 импульсов, делитель 4 импульсов, счетчик 5 импульсов, D-триггеры 6-8, дешифратор 9, регистр 10, элемент ИЛИ 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, элементы И 13-16, Т-триггеры 17 и 18, группу 19 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент НЕ 20, на че ртеже также пока- заны первый (инверсный) 21 и второй (прямой) 22 информационные входы, управляющий вход 23 (строба очистки буфера), информационные выходы 24, первый 25 (признак заполнения буфера) и второй 26 (признак невосстановленной ошибки) управляющие выходы 25 и 26 устройства.

Устройство работает следующим образом,

Последовательный код входной информации поступает с буферов согла- сователей дифференциального канала (на схеме не показаны) на прямой 22 и инверсный 21 входы устройства. В состоянии ожидания приема информации на выходе переполнения счетчика 5 будет уровень логической единицы. Уровень логической единицы на прямом входе 22 подтверждает состояние ожи- дания устройства. Стартовый бит (уровень логического нуля на прямом входе) разблокирует работу делителя 4 и в случае достаточной длительности (более половины заданной длитель- ности импульса одного бита) устройство начинает прием последовательной информации в регистр 1. Каждый принятый бит подсчитывается в счетчике 5 и, когда число превысит заданное, на выходе переполнения счетчика 5 появится уровень логической единицы. Если передаваемая последовательность завершена, то уровень логической единицы на прямом входе 22 подтвердит это и через элемент 15 заблокирует работ делителя 4. Прием информации прекращается до появления нового стартового бита.

0

Q с

5

5

Передний фронт сигнала переполнения устанавливает D-триггер 7 в единичное состояние и, если D-триггер 6 будет сброшен, импульс с выхода генератора 3 через элемент 16 записывает в буферный регистр 2 выдаваемую на выходы 24 информацию. При этом тот же импульс записи с выхода элемента 16 сбрасывает D-триггер 7 и устанавливает в единичное состояние D-триггер- 6. Уровень логической единицы на выходе 25 является признаком заполнения буфера. D-триггер 6 сбрасывается только после прихода строба очистки буфера по входу 23, подтверждающему перезапись содержимого буферного регистра 2 во внешнее устройство, после чего уровень логической единицы с инверсного выхода D-триггера 6 разрешает запись в буферный регистр 2 новой информации.

Контроль информации по модулю два и ее исправление производится следующим образом.

Импульсы приема информации с выхода делителя 4 поступают на элемент И 13, ив случае приема единицы она проходит на синхровход счетного триггера 17. В случае, если число единиц в принимаемой последовательности нечетно, на выходе Т-триггера 17 будет уровень логической единицыв свидетельствующий об отсутствии ошибки четности (этим осуществляется конт- роль четности по модулю два), Иначе, на выходе Т-триггера 17 будет уровень логического нуля, который через элемент ИЛИ 11 может разблокировать работу дешифратора 9 кода бита ошибки.

Ошибочный бит в предлагаемом устройстве выявляется путем сравнения логических уровней в прямого 22 и инверсного 21 информационных входов устройства на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 12. Если уровни совпадают, то это признается ошибкой, так как в нормальном режиме сигналы должны быть противоположных уровней, т.е. не совпадать. Момент совпадения стробируется на элементе 14 импульсом приема информации с выхода делителя 4, и в регистр 10 записывается код номера принятого бита информации. Этот код разблокированным дешифратором 9 будет преобразован в управляющий потенциал на соответствующем выходе, что приводит к инвертированию логического - уровня ошибочного бита в регистре 1 , На вход буферного регистра 4 с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 19 поступает уже исправленная, восстановленная информация, Восстгчовления не требуется в случае отсутствия ошибок при прием или искажения уровня на инверсном входе 21. Поэтому уровень логической единицы с выхода Т-триггера 17 через элемент ИЛИ 11 блокирует работу дешифратора 9, и принятая информация с выходов регистра 1 без изменений записывается в буферный регистр 2„

Обнаружение ошибок двойной и большей кратности осуществляется путем подсчета числа совпадений логических уровней на входа 21 и 22, выявляемых элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 12 и стро- бируемых на элементе И 14. Импульсы с выхода элемента И 14 поступают на счетный вход Т-триггера 18, Если совпадений было меньше двух (т.е. ни одного или только одно), то на синхро- входе D-триггера 8 за все время контроля не появляется ни одного фронта записи логической единицы с его D-входа. В противном случае хотя- бы один записывающий перепад логического уровня на инверсном выходе Т-триггера 18 обеспечит переключение D- триггера 8 в состояние единицы. При этом на выходе 26 формируется уровень логического нуля, свидетельствующий о приёме информации с большим числом ошибок, восстановить которые устройство неоможет. Сигнал логической единицы с прямого выхода триггера 8 через элемент ИЛИ 11 блокирует работу дешифратора 9.

В момент записи принятой информации в буферный регистр 2 импульсом на выходе элемента И 16 производится сброс Т-триггеров 17 и 18 и D-тригге- ра 8. Для этого импульс на выходе элемента И 16 инвертируется элементом НЕ 20,

Запись неверной информации в буферный регистр 2 и извещение об этом внешнего устройства производится для того, чтобы оставить внешнему устройству возможность восстановления данной информации другими методами. При нежелательности этого остается возможность прямого соединения выхода 26 признака невосстанавливаемой ошибки с D-входом триггера 6, на который в ином случае (как это и

описано) подается постоянный уровень логической единицы. Указанное соединение препятствует формированию признака заполнения буфера на выходе 25 и соответственно последующему считыванию принятой с невосстанавливаемыми ошибками информации.

Устройство не может исправлять

П более одной ошибки в, посылке, но об- наруживает любое их количество. Фиксация невосстанавливаемого числа ошибок производится при их превышении единицы (т.к. Две ошибки уже не

г восстанавливаются),

Формула изобретения

Устройство для контроля двоичной

0 информации, содержащее генератор импульсов, выход которого соединен с первым входом первого элемента И и первым входом делителя импульсов, выход которого соединен с входом счет5 чика импульсов и первыми входами второго и третьего элементов И регистра сдвига, выходы разрядов которого соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выхоQ ды которых соединены с соответствующими первыми входами буферного регистра, выходы разрядов которого являются информационными выходами устройства, выходы разрядов счетчика импульсов соединены с соответствующими первыми входами регистра, выходы разрядов которого соединены с соответствующими первыми входами дешифратора, выходы которого соединены с вторыми

л входами соответствующих элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выход переноса счетчика импульсов соединен с первым входом четвертого элемента И и , первым входом первого D-триггера,

с второй вход которого подключен к шине логической единицы,, выход соединен с вторым входом первого элемента И, выход которого соединен с вторым входом буферного регистра, третьим

Q входом первого D-триггера и первым входом второго D-триггера, второй вход которого подключен к шине логической единицы, инверсный выход соединен с третьим входом первого эле- , мента И, выход четвертого элемента И соединен с вторыми входами делителя импульсов и регистра, выход второго элемента И соединен с первым входом первого Т-триггера, элемент

5

71

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом третьего эле- йента И, выход которого соединен с третьим входом регистра, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является первым информационным входом устройства, вторые входы регистра сдвига, второго и четвертого элементов И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ объединены и являются вторым информационным входом устройства, третий вход и прямой выход второго D-тригге ра являются соответственно управляющим входом и первым управляющим выхо дом устройства, отличающее с я тем, что, с целью повышения дос товерности устройства, в него введены элемент НЕ,второй Т-триггер, тре488488

тми D-триггер и элемент ИЛИ, выход которого соединен с вторым входом дешифратора, вход элемента НЕ подклю- чен к выходу первого элемента И, выход соединен с вторым входом первого Т-триггера и первыми входами второго Т-триггера и третьего D-триггера, второй вход которого подключен к

Ю шине логической единицы, прямой выход соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу первого Т-триггера, второй вход второго Т-триггера подклю15 чен к выходу третьего элемента И, инверсный выход соединен с третьим входом третьего D-триггера, инверсный выход которого является вторым управляющим выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство Нисневича для контроля двоичной информации | 1987 |

|

SU1464294A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

| Устройство для передачи и приема информации | 1984 |

|

SU1269174A1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| УСТРОЙСТВО ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2217791C1 |

Изобретение относится к области вычислительной техники и техники приема/передачи данных и может применяться для повышения достоверности приема последовательной информации. Целью изобретения является повышение достоверности устройства. Устройство для контроля двоичной информации содержит регистр 1 сдвига, буферный регистр 2, генератор 3 импульсов, делитель 4 импульсов, счетчик 5 импульсов, D-триггеры 6-8, дешифратор 9, регистр 10, элемент ИЛИ 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, элементы И 13 - 16, Т-триггеры 17, 18, группу 19 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент НЕ 20. 1 ил.

Редактор Н.Лазаренко

Составитель С.Берестевич

Техред Л.Сердюкова Корректор Н„Ревская

Заказ 145

Тираж 655

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР , 113035, Москва, Ж-35, Раушская наб., д. 4/5

,«--.«--. - - - - -- - - ---..--,„---«-- - -.----- -----.----- - --.-.-- - - ------------- - - - - - -

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

Подписное

| Устройство Нисневича для контроля двоичной информации | 1987 |

|

SU1464294A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-07—Публикация

1988-07-07—Подача