Устройство относится к области вычислительной техники и предназначено для использования в системах управления гибкими автоматизированными производствами, тех1гологическими процессами, в специализированных вычислительных устройствах.

Целью изобретения является расширение класса решаемых задач за счет возможности преобразования заданного числа непрерывных монотонных функций.

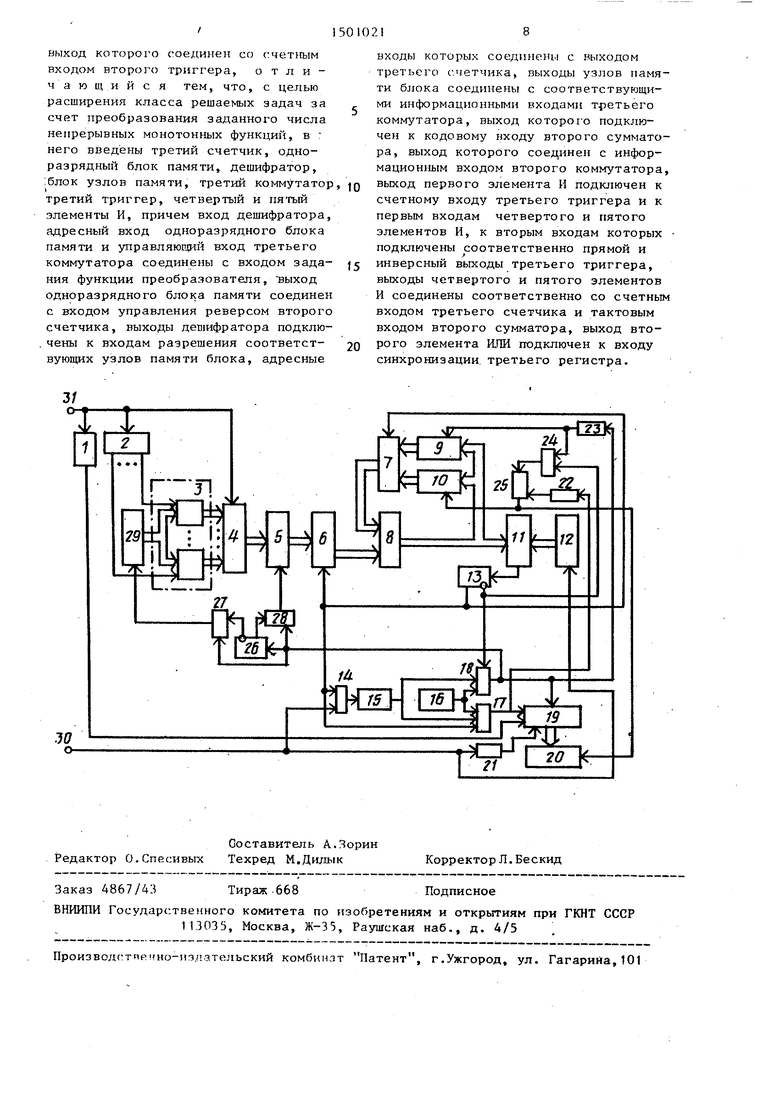

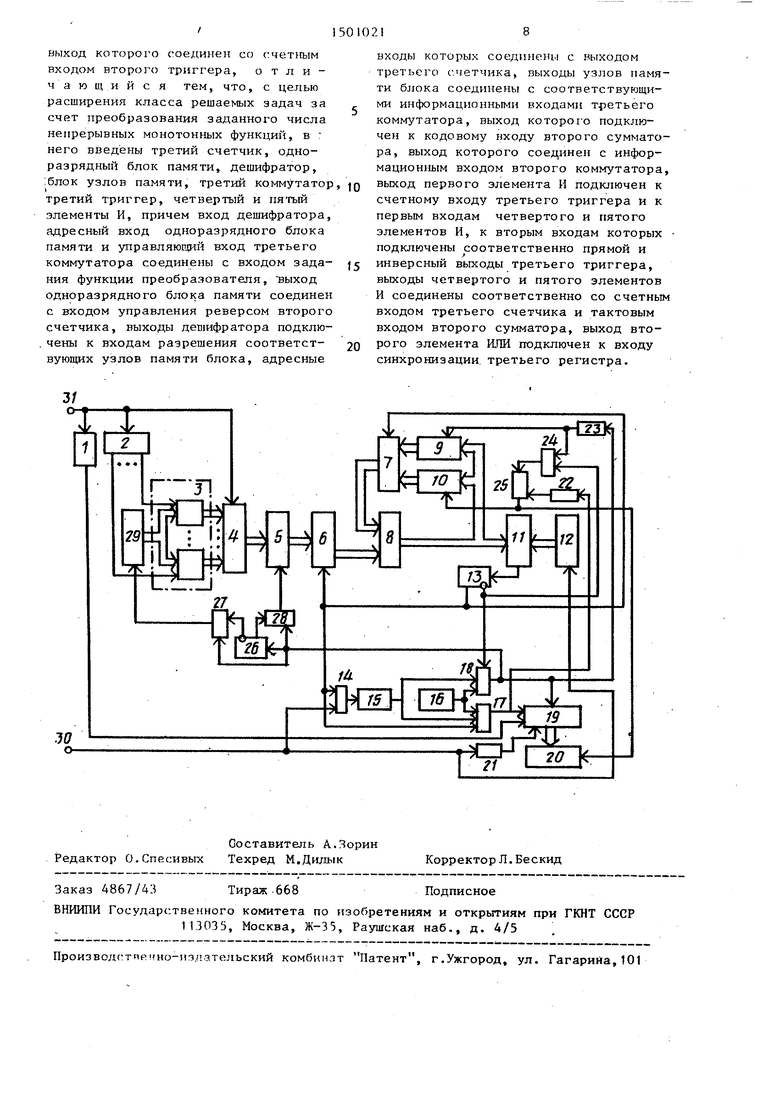

На чертеже представлена функциональная схема преобразователя.

Устройство содержит одноразрядный блок 1 памяти, дешифратор 2, блок 3 узлов памяти, коммутатор 4, сумматор 5, коммутаторы б, 7, сумматор 8, регистры 9, 10, схему 11 сравнения, счетчик 12, триггер 1 3, элемент IL M 14, триггер 15, генератор 16 импульсов, элементы И 17 и 18, счетчик 19, регистр 20, элементы 21-23 задержки, элемент И 24, элемент ИЛИ 25, триггер 26, элементы И 27 и 28, счетчик

ь:)

3150

29, тактовый вход 30 устройства, вход 31 задания функции устройства. Первый сумматор 8 выполнен комбинационным, а второй 5 - накапливающим.

В общем виде метод преобразования непрерывно строго монотонных функций запишется следующим образом:

L.(p+l) L,(p) +4 Sq,(p),

г р+ (

«V

F(t

P+t

,/(п), )%(tj,, ) + sign (г)-2

L/j-Ы) L(p+l)/2

A- V

p+1

этап 2.

J+a

+ L.(j + 1),

) F(t ) sign(r)-2где r 1 - для строго монотонно возрастающих .функций и г -1 - для строго монотонно убывающих функцш . .

Начальные значения L(,(o) й (; и S (о) 4 Ч о , где Л Л конечные разности взаимообратной функции (t) на равномерной сетке с шагом . В качестве начального значения функции ее значение

F(t,).

Номер q разряда, в котором осуществляется развертка с увеличенным шагом, определяется из выражения

- logjC (Л М Х,)

jCflT

ч

),

1(2

.где д сСр+1, 4 конечные разности первого и второго порядка взаимно обратной функции Ф(t) на равномерных сетках соответственно с шагами 2 и 2-14 tf}, На практике достаточно проверить условие в тех узлах сетки, где функция F(t) имеет наибольшую кривизну.

Дпя непрерывных строго монотонных функций как правило , где

- целое с избытком.

Устройство работает следую1дим образом.

В исходном состоянии регистр 9 и сумматор 5 записан двоичный код интервала постоянства L(o), счетчики 12 и 19, триггеры 13, 15, 26 обнулены.

Первый счетньп импульс с входа 30 устройства поступает на счетчик 12,

увеличивая его содержимое на 2

Л

через элемент ИЛИ 14 на счетный вход триггера 15, перекгаочая его в единицу. Пройдя элемент 21 задержки, счет21

ный импульс сбрасывает в ноль младшие (Л - q) разряды счетчика 19. Единица с прямого выхода триггера 13 поступает на входы элементов И 17 и 18. Элемейт И 18 открыт сигналом 1 с инверсного выхода триггера 13.

Код функции поступает с входа 31 устройства на дешифратор 2 и комму- Q татор 4. Код с выхода дешифратора 2 поступает на входы разрешения- блока 3 узлов памяти и разрешает считывание информации с j-ro узла, в котором записаны локальные тренды j-й преобра- 5 зуемой функции. В коммутаторе А код с входа 31 управляет передачей на вход сумматора 5 локальных трендов с j-ro узла блока 3.

Тактовые импульсы генератора 16 0 импульсов, пройдя открытый элемент И 18, поступают на вход пересчета с весом 2 счетчика 19, увеличивая его содержимое на . Кроме того, тактовые импульсы через открытый сигна- 5 лом 1 с инверсного выхода триггера 26 элемент И 27 поступают на счетный вход счетчика 29, увеличивая его со- 1держимое на 1. По заднему фронту тактового импульса счетный триггер 26 0 переключается в 1. Считанное из

j-ro узла значение очередного лакаль- ного тренда q-ro разряда поступает через коммутатор 4 на вход сумматора 5. Следующий тактовый импульс по- 5 ступает через открытый сигналом 1 с прямого выхода триггера 26 элемент И 28 на тактируюпцш вход сумматора 5, в котором осуществляется вычисление очередного интервала постоянства 0 L(p+l).

По заднему фронту токтового импульса триггер 26 изменяет свое состояние на противоположное, осуществ- 5 ляя пересчет тактовых импульсов по модулю 2.

Код с выхода сумматора 5 поступает через коммутатор 6 на вход второго слагаемого сумматора 8, Hd вход CQ первого слагаемого которого поступает код с выхода регистра 9. В результате выполнения операции сложения на выходе сумматора 8 появляется двоич- код аргумента t . В схеме 1 2 сравнения код с выхода сумматора 8 сравнивается с кодом аргумента t , поступающим с выхода счетчика 12.

Если tp.j , то на выходе схемы 11 сравнения остается ноль. В этом

150102

случае в регистр 10 записывается код с выхода сумматора 8. При развертке с увеличенным шагом в регистр 9 записывается код с выхода сумматора 8 независимо от результата сравнения.

При появлении на выходе схемы 11 сравнения единицы триггер 13 переключается в сдиниду и ноль с его инверс- ного выхода закрывает элемент И 24 ю и в регистре 10 остается прежнее значение суммы интервалов постоянства q-ro разряда.

Реализуется переход ко второму этапу преобразования, т.е. к разверт- 15 ке мелким шагом. Тактовые импульсы через открытый сигналом с прямого выхода триггера 13 элемент И 17 поступают на вход пересчета с весом 2 счетчика 19. На вход первого слагае,- МОго сумматора 8 поступает через коммутатор 7 код с выхода регистра 10, а на вход второго слагаемого поступает сдвинутый в коммутаторе 6 на (А ч) разрядов в сторону младших код (р+1)-го интервала постоянства q-ro разряда. В результате выполнения в сумматоре 8 операции сложения на

20

25

импульсов, два элемента ИЛИ, три мента И, три элемента задержки, п чем тактовый вход преобразователя соединен с первыми входами первог элемента {-ШИ, первого элемента за держки и счетным входом первого с чика, выход которого соединен с п вым входом схемы сравнения, второ вход которой подключен к выходу п вого сумматора и информационным в дам первого и второго регистров, диненных выходами соответственно первым и вторым информационными в дами первого коммутатора, выход к рого соединен с входом первого сл гаемого первого сумматора, вход в рого слагаемого которого подключе выходу второго коммутатора, управ 1цие входы первого и второго комму торов соединены с прямым выходом вого триггера, счетный вход котор подключен к выходу схемы сравнени инверсный выход первого триггера динен с первым входом первого эле та И, к второму и третьеьгу входам торого подключены соответственно мой выход второго триггера и выхо генератора импульсов, подключенны

его выходе появляется код аргумента

tj, которьш сравнивается в схеме 11 30 первому входу второго элемента И, с кодом вь1хода счетчика 12.

сравнения ,, ,, - ,- ,

Код аргумента t О записывается в регистр 10. В это время в регистр 20 осуществляется запись содержимого счетчика 19. Синхронизация записи в 5 регистры 10 и 20 осуществляется им- пульсами с выхода второго элемента ИЛИ 25. Второй этап преобразования осуществляется до тех пор, пока на выходе схемы 11 сравнения не появит- 40 ся единица. Тогда триггер 13 переключается в ноль, переключая в свою очередь триггер 15, ноль с прямого выхода которого закрывает элементы И 17 и 18. На этом вычисление текущего 45 значения непрерывной строго монотонной функции F(t) заканчивается, ее значение записано в регистр 20.

При поступлении следующего счетного импульса на вход 30 устройства 50 повторяется описанньй вычислительный процесс.

Формула изобретения

второй и третий входу которого со нены с прямыми выходами соответст но первого и второго триггеров, в ходы первого и второго элементов подключены к счетным входам второ счетчика с весами соответственно и 2 , где Л- разрядность аргуме q - номер разряда, с которого вед ся развертка с увеличенным шагом, ход второго счетчика соединен с ин формационным входом третьего регис ра, выход второго элемента И соеди нен через второй элемент задержки первым входом второго элемента ИЛИ подключенного выходом к входу синх низации второго регистра, выход пе вого элемента И подключен через тр тий элемент задержки к входу синхр низации первого регистра и первому входу третьего элемента И, второй вход которого соединен с инверсным выходом первого триггера, выход тр тьего элемента Н соединен с вторым входом второго элемента ИЛИ, выход первого элемента задеряки подключе к .входу установки в О младших Aразрядов второго счетчика, прямой выход первого триггера соединен с вторым входом первого элемента НТК

Функциональный преобразователь, содержащий два счетчика, два сумматора, два коммутатора, схему сравнения, три регистра, два триггера, 1 енератор

0

5

импульсов, два элемента ИЛИ, три элемента И, три элемента задержки, причем тактовый вход преобразователя соединен с первыми входами первого элемента {-ШИ, первого элемента задержки и счетным входом первого счетчика, выход которого соединен с первым входом схемы сравнения, второй вход которой подключен к выходу первого сумматора и информационным входам первого и второго регистров, сое- диненных выходами соответственно с первым и вторым информационными входами первого коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, вход второго слагаемого которого подключен к выходу второго коммутатора, управляю- 1цие входы первого и второго коммутаторов соединены с прямым выходом первого триггера, счетный вход которого подключен к выходу схемы сравнения, инверсный выход первого триггера соединен с первым входом первого элемента И, к второму и третьеьгу входам которого подключены соответственно пря-; мой выход второго триггера и выход генератора импульсов, подключенный к

0 первому входу второго элемента И,

5 0 5

0

5

второй и третий входу которого соединены с прямыми выходами соответственно первого и второго триггеров, выходы первого и второго элементов И подключены к счетным входам второго счетчика с весами соответственно 2 и 2 , где Л- разрядность аргумента, q - номер разряда, с которого ведется развертка с увеличенным шагом, выход второго счетчика соединен с информационным входом третьего регистра, выход второго элемента И соединен через второй элемент задержки с первым входом второго элемента ИЛИ, подключенного выходом к входу синхронизации второго регистра, выход первого элемента И подключен через третий элемент задержки к входу синхронизации первого регистра и первому входу третьего элемента И, второй вход которого соединен с инверсным выходом первого триггера, выход третьего элемента Н соединен с вторым входом второго элемента ИЛИ, выход первого элемента задеряки подключен к .входу установки в О младших Aq разрядов второго счетчика, прямой выход первого триггера соединен с вторым входом первого элемента НТК,

выход которого соединен со гчетным входом второго триггера, о т л и - ча ю щи и с я тем, что, с целью расширения класса решаемых задач за счет нреобразования заданного числа непрерывных монотонных функций, в : него введены третий счетчик, одноразрядный блок памяти, дешифратор, блок узлов памяти, третий коммутатор,О ретий триггер, четвертый и пятый элементы И, причем вход дешифратора, адресный вход одноразрядного блока памяти и управляющий вход третьего коммутатора соединены с входом зада- jj ния функции преобразователя, выход одноразрядного блока памяти соединен с входом управления реверсом второго счетчика, выходы дешифратора подклю- чены к входам разрешения соответст- 20 вующих узлов памяти блока, адресные

входы которых соединены с выходом третьего счетчика, выходы узлов памяти блока соединены с соответствующими информационными входами третьего коммутатора, выход которог о подключен к кодовому входу второго сумматора, выход которого соединен с информационным входом второго коммутатора выход первого элемента И подключен к счетному входу третьего триггера и к первым входам четвертого и пятого элементов И, к вторым входам которых подключены соответственно прямой и инверсный выходы третьего триггера, выходы четвертого и пятого элементов И соединены соответственно со счетны входом третьего счетчика и тактовым входом второго сумматора, выход второго элемента ИЛИ подключен к входу синхронизации, третьего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1987 |

|

SU1481750A1 |

| Устройство для вычисления функции вида F( @ )= @ | 1987 |

|

SU1418709A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для определения границ микропика на контуре основного пика | 1987 |

|

SU1575209A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

Изобретение относится к вычислительной технике и предназначено для использования в системах управления гибкими автоматизированными производствами, технологическими процессами, в специализированных вычислительных устройствах. Целью изобретения является расширение класса решаемых задач. Для достижения поставленной цели в устройство введены одноразрядный блок памяти, дешифратор, блок узлов памяти, третий коммутатор, третий триггер, четвертый и пятый элементы И, третий счетчик. Дополнительно введенные элементы позволяют реализовать функциональное преобразование заданного числа непрерывных строго монотонных функций путем использования записанных в узлы памяти блока локальных трендов воспроизводимых функций. Расширение класса решаемых задач достигается при незначительном увеличении оборудования и сохранении высоких точностно-временных характеристик. Алгоритм преобразования состоит из двух этапов. На первом этапе развертка функции осуществляется увеличенным шагом в некотором среднем разряде с использованием локальных трендов этого разряда и приращение функции реализуется квантами. На втором этапе ведется развертка мелким шагом в младшем разряде. 1 ил.

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1300466, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-05—Подача