517

СЛ СП

to

входов логических элементов равна 72, а быстродействие, определяемое глубиной схемы, равно 5Ј, где Ј задержка на вентиль. Мультиплексор работает в двух режимах. В режиме коммутатора на его адресные входы подаются переменные х ,, ха, хэ, х4,

составляющие двоичный номер информа1552170л

ционного входа, который подключается к выходу. В режиме универсального логического модуля на информационные входы подается вектор значений (габ- 5 лица интенсивности) реализуемой логической функции F, переменные которой подаются на адресные входы. 1 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексор | 1990 |

|

SU1780185A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Универсальный логический модуль с самоконтролем | 1988 |

|

SU1644125A1 |

| Программируемое устройство | 1991 |

|

SU1789979A1 |

| Универсальный логический модуль с самоконтролем | 1988 |

|

SU1520504A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Многофункциональная ячейка однородной структуры | 1989 |

|

SU1663609A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано в качестве коммутатора или универсального логического модуля при построении устройств цифровой обработки информации. Цель изобретения - упрощение конструкции мультиплексора. Поставленная цель достигается тем, что мультиплексор содержит четыре элемента НЕ 1 - 4, двадцать один элемент ИЛИ 5 - 25, четыре элемента И 26 - 29, четыре адресных входа 30 - 33, шестнадцать информационных входов 34 - 49 и выход 50. Сложность мультиплексора по числу входов логических элементов равна 72, а быстродействие, определяемое глубиной схемы, равно 5Τ, где Τ - задержка на вентиль. Мультиплексор работает в двух режимах. В режиме коммутатора на его адресные входы подаются переменные X1, X2, X3, X4, составляющие двоичный номер информационного входа, который подключается к выходу. В режиме универсального логического модуля на информационные входы подается вектор значений (таблица истинности) реализуемой логической функции F, переменные которой подаются на адресные входы. 1 ил., 1 табл.

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано в качестве коммутатора или универсального логического модуля при построении устройств цифровой обработки информации .

Цель изобретения - упрощение конструкции мультиплексора.

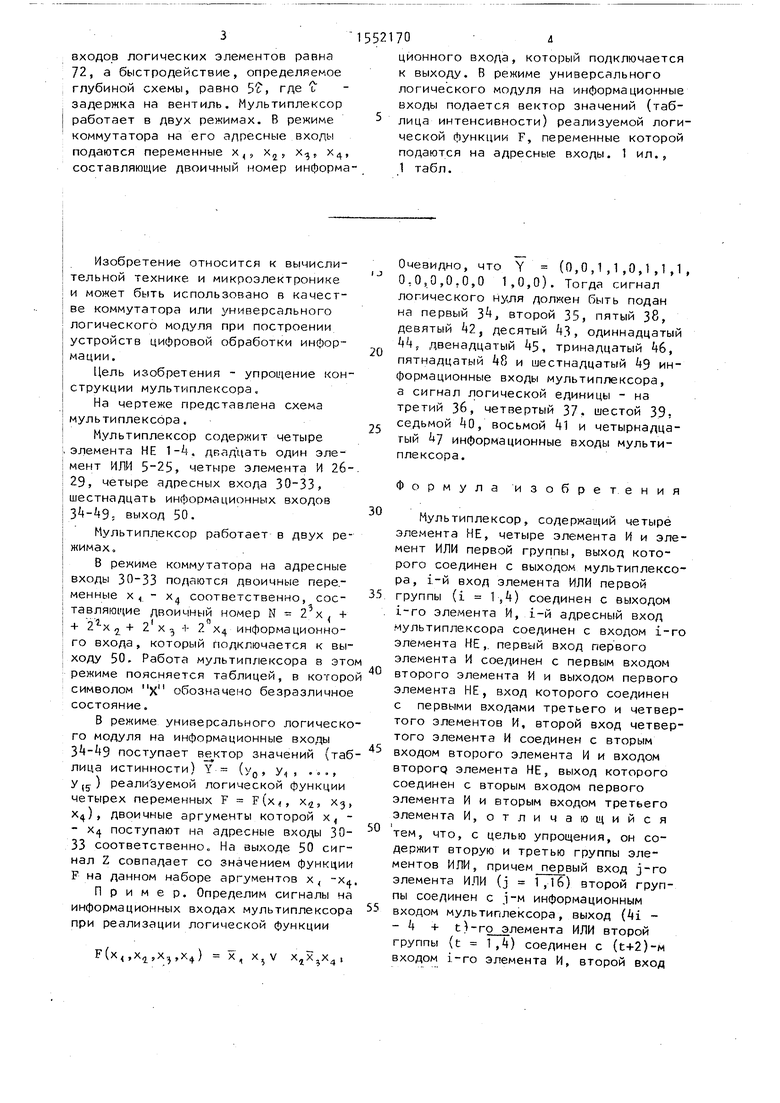

На чертеже представлена схема мультиплексора.Мультиплексор содержит четыре элемента НЕ 1-4, двадцать один элемент ИЛИ , четыре элемента И 26- 29, четыре адресных входа , шестнадцать информационных входов 34-49 выход 50.

Мультиплексор работает в двух режимах.

В режиме коммутатора на адресные входы 30-33 подаются двоичные переменные х - х4 соответственно, сое- тавляющие двоичный номер N - 2эх, +

О)0

+ 2 х э 2 Х4 информационного входа, который подключается к выходу 50, Работа мультиплексора в это

г-

режиме поясняется таблицей, в которо

символом х11 обозначено безразличное состояние.

В режиме универсального логического модуля на информационные входы

34-49 поступает вектор значений (таблица истинности) Y - (у0, у,, , . .., у(5) реализуемой логической функции четырех переменных F - Fix,, х2, xg х), двоичные аргументы которой х4 - - х поступают на адресные входы 30- 33 соответственно. На выходе 50 сигнал Z совпадает со значением функции F на данном наборе аргументов х х. Пример. Определим сигналы на информационных входах мультиплексора при реализации логической функции

Р(х,ха,х,хф) x,x5v ,

0

„

0

0

5

Очевидно, что Y (0,0,1,1,0,1,1,1, 0.0,0,0.0,0 1,0,0). Тогда сигнал логического нуля должен быть подан на первый 3k, второй 35, пятый 38, девятый 42, десятый 43, одиннадцатый 44, цвенадцатый 45, тринадцатый 46, пятнадцатый 48 и шестнадцатый 49 информационные входы мультиплексора, а сигнал логической единицы - на третий 36, четвертый 37. шестой 39- седьмой 40, восьмой 41 и четырнадцатый 47 информационные входы мультиплексора.

Формула изобретения

Мультиплексор, содержащий четыре элемента НЕ, четыре элемента И и элемент ИЛИ первой группы, выход которого соединен с выходом мультиплексора, 1-й вход элемента ИЛИ первой группы (i 1,4) соединен с выходом 1-го элемента И, i-й адресный вход мультиплексора соединен с входом 1-го элемента НЕ, вход первого элемента И соединен с первым входом второго элемента И и выходом первого элемента НЕ, вход которого соединен с первыми входами третьего и четвертого элементов И, второй вход четвертого элемента И соединен с вторым входом второго элемента И и входом второгр элемента НЕ, выход которого соединен с вторым входом первого элемента И и вторым входом третьего элемента И, отличающийся тем, что, с целью упрощения, он содержит вторую и третью группы элементов ИЛИ, причем первый вход j-ro элемента И ПИ (j 1,16) второй группы соединен с i-м информационным входом мультиплексора, выход (4i - - 4 + элемента ИЛИ второй группы (t 1,4) соединен с (t+2)-M входом 1-го элемента И, второй вход

51

(Ш -Ц + t)-ro элемента ИЛИ второй группы соединен с выходом t-ro элемента ИЛИ третьей группы, первый вход первого элемента ИЛИ третьей группы соединен с первым входом второго элемента ИЛИ третьей группы и входом третьего элемента НЕ, выход которого соединен с первым входом третьего элемента ИЛИ третьей группы

521706

и первым входом четвертого элемента i ИЛИ третьей группы, второй вход которого соединен с вторым входом второго элемента ИЛИ третьей группы и входом четвертого элемента НЕ, выход которого соединен с вторым входом первого элемента ИЛИ третьей группы и вторым входом третьего элемента Ю ИЛИ третьей группы.

| Авторское свидетельство СССР | |||

| If 1487023, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Интегральные микросхемы: Справочник | |||

| / Под ред | |||

| Б.В.Тарабрима | |||

| - М.: Радио и связь, 1984, с | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

Авторы

Даты

1990-03-23—Публикация

1988-07-04—Подача