Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора, а также для реализации всех логических функций трех переменных.

Цель изобретения - упрощение мультиплексора.

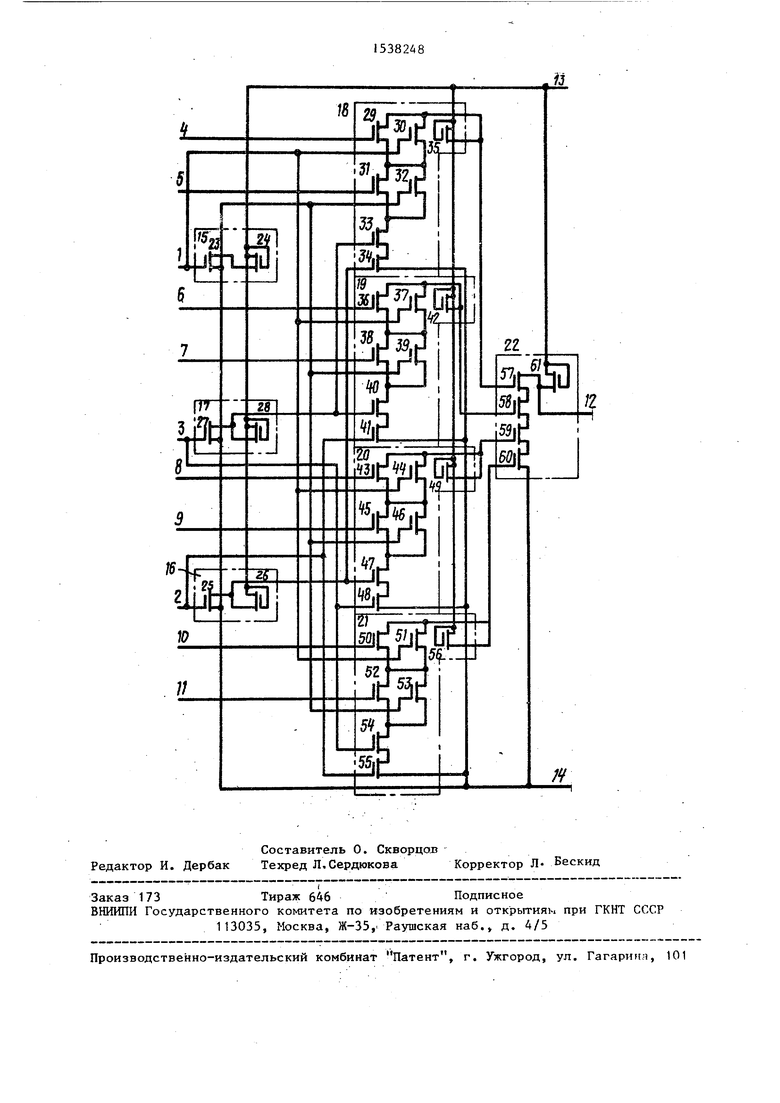

На чертеже представлена электрическая принципиальная схема предлагаемого мультиплексора.

Мультиплексор содержит три информационные шины 1-3, восемь настроечных шин 4-11, выход 12, две шины 13

и 14 питания, первый 15, второй 16 и третий 17 элементы НЕ, первый 18, второй 19, третий 20 и четвертый 2t элементы 2-2ИЛИ-4И-НЕ и элемент

И-НЕ 22.

Первый элемент НЕ 15 выполнен на переключательном 23 и нагрузочном 24 транзисторах, второй элемент НЕ 16 - на переключательном 24 и нагрузочном 26 транзисторах а третий элемент НЕ 17 - на переключательном 27 и нагрузочном 28 транзисторах. Первый элемент 2-2ИЛИ-4И-НЕ 18 выполнен на шести переключательных 29-34 и одном нагрузочном 35 транзисторах, второй элемент 2-2ИЛИ-4И-НЕ 19-на шести переключательных 36-41 и одном нагрузочном 42 транзисторах, третий элемент 2-2ИЛИ- 4И-НЕ 20 - на шести переключательных 43-48 и одном нагрузочном 49 транзисторах, а четвертый элемент 2-2ИЛИ-4И- НЕ 21 - на шести переключательных 50- 55 и одном нагрузочном 56 транзисто- pax.

Элемент И-НЕ 22 выполнен на четырех переключательных 57-60 и одном нагрузочном 61 транзисторах.

Элемент 2-2ИЛИ-4И-НЕ реализует, логическую функцию Q) (zj Vz})- () xz5 zg, где z, i 1,6 - значение

игнала на i-м входе элемента.

Первая, информционная шина 1 муль- типлексора соединена с входом первого элемента НЕ 15 (затвор транзистора 23)

1 третьими входами первого элемента 2-2ИЛИ-4И-НЕ 18 (затвор транзистора

30), второго элемента 2-2ИЛИ-4И-НЕ 19 (затвор транзистора 37), третьего

элемента 2-2ИЛИ-4И-НЕ 20 (затвор тран зистора 44) и четвертого элемента 2-2ИЛИ-4И-НЕ 21 (затвор транзистора

51).

Вторая информационная шина 2 мультиплексора соединена с входом второго элемента НЕ 16 (затвор транзистора 25) и пятыми входами второго элемента 2-2ИЛИ-4И-НЕ 19 (затвор транзистора 41) и четвертого элемента 2-2ИЛИ-4И-НЕ 21 (затвор транзистора 55).

Третья информационная шина 3 мультиплексора соединена с входом третьего элемента НЕ 17 (затвор транзистора 27) и шестыми входами третьего элемента 2-2ИЛИ-4И-НЕ 20 (затвор транзистора 48) и четвертого элемента 2-2ИЛИ- 4И-НЕ 21 (затвор транзистора 54).

Первая 4 и вторая 5 настроечные Шины мультиплексора соединены соответственно с первым и вторым входами первого элемента 2-2ИЛИ-4И-НЕ 18 (затворы транзисторов 29 и 31), третья 6 И четвертая 7 настроечные шины мультиплексора -. соответственно с первым и Вторым входами второго элемента 2-2ИЛИ-4И-НЕ 19 (затворы транзисторов 36 и 38), пятая 8 и шестая 9 настроечные шины мультиплексора - соответст

Венно с первым и вторым входами третьего элемента 2-2Ш1И-4И-НЕ 20 (затворы транзисторов 43 и 45), а седьмая 10 й восьмая 11 настроечные шины мульти , -- ю

15382484

плексора соединены соответственно

5

0

5

0

5

0

5

0

5

первым и вторым входами четвертого элемента 2-2ШШ-4Н-НЕ 21 (затворы транзисторов 50 и 52).

Выход первого элемента НЕ 15 (сток транзистора 23) соединен с четвертыми входами первого 18, второго 19, третьего 20 и четвертого 21 элементов 2-2ИЛИ-4И-НЕ (соответственно затворы транзисторов 32, 39, 46 и 53).

Выход второго элемента НЕ 16 (сток транзистора 26) соединен с пятыми входами первого 18 и третьего 20 элементов 2-2ИЛИ-4И-НЕ (соответственно затворы транзисторов 34 и 47).

Выход третьего элемента НЕ 17 (сток транзистора 28) соединен с шестыми входями первого 18 и второго 19 элементов 2-2ИЛИ-4И-НЕ (соответственно затворы транзисторов 33 и 40).

Выходы элементов 2-2ИЛИ-4И-НЕ 18- 21 (соответственно стоки транзисторов 35, 42, 49 и 56) соединены с входами элемента И-НЕ 22 (соответственно затворы транзисторов 57-60), выход которого (сток транзистора 61) соединен с выходом 12 модуля.

Элементы НЕ 15-17, элементы 2-2ИЛИ- 4И-НЕ 18-21 и элемент И-НЕ 22 соединены между шинами 13 и 14 питания.

Мультиплексор работает в двух, режимах.

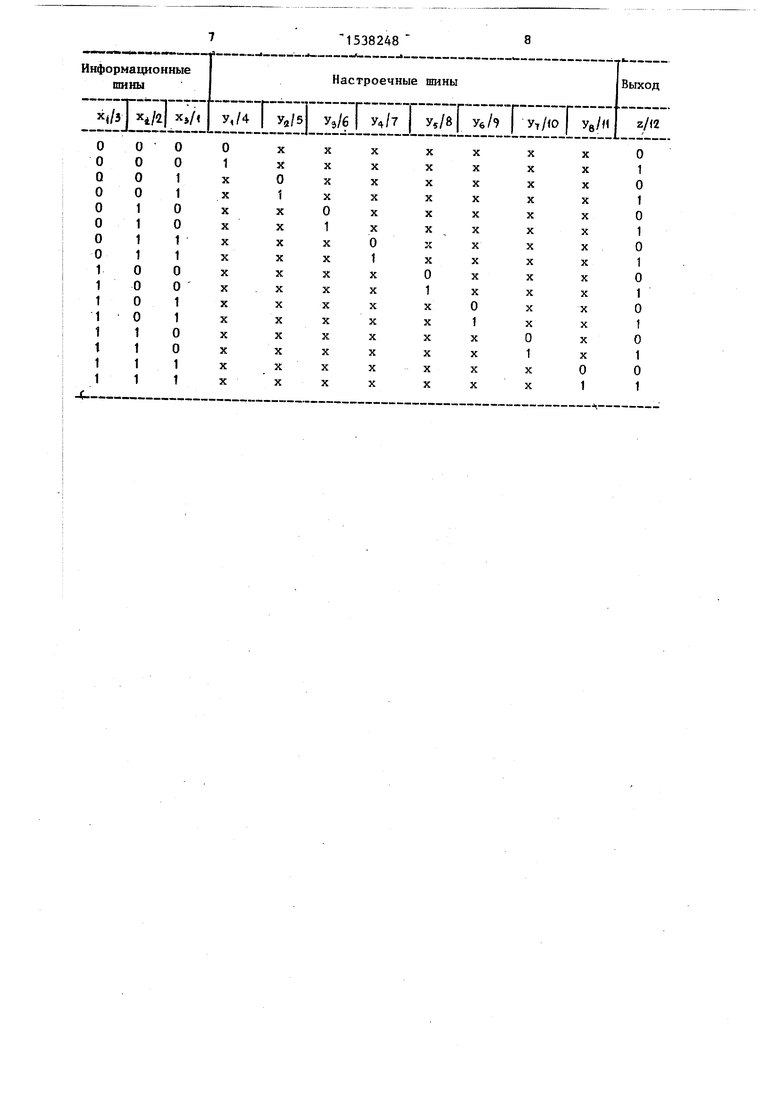

В режиме коммутатора на информационные шины 1-3 подаются двоичные переменные соответственно х, хги х,, определяющие двоичный номер N 2х,+ + 2 х„ -I- 2°х + 1 настроечной шины, сигнал с которой приходит на выход 12 мультиплексора (очевидно N 1,8). Работа мультиплексора в этом режиме поясняется таблицей (х - безразличное состояние).

В режиме универсального логического модуля на информационные шины 1-3 также подаются двоичные переменные х, хг и х,, которые являются аргументами реализуемой устройством некоторой логической функции трех переменных f(xi, хэ) компоненты вектора значений которой Y(y,,у4,..., Уц) подаются соответственно на наст- роечные .шины 4т11 (где у;, i 1,8 - значение f (х,, х,) на(1-1)м наборе переменных х (, х).

Таким образом, сигнал настройки 11 бГо,1Т на i-й настроечной шине мультиплексора совпадает со значением yj. На выходе 12 мультиплексора сигнал z

совпадает со значением f(x,, х3) на данном наборе переменных х,, х }.

Первообразная мультиплексора имеетt вид; f(x.(,x3,U) (U, V ха()хах,

(Ц4У х3)( хъ),- (UgVx dJfeVxjx S

(UT x5)(Ue VX3)x,l x, .

Пример. Определяют сигналы на .настроечных шинах мультиплексора при (реализации логической функции f (x,Xj) х,. Очевидно, вектор ее значений V (у,,уг,...,ув) (0,1,0,0, 0,1,1,1). Тогда компоненты вектора настройки U имеют значения: U,

U О, Uu Ue U7 Ug

U:

соединены соответственно с (21-1)-й и 21-й настроечными иинами мультиплексора, первая информационная шина которого соединена с входом первого элемента НЕ и третьим входом 1-го элемента 2-2ИЛИ-4И-НЕ, четвертый вход которого соединен с выходом первого элемента НЕ, вторая информационная

«Q шина мультиплексора соединена с пятыми входами второго и четвертого элементов 2-2ИЛИ-4И-НЕ и входом второго элемента НЕ, выход которого соединен с пятыми входами первого и третьего

,5 элементов 2-2ИЛИ-4И-НЕ, третья информационная шина мультиплексора соединена с шестыми входами третьего и четвертого элементов 2-2ИЛИ-4И-НЕ и входом третьего элемента НЕ, выход

1. Следовательно, сигнал логического нуля должен быть подан на первую 4, третью 6, четвертую 7 и пятую 8 настроечные шины, а сигнал логической которого соединен с шестыми входами ницы - на вторую 5, шестую 9, седьмую первого и второго элементов 2-2ИЛИ4И-НЕ, выход 1-го элемента 2-2ИЛИ-4И- НЕ соединен с i-м входом элемента И-НЕ, выход которого соединен с выхо- 25 дом мультиплексора, каждый элемент 2-2ИЛИ-4И-НЕ содержит семь полевых транзисторов, затвор первого из которых соединен с первым входом элемента, а сток соединен со стоком второго по30

10 и восьмую 11 настроечные шины мультиплексора.

Предлагаемый мультиплексор характеризуется простой конструкцией и широкими функциональными возможностями. Сложность известного устройства по числу входов логических элементов составляет 55, тогда как сложность предлагаемого мультиплексора равна 39 (три элемента НЕ содержат по два, четыре элемента 2-2ИЛИ-4И-НЕ - по семь и элемент И-НЕ - пять полевых транзисторов), что как минимум в 1,4 раза меньше сложности известного .устройства.

Формула изобретения

Мультиплексор, содержащий три информационных и восемь настроечных шин, две шины питания, выполненные на МОП- транзисторах, шесть из которых образуют три элемента НЕ, отличающийся тем, что, с целью упрощения, содержит один элемент И-НЕ и четыре элемента 2-2ИЛИ-4И-НЕ, первый и второй входы 1-го из которых (,4)

35

40

45

левого транзистора, затвор которого соединен с вторым входом элемента, а Ьсток соединен с истоком первого полевого транзистора и стоками третьего и четвертого полевых транзисторов, затворы которого соединены соответственно с третьим и четвертым входами элемента, а истоки соединены со стоком пятого полевого транзистора, затвор которого соединен с пятым входом элемента, а исток соединен со стоком шестого полевого транзистора, затвор которого соединен с шестым входом элемента, а исток соединен с первой шиной питания, вторая шина питания соединена с затвором и стоком седьмого полевого транзистора, исток которого .соединен с выходом элемента и стоками первого и второго полевых транзисто- ров.

соединены соответственно с (21-1)-й и 21-й настроечными иинами мультиплексора, первая информационная шина которого соединена с входом первого элемента НЕ и третьим входом 1-го элемента 2-2ИЛИ-4И-НЕ, четвертый вход которого соединен с выходом первого элемента НЕ, вторая информационная

шина мультиплексора соединена с пятыми входами второго и четвертого элементов 2-2ИЛИ-4И-НЕ и входом второго элемента НЕ, выход которого соединен с пятыми входами первого и третьего

5 элементов 2-2ИЛИ-4И-НЕ, третья информационная шина мультиплексора соединена с шестыми входами третьего и четвертого элементов 2-2ИЛИ-4И-НЕ и входом третьего элемента НЕ, выход

0 которого соединен с шестыми входами первого и второго элементов 2-2ИЛИ

левого транзистора, затвор которого соединен с вторым входом элемента, а Ьсток соединен с истоком первого полевого транзистора и стоками третьего и четвертого полевых транзисторов, затворы которого соединены соответственно с третьим и четвертым входами элемента, а истоки соединены со стоком пятого полевого транзистора, затвор которого соединен с пятым входом элемента, а исток соединен со стоком шестого полевого транзистора, затвор которого соединен с шестым входом элемента, а исток соединен с первой шиной питания, вторая шина питания соединена с затвором и стоком седьмого полевого транзистора, исток которого .соединен с выходом элемента и стоками первого и второго полевых транзисто- ров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

| Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ | 1991 |

|

SU1811002A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1274148A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Программируемый логический модуль | 1984 |

|

SU1233274A1 |

Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора, а также для реализации всех логических функций трех переменных. Цель изобретения - упрощение мультиплексора. Поставленная цель достигается тем, что мультиплексор содержит три информационные шины, восемь настроечных шин, две шины питания, один выход, три элемента НЕ, четыре шестивходовых элемента 2-2ИЛИ-4И-НЕ и один четырехвходовый элемент И-НЕ. Мультиплексор работает в двух режимах - коммутатора и универсального логического модуля. В режиме коммутатора на информационные шины подаются двоичные переменные, определяющие двоичный номер настроечной шины, сигнал с которой происходит на выход мультиплексора. В режиме универсального логического модуля на информационные шины также подаются двоичные переменные, которые являются аргументами реализуемой устройством некоторой логической функции трех переменных, компоненты вектора значений которой подаются на настроечные шины. Мультиплексор обладает широкими функциональными возможностями, простой конструкцией и однородной структурой. 1 ил., 1 табл.

| Универсальный логический модуль | 1983 |

|

SU1119003A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Справочник/Под ред | |||

| Б.Н.Файзула- ева, Б.В | |||

| Тарабрина | |||

| - М | |||

| Радио и связь, 1987, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-01-23—Публикация

1988-07-06—Подача