ел ел to

Cfc

3Ч

Изобретение относится к вычислительной и измерительной технике и может использоваться для построения арифметических и модернизации измерительных цифровых устройств.

Цель изобретения - упрощение устройства.

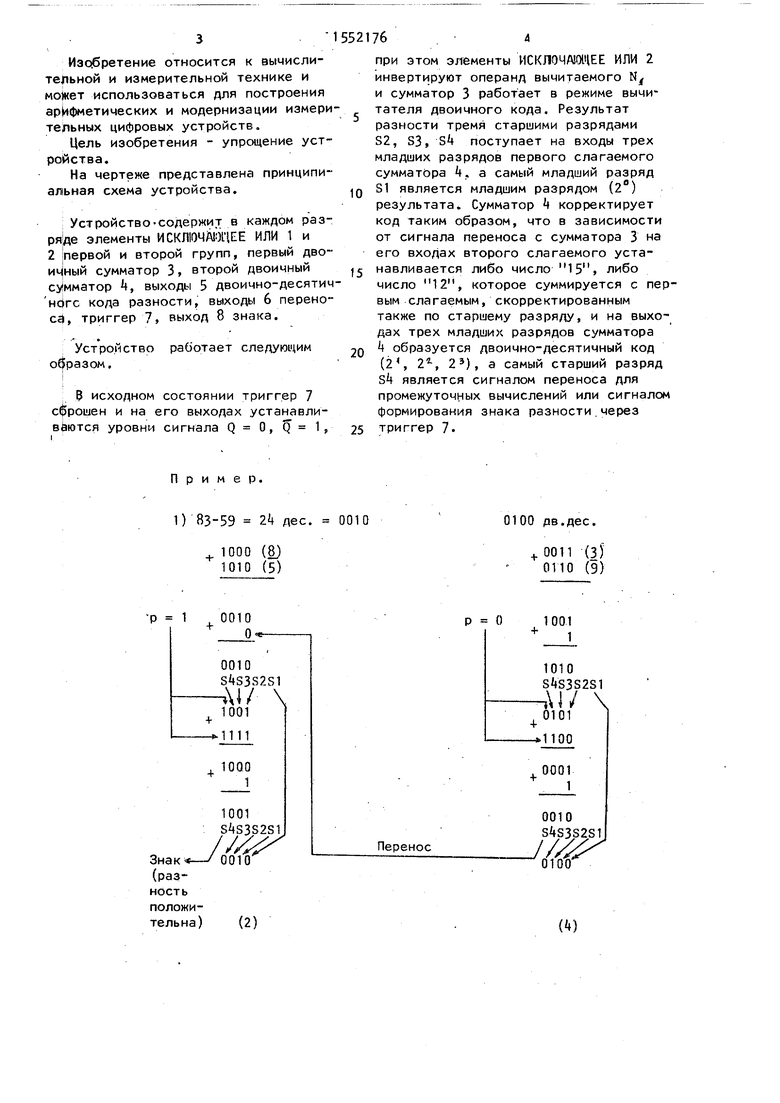

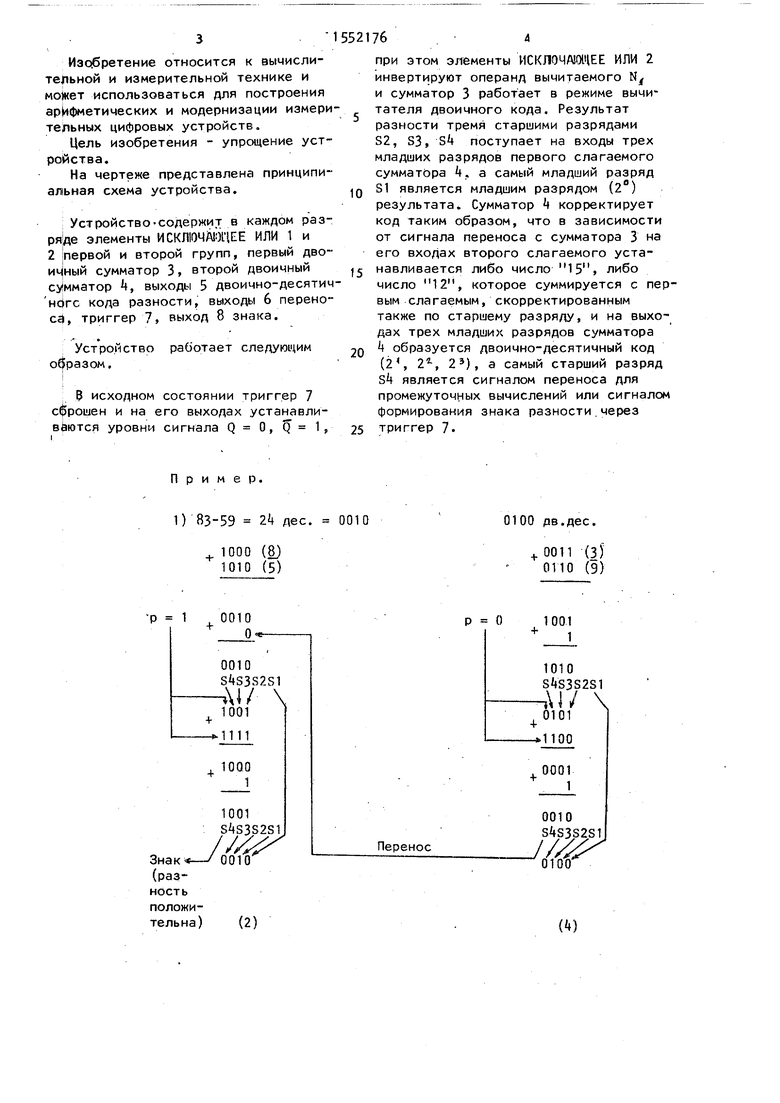

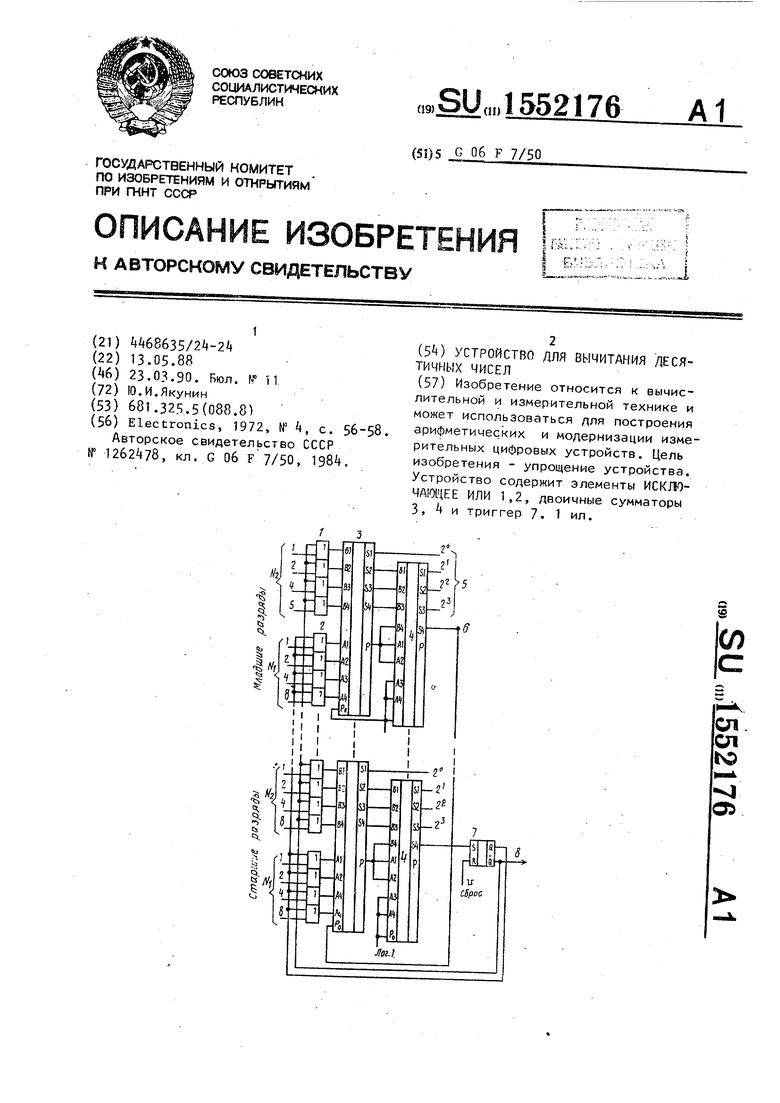

На чертеже представлена принципиальная схема устройства.

Устройство-содержит в каждом разряде элементы ИСКЛЮЧАЙТЕ ИЛИ 1 и 2 первой и второй групп, первый двоичный сумматор 3, второй двоичный сумматор А, выходы 5 двоично-десятич- ногс кода разности, выходы 6 переноса, триггер 7, выход 8 знака.

10

Устройство образом.

работает следующим

9 исходном состоянии триггер 7 спрошен и на его выходах устанавливаются уровни сигнала Q О, Q 1,

5521764

при этом элементы ИСКЛОЧАВДЕЕ ИЛИ 2 инвертируют операнд вычитаемого N,, и сумматор 3 работает в режиме вычи- тателя двоичного кода. Результат разности тремя старшими разрядами S2, S3, S поступает на входы трех младших разрядов первого слагаемого сумматора k, а самый младший разряд S1 является младшим разрядом (2е) результата. Сумматор корректирует код таким образом, что в зависимости от сигнала переноса с сумматора 3 на его входах второго слагаемого устаJ5 навливается либо число 15, либо

число 12, которое суммируется с первым слагаемым, скорректированным также по старшему разряду, и на выходах трех младших разрядов сумматора

2Q k образуется двоично-десятичный код (24, , 23), а самый старший разряд Sk является сигналом переноса для промежуточных вычислений или сигналом формирования знака разности через

25 триггер 7.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для вычитания десятичных чисел | 1984 |

|

SU1262478A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

Изобретение относится к вычислительной и измерительной технике и может использоваться для построения арифметических и модернизации измерительных цифровых устройств. Цель изобретения - упрощение устройства. Устройство содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 1, 2, двоичные сумматора 3, 4 и триггер 7. 1 ил.

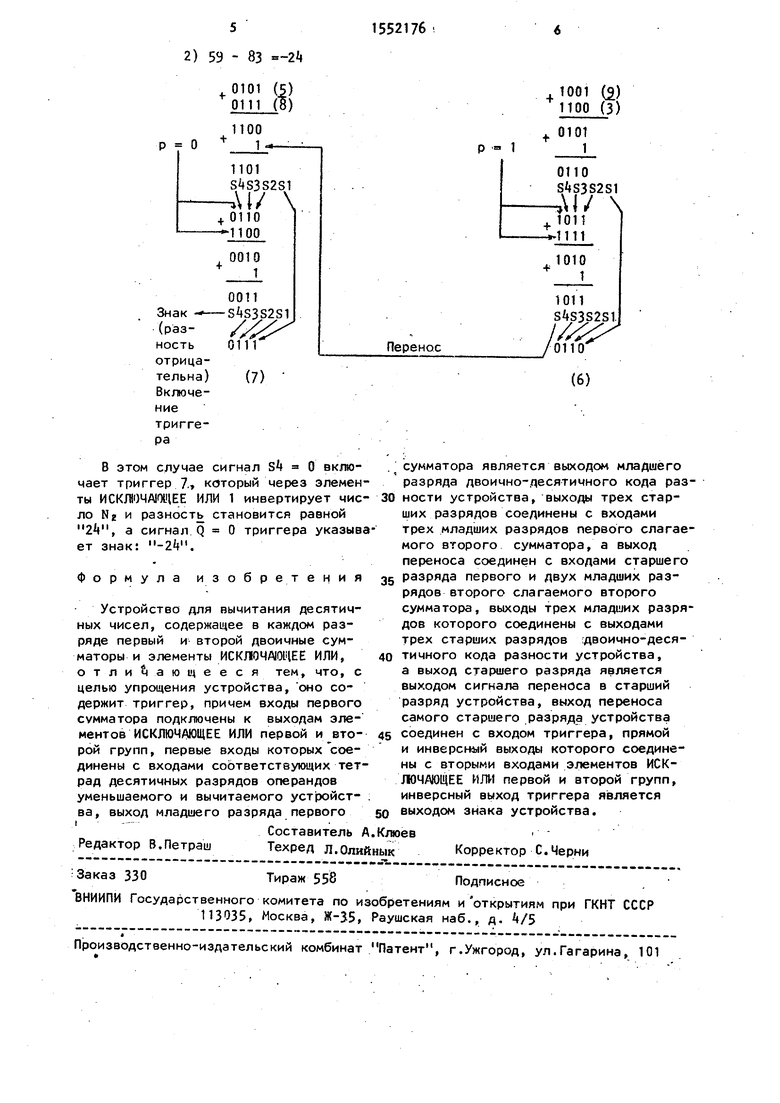

Пример.

1) 83-59 21 дес. 0010

(2)

0100 ре.дес.

0

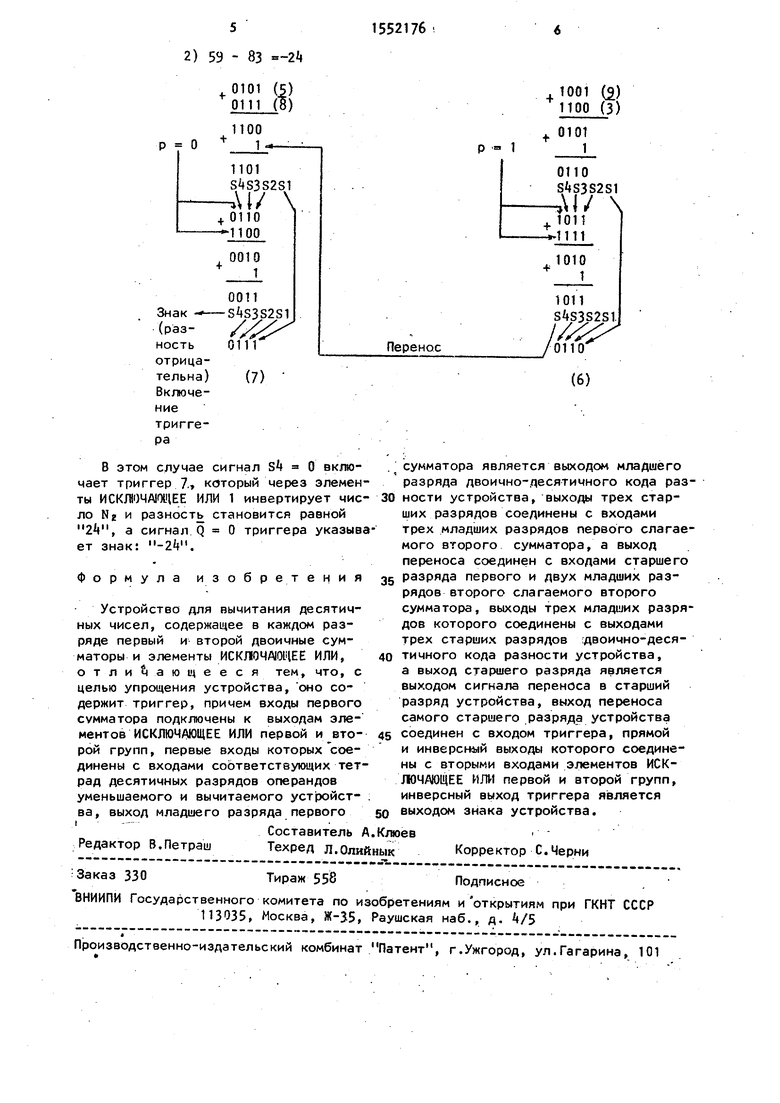

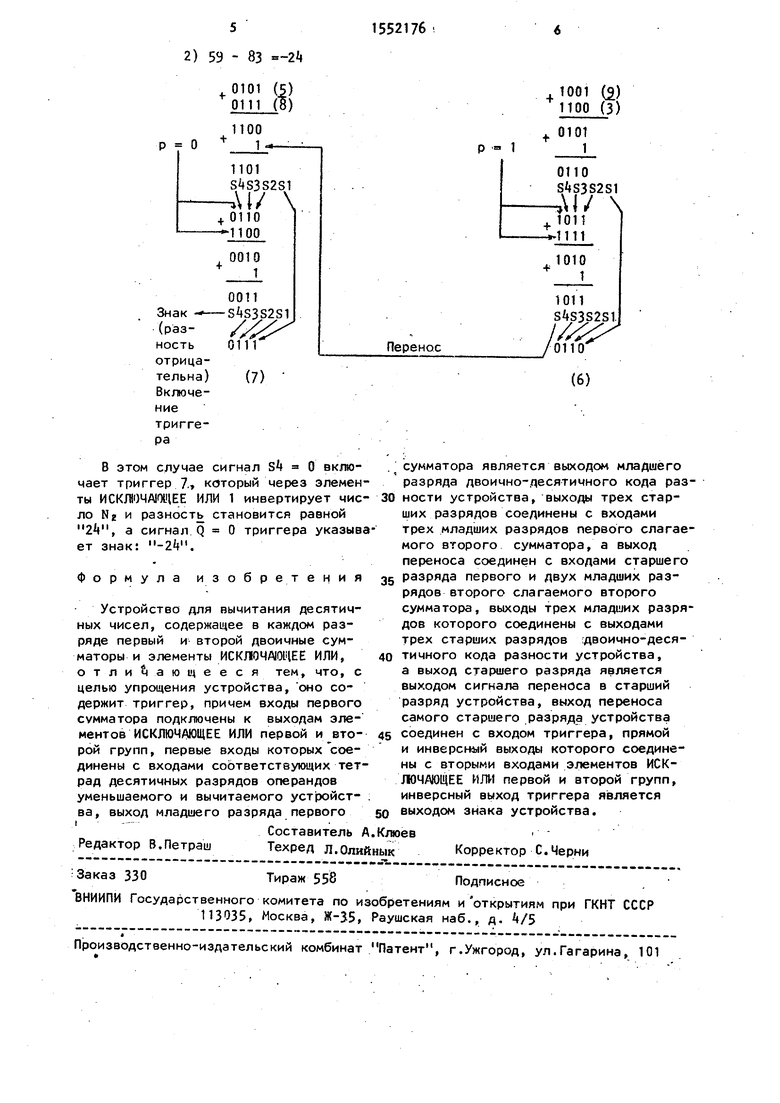

2) 59 - 83 «-2k

Включение

триггера

В этом случае сигнал Sk 0 вклю- сумматора является выходом младшего чает триггер 7, который через элемен- разряда двоично-десятичного кода раз- ты ИСКЛЮЧАЮЩЕЕ ИЛИ 1 инвертирует чис- 30 ности устройства, выходы трех стар- ло Nz и разность становится равной ших разрядов соединены с входами

сигнал Q О триггера указыва- трех младших разрядов первого слагае 2V, а ет знак

-2.

мого второго сумматора, а выход переноса соединен с входами старшего

Формула изобретения

Устройства для вычитания десятичных чисел, содержащее в каждом разряде первый и второй двоичные сумматоры и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающееся тем, что, с целью упрощения устройства, оно содержит триггер, причем входы первого сумматора подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп, первые входы которых соединены с входами соответствующих тетрад десятичных разрядов операндов уменьшаемого и вычитаемого устройст5Q выходом знака устройства.

ва, выход младшего разряда первого

Составитель А.Клюев -1 1 :ТРаШ Техред Л.Олийнык Корректор С.Черни

Заказ 330тираж 558Подписи

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

мого второго сумматора, а выход переноса соединен с входами старшего

разряда первого и двух младших разрядов второго слагаемого второго сумматора, выходы трех младших разрядов которого соединены с выходами трех старших разрядов двоично-десятичного кода разности устройства, а выход старшего разряда является выходом сигнала переноса в старший разряд устройства, выход переноса самого старшего разряда устройства

соединен с входом триггера, прямой и инверсный выходы которого соединены с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп, инверсный выход триггера является

выходом знака устройства.

| Electronics, 1972, № 4, с | |||

| Устройство для вычитания десятичных чисел | 1984 |

|

SU1262478A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1990-03-23—Публикация

1988-05-13—Подача