со

4 VI Ю

Изобретение относится к вычислительной технике и может использоваться в арифметических блоках обработки комплексных чисел в последовательном коде.

Известно устройство для вычисления модуля комплексного числа, содержащее регистры, сумматоры, коммутатор и элементы контроля.

Недостатком устройства являются большие затраты оборудования.

Известно устройство для вычисления модуля комплексного числа, содержащее первый, второй и третий сумматоры, первый и второй мультиплексоры, первый и второй сумматоры по модулю два, сумматор по модулю три, блок свертки по модулю три, первую и вторую группы сумматоров (четвертый и пятый сумматоры) из М - 1 сумматоров в каждой группе, где М - количество тетрад двоично-десятичного кода действительной и мнимой части комплексного числа, причем входы информационных разрядов действительной и мнимой частей числа устройства соединены соответственно с входами первого слагаемого и с инверсным входом второго слагаемого первого сумматора, вход информационных разрядов мнимой части числа устройства соединен с входом первого слагаемого второго сумматора, выход которого соединен с первым информационным входом первого мультиплексора, второй информационный вход которого соединен с выходом третьего сумматора, вход первого слагаемого которого соединен с входом информационных разрядов действительной части числа устройства, информационный и контрольный разряды которого соединены соответственно с выходом первого мультиплексора и с выходом блока свертки по модулю три, входы контрольных разрядов действительной и мнимой частей числа устройства соединены соответственно с входами первого и второго слагаемых сумматора по модулю три, выходы разрядов которого соединены соответственно с выходами первых слагаемых первого и второго сумматоров по модулю два, входы вторых слагаемых которых объединены и соединены с управляющими входами первого и второго мультиплексоров и с выходом знакового разряда первого сумматора, входы младших информационных разрядов мнимой и действительной частей числа устройства соединены соответственно с первым и вторым информационными входами второго мультиплексора, выходы первого и второго мультиплексоров первого и второго сумматоров по модулю два соединены соответственно с входами блока свертки по модулю

три, входы первого, второго, третьего и четвертого информационных разрядов М-й (старшей) тетрады второго слагаемого второго сумматора соединены соответственно

с входами второго, третьего, четвертого информационных разрядов М-й тетрады действительной части числа устройства и с входом нулевого потенциала устройства, входы первого, второго, третьего и четвер0 того разрядов М-й тетрады второго слагаемого третьего сумматора соединены соответственно с входами второго, третьего, четвертого информационных разрядов М-й тетрады мнимой части числа устройства

5 и с входом нулевого потенциала устройства, входы второго, третьего и четвертого информационных разрядов К-й тетрады действительной части числа устройства соединены соответственно с входами первого, второго,

0 третьего разрядов слагаемого К-го сумматора первой группы (К 1, М -1), вход первого слагаемого младшего информационного разряда (К + 1)-й тетрады действительной части числа устройства соединен с входами

5 первого и третьего разрядов второго слагаемого К-го сумматора первой группы, входы второго, третьего и четвертого информационных разрядов К-й тетрады мнимой части числа устройства соединены соответствен0 но с входами первого, второго и третьего разрядов первого слагаемого К-го сумматора второй группы, вход первого информационного разряда (К + 1)-й тетрады мнимой части числа устройства соединен с входами

5 первого и третьего разрядов второго слагаемого К-го сумматора второй группы, вход четвертого разряда первого слагаемого и входы второго и четвертого разрядов второго слагаемого, а также вход переноса каж0 дого сумматора первой и второй групп соединены с входом нулевого потенциала устройства, входы разрядов К-го сумматора первой группы соединены с входами соответствующих разрядов К-й тетрады второго

5 слагаемого второго сумматора, выходы разрядов К-го сумматора второй группы соединены с входами соответствующих разрядов К-й тетрадЫ второго слагаемого третьего сумматора.

0 Недостатком устройства являются большие затраты оборудования.

Целью изобретения является упрощение устройства.

Указанная цель достигается тем, что в

5 устройство, содержащее с первого по пятый сумматоры и коммутатор, выходы второго и третьего сумматоров соединены с первым и вторым информационными входами коммутатора, выход которого является выходом устройства, вход первого слагаемого третьего сумматора соединен с выходом суммы пятого сумматора, вход второго слагаемого второго сумматора подключен к выходу суммы четвертого сумматора, введены первый и второй регистры, счетчик, с первого по шестой триггеры, элемент И-НЕ и с первого по четвертый элементы И, причем тактовый вход устройства соединен со счетным входом счетчика, синхровходами первого и второго регистров, третьего, четвертого и пятого триггеров, второго и третьего сумматоров, вход начальной установки устройства подключен к входам сброса первого, второго, третьего и четвертого триггеров счетчика, первого и второго регистров, второго и третьего сумматоров и входу установки пятого триггера, информационные входы первого и второго регистров являются входами первого и второго операндов устройства и подключены к информационным входам первого и второго триггеров соответственно, выходы которых соединены с первыми входами соответственно первого и четвертого элементов И, вторые инверсные входы которых объединены между собой, с первым входом элемента И-НЕ, первыми синхровходами второго и третьего сумматоров и подключены к выходу первого разряда счетчика, выходы первого и четвертого элементов И соединены с входами первого слагаемого четвертого и пятого сумматоров, входы второго слагаемого которых подключены к выходам второго и третьего элементов И соответственно, первые входы которых соединены с выходами четвертых разрядов первого и второго регистров, а вторые входы объединены и подключены к выходу элемента И-НЕ, второй вход которого обьединен с вторыми синхровходами второго и третьего сумматоров, синхровходами первого и второго триггеров и подключен к выходу второго разряда счетчика, выходы переноса четвертого и пятого сумматоров соединены с информационными входами третьего и четвертого триггеров соответственно, выходы которых соединены с входами переноса четвертого и пятого сумматоров соответственно, выходы первых разрядов первого и второго регистров соединены с входами первого слагаемого и инверсными входами второго слагаемого первого сумматора соответственно, вход переноса которого соединен с выходом пятого триггера, а выход переноса - с информационными входами пятого и шестого триггеров, синхровход шестого триггера соединен с выходом четвертого разряда счетчика, а выход соединен с управляющим входом коммутатора, выходы пятых разрядов первого и второго регистров соединены

с входом второго слагаемого третьего сумматора и входом первого слагаемого второго сумматора соответственно

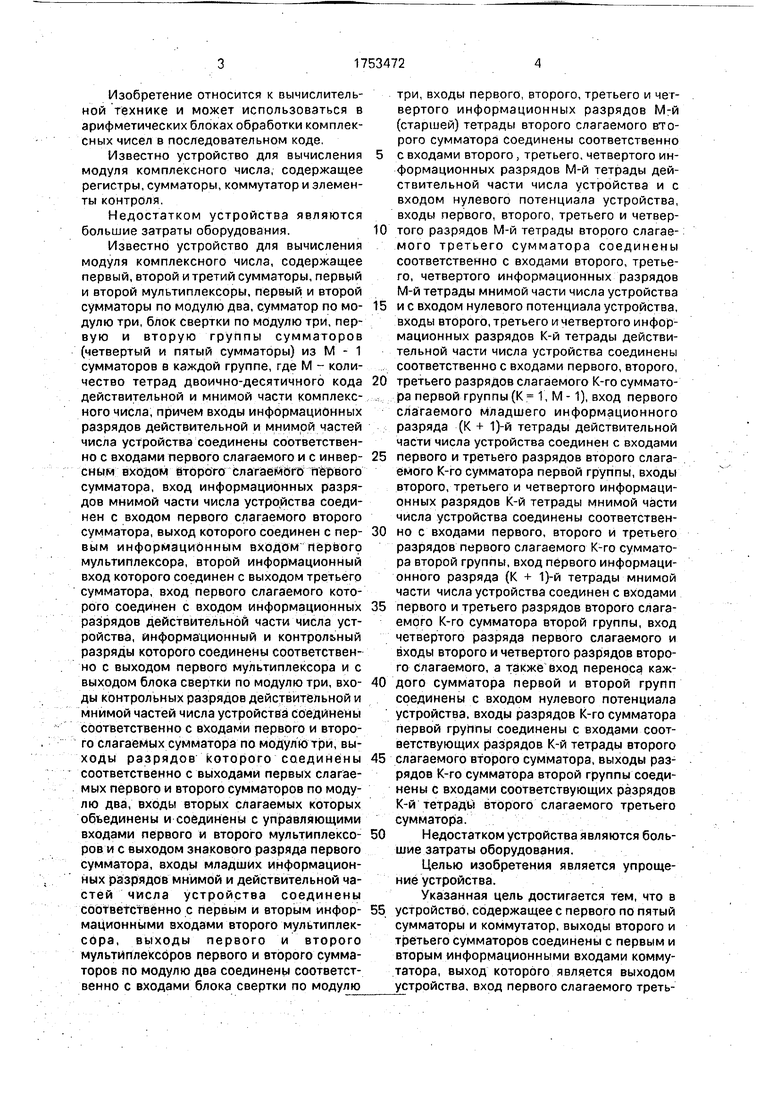

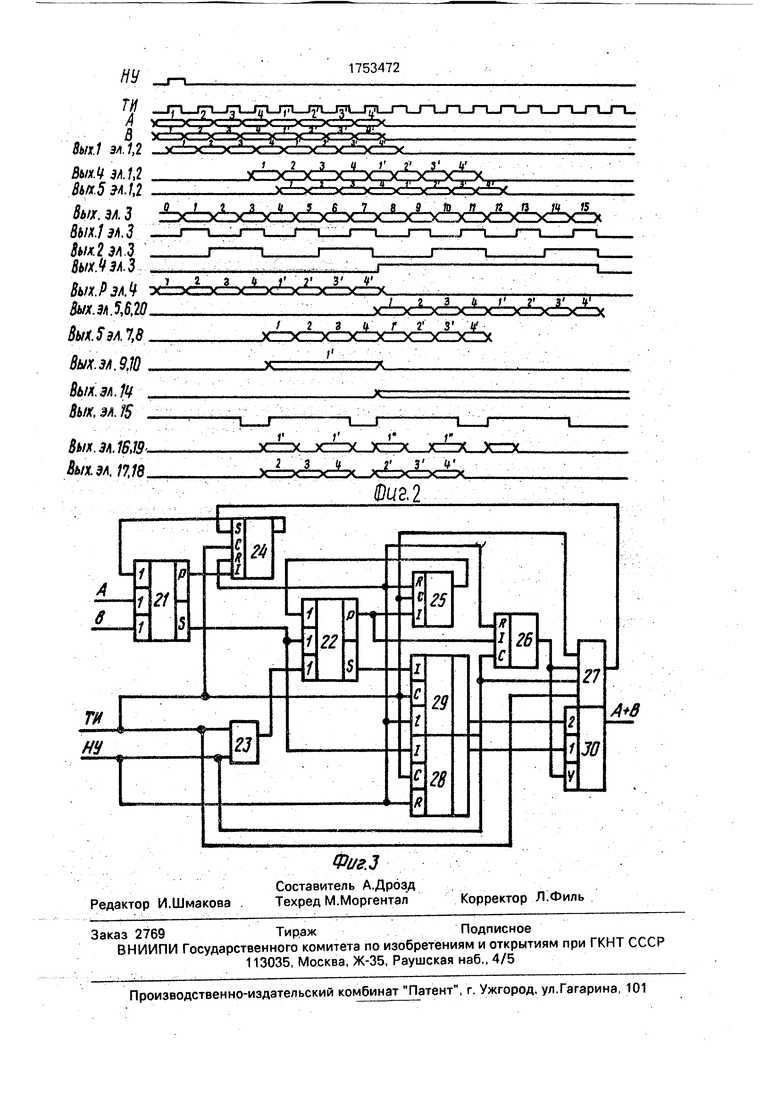

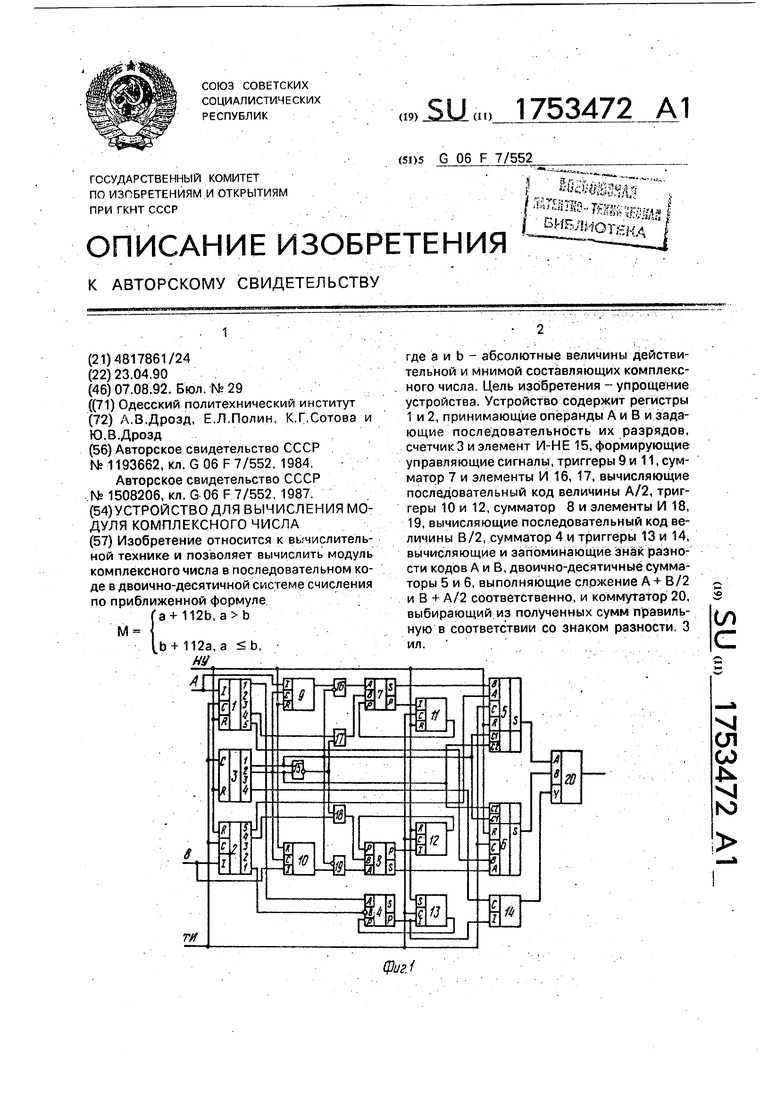

На фиг. 1 приведена схема устройства;

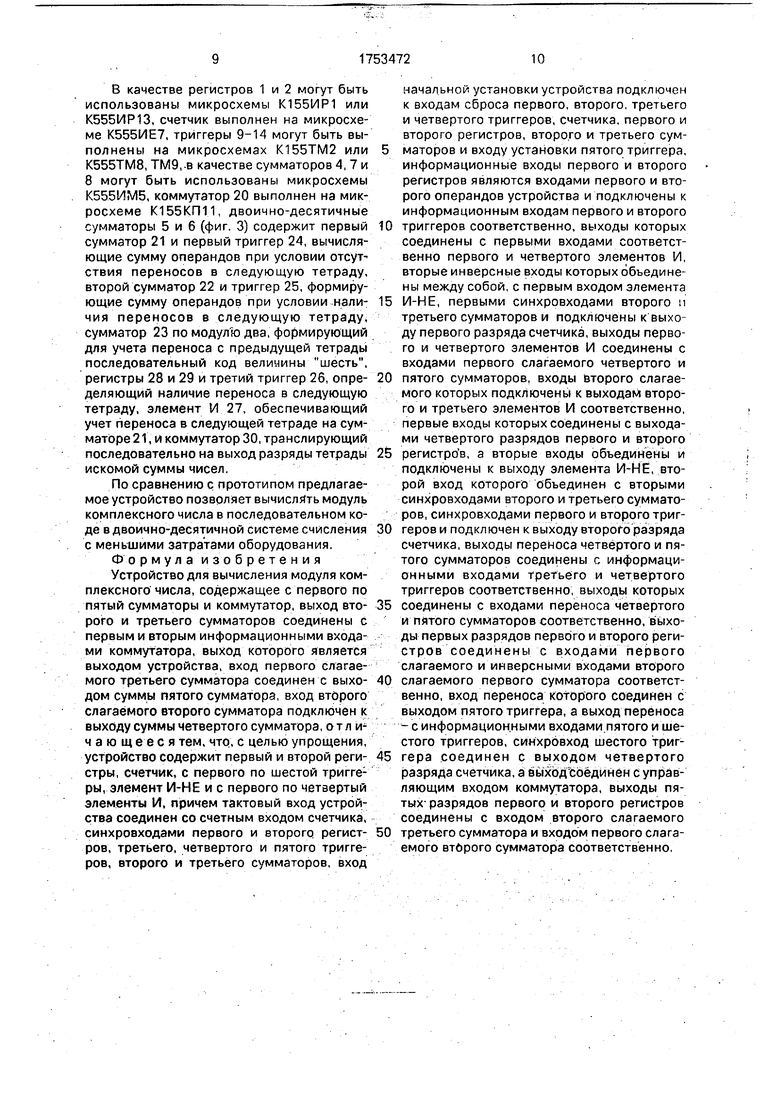

на фиг. 2 - временные диаграммы, поясняющие работу устройства; на фиг. 3 - схема сумматора.

Устройство содержит первый 1 и второй

2 регистры, счетчик 3, первый-пятый сумматоры 4-8, первый-шестой триггеры 9-14, элемент И-НЕ 15, первый-четвертый элементы И 16-19 и коммутатор 20, причем вход первого слагаемого третьего сумматора 6 соединен с выходом суммы пятого сумматора 8, а вход второго сумматора 5 соединен с выходом суммы четвертого сумматора 7, выходы второго 5 и третьего 6 сумматоров подключены к первому и второму информационным входам коммутатора 20, выход которого является выходом устройства, вход начальной установки устройства подключен к входам сброса первого 1 и второго 2 регистров, первого 9, второго 10,

третьего 11 и четвертого 12 триггеров, второго 5 и третьего 6 сумматоров и входу установки пятого триггера 13, тактовый вход устройства соединен со счетным входом счетчика 3, синхровходами первого 1 и второго 2 регистров, третьего 11, четвертого 12 и пятого 13 триггеров, второго 5 и третьего б сумматоров, информационные входы первого 1 и второго 2 регистров являются входами первого и второго операндов

устройства и подключены к информационным входам первого 9 и второго 10 триггеров соответственно, выходы которых соединены соответственно с первыми входами первого 16 и четвертого 19 элементов

И соответственно, вторые инверсные входы которых объединены между собой и первым входом элемента И-НЕ 15, а также первыми синхровходами второго 5 и третьего 6 сумматоров и подключены к первому выходу

счетчика 3, а выходы первого и четвертого элементов И 16 и 19 соединены соответственно с входами первого слагаемого четвертого 7 и пятого 8 сумматоров, входы второго слагаемого которых подключены соответственно к выходам второго 17 и третьего 18 элементбв И, первые входы которых соединены соответственно с четвертыми выходами первого 1 и второго 2 регистров, а вторые входы объединены между собой и соединены с выходом элемента И-НЕ 15, второй вход которого объединен с вторыми синхровходами второго 5 и третьего 6 сумматоров и синхровходами первого 9 и второго 10 триггеров и подключен к второму выходу счетчика 3, выходы переноса четвертого 7 и

пятого 8 сумматоров соединены соответственно с информационными входами третьего 11 и четвертого 12 триггеров, выходы которых соединены соответственно с выходами переноса четвертого 7 и пятого 8 сум- маторов, выходы первого 1 и второго 2 регистров соединены соответственно с входами первого слагаемого и инверсным входом второго слагаемого первого сумматора 4, вход переноса которого соединен с выхо- дом пятого триггера 13, а выход переноса подключен к информационным входам пятого 13 и шестого 14 триггеров, синхровхо- ды шестого триггера 14 соединены с четвертым выходом счетчика 3, а выход со- единен с управляющим входом коммутатора 20, пятый выход первого регистра 1 соединен с входом второго слагаемого третьего сумматора б, а пятый выход регистра 2 соединен с входом первого слагаемо- го второго сумматора 5.

Устройство работает следующим образом.

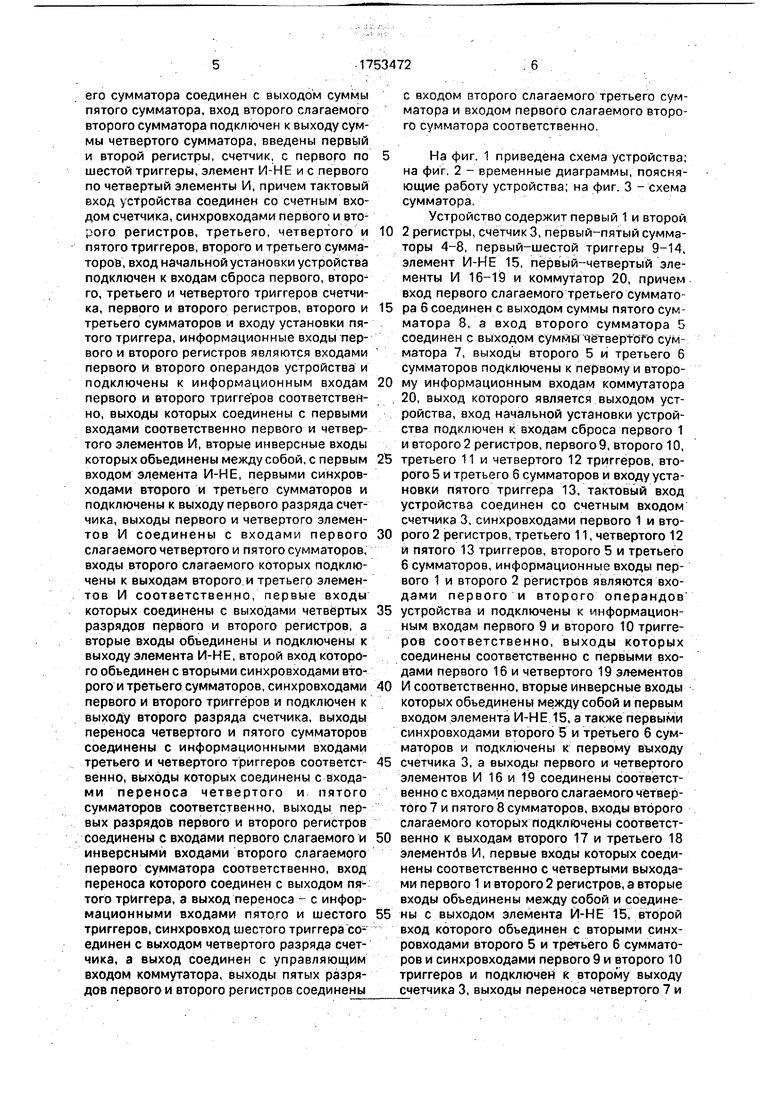

В начальный момент времени на вход начальной установки устройства поступает импульс НУ, сбрасывающий в нулевое состояние триггеры 9-12, регистры 1 и 2, счетчик 3, а также устанавливающий в исходное состояние сумматоры 5 и 6 и в единичное состояние триггер 13. На тактовый вход устройства поступают синхроимпульсы типа меандр ТИ, тактирующие работу устройства. Они подаются на синхровходы триггеров 11-13, регистров 1 и 2, счетный вход счетчи- ка 3, синхровходы сумматоров 5 и 6. На входы операндов устройства поступают последовательно разряды мантисс прямых кодов (начиная с младших разрядов) составляющих А и В комплексного числа К А + jB. На временных диаграммах показаны две тетрады разрядов операндов, пронумерованные от 1 до 4 разряды первой тетрады и от 1 до 4 разряды второй, С первого, четвертого и пятого выходов регистров 1 и 2 снимается последовательность импульсов, показанная на временных диаграммах. Счетчик 3 формирует последовательность сигналов, которая также показана на временных диаграммах. В триггеры 9 и 10 заносится сигнал по заднему фронту второго выхода счетчика. На второй инверсный вход первого элемента И 16 и первый инверсный вход четвертого элемента И 19 поступает значение первого разряда второй тетрады и сигнал с первого выхода счетчика. На их выходах получается последовательный код 0101 или 0000 чисел пять или ноль для единичного и нулевого значений первого разряда следующей тетрады,

На элементе И-НЕ 15 формируется сигнал, принимающий нулевое значение в четвертых разрядах тетрады, последовательности разрядов, снимаемых с четвертых выходов первого 1 и второго 2 регистров. На втором 17 и третьем 18 элементах И выполняется перемножение этих последовательностей на сигнал с выхода элемента И-НЕ 15. Таким образом формируется последовательность разрядов операндов с обнуленными четвертыми разрядами тетрад. Их сложение производится с кодами 0101 или 0000 с выходов первого 16 и четвертого 19 элементов И. Эти коды поступают на входы первого слагаемого четвертого 7 и пятого 8 сумматоров. На входы второго слагаемого этих сумматоров поступают сигналы с выходов второго 17 и третьего 18 эпементов И соответственно.

С первых выходов первого 1 и второго 2 регистров сигнал поступает на входы первого и инверсного второго слагаемого первого сумматора 4, выполняющего вычитание кодов А - В в дополнительном коде с учетом переноса, задерживаемого на такт на триггере 13, единичное начальное значение которого обеспечивает добавление единицы младшего разряда, По окончании вычитания значение знака разности с выхода переноса сумматора 4 принимается в шестой триггер 14 по переднему фронту сигнала с четвертого выхода счетчика 3. Сумматоры 7 и 8 выполняют сложение кодов с учетом переносов, задерживаемых на такт на триггерах 11 и 12, и при этом определяют коды А/2 и В/2 соответственно. На входы слагаемых А и В двоично-десятичных сумматоров 5 и 6 поступают значения b и а/2 и а и Ь/2 соответственно, На синхровходы СИ сумматоров 5 и 6 поступает значение с первого разряда счетчика, а на их вторые синхровходы С2 - значение с второго разряда счетчика. При этом на выходе двоично-десятичного сумматора 5 вычисляется сумма b + а/2, а на выходе двоично-десятичного сумматора б - сумма а + Ь/2. Эти значения поступают на первый и второй информационные входы коммутатора 20. Сигнал с выхода шестого триггера 14 поступает на управляющий вход коммутатора 20. В зависимости от значения этого сигнала коммутатор 20 пропускает на выход результат сложения а + Ь/2, если Зн 0, или результат b + а/2, если Зн 1. Таким образом на выходе устройства, подключенном к выходу коммутатора 20, определяется приближенное значение М модуля комплексного числа А «1+05 по формуле

ta + Ь/2, а Ь, где а I «i I ; b + а/2, а b, b I аг I.

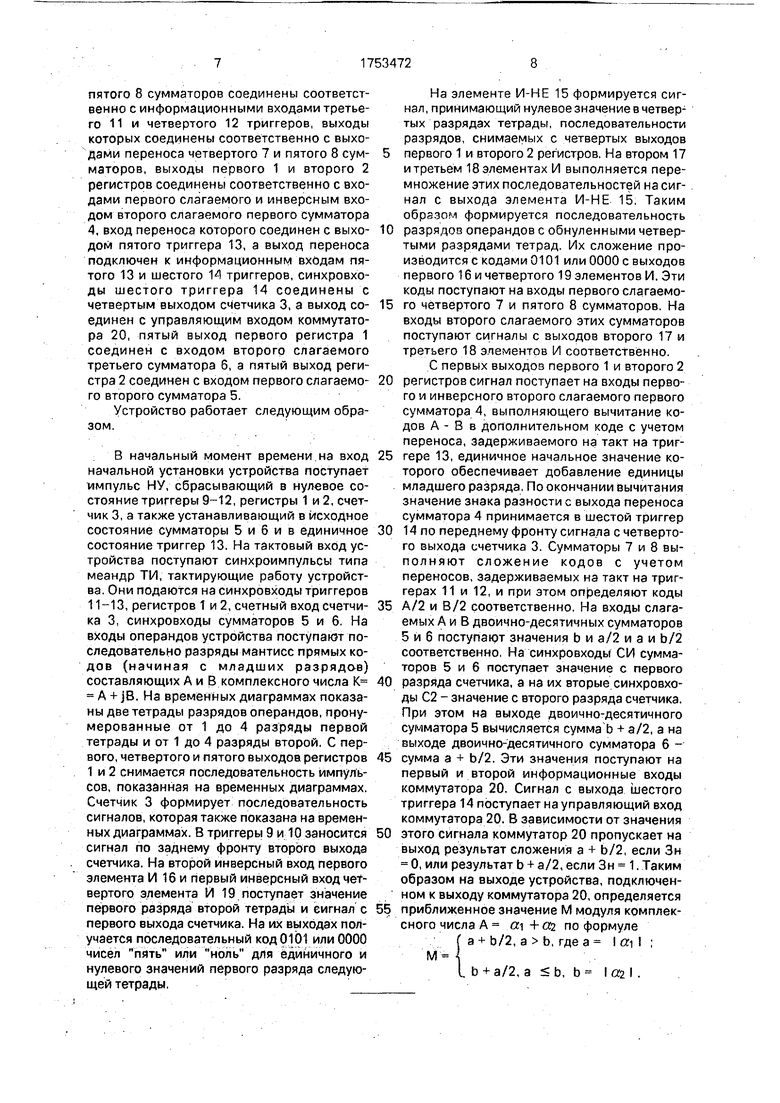

В качестве регистров 1 и 2 могут быть использованы микросхемы К155ИР1 или К555ИР13, счетчик выполнен на микросхеме К555ИЕ7, триггеры 9-14 могут быть выполнены на микросхемах К155ТМ2 или К555ТМ8, ТМ9, в качестве сумматоров 4, 7 и 8 могут быть использованы микросхемы К555ИМ5, коммутатор 20 выполнен на микросхеме К155КП11, двоично-десятичные сумматоры 5 и 6 (фиг 3) содержит первый сумматор 21 и первый триггер 24, вычисляющие сумму операндов при условии отсутствия переносов в следующую тетраду, второй сумматор 22 и триггер 25, формирующие сумму операндов при условии наличия переносов в следующую тетраду, сумматор 23 по модулнэ два, формирующий для учета переноса с предыдущей тетрады последовательный код величины шесть, регистры 28 и 29 и третий триггер 26, определяющий наличие переноса в следующую тетраду, элемент И 27, обеспечивающий учет переноса в следующей тетраде на сумматоре 21, и коммутатор 30, транслирующий последовательно на выход разряды тетрады искомой суммы чисел.

По сравнению с прототипом предлагаемое устройство позволяет вычислить модуль комплексного числа в последовательном коде в двоично-десятичной системе счисления с меньшими затратами оборудования.

Формула изобретения

Устройство для вычисления модуля комплексного числа, содержащее с первого по пятый сумматоры и коммутатор, выход второго и третьего сумматоров соединены с первым и вторым информационными входами коммутатора, выход которого является выходом устройства, вход первого слагаемого третьего сумматора соединен с выходом суммы пятого сумматора, вход второго слагаемого второго сумматора подключен к выходу суммы четвертого сумматора, отличающееся тем, что, с целью упрощения, устройство содержит первый и второй регистры, счетчик, с первого по шестой триггеры, элемент И-НЕ и с первого по четвертый элементы И, причем тактовый вход устройства соединен со счетным входом счетчика, синхровходами первого и второго регистров, третьего, четвертого и пятого триггеров, второго и третьего сумматоров, вход

начальной установки устройства подключен к входам сброса первого, второго третьего и четвертого триггеров, счетчика, первого и второго регистров, второго и третьего сум- маторов и входу установки пятого триггера, информационные входы первого и второго регистров являются входами первого и второго операндов устройства и подключены к информационным входам первого и второго

триггеров соответственно, выходы которых соединены с первыми входами соответственно первого и четвертого элементов И, вторые инверсные входы которых объединены между собой, с первым входом элемента

И-НЕ, первыми синхровходами второго и третьего сумматоров и подключены к выходу первого разряда счетчика, выходы первого и четвертого элементов И соединены с входами первого слагаемого четвертого и

пятого сумматоров, входы второго слагаемого которых подключены к выходам второго и третьего элементов И соответственно, первые входы которых соединены с выходами четвертого разрядов первого и второго

регистров, а вторые входы объединены и подключены к выходу элемента И-НЕ, второй вход которого объединен с вторыми синхровходами второго и третьего сумматоров, синхровходами первого и второго триггеров и подключен к выходу второго разряда счетчика, выходы переноса четвертого и пятого сумматоров соединены с информационными входами третьего и четвертого триггеров соответственно, выходы которых

соединены с входами переноса четвертого и пятого сумматоров соответственно, выходы первых разрядов первого и второго регистров соединены с входами первого слагаемого и инверсными входами второго

слагаемого первого сумматора соответственно, вход переноса которого соединен с выходом пятого триггера, а выход переноса - с информационными входами пятого и шестого триггеров, синхровход шестого триггера соединен с выходом четвертого разряда счетчика, а выход соединен с управляющим входом коммутатора, выходы пятых разрядов первого и второго регистров соединены с входом второго слагаемого

третьего сумматора и входом первого слагаемого второго сумматора соответственно

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1635173A1 |

Изобретение относится к вычислительной технике и позволяет вычислить модуль комплексного числа в последовательном коде в двоично-десятичной системе счисления по приближенной формуле (a + 112b, b + 112a, a b, М. где а и b - абсолютные величины действительной и мнимой составляющих комплексного числа. Цель изобретения - упрощение устройства. Устройство содержит регистры 1 и 2, принимающие операнды А и В и задающие последовательность их разрядов, счетчик 3 и элемент И-НЕ 15, формирующие управляющие сигналы, триггеры 9 и 11, сумматор 7 и элементы И 16, 17, вычисляющие последовательный код величины А/2, триггеры 10 и 12, сумматор 8 и элементы И 18, 19, вычисляющие последовательный код величины В/2, сумматор 4 и триггеры 13 и 14, вычисляющие и запоминающие знак разности кодов А и В, двоично-десятичные сумматоры 5 и 6, выполняющие сложение А + В/2 и В + А/2 соответственно, и коммутатор 20, выбирающий из полученных сумм правильную в соответствии со знаком разности 3 ил. (Л С

Аи/ ал 1,2 jcbcb ±ix±xibcfz c±x±zx

Вы Ч м/,2 8ых5мЦ

Лмг.мЗ ЬсЬсЪсЪсЬсЪсЬ

Зш./,3

Алс2элЗ

&яг.0Л1.3

Вых.Рэл.4 х г /х.зд.5;5,2.

.5м7,5

8bfX.3A.9JO

Вых.эл.П , Вых. ЗА. 15 .

Вш.эк.1639. Вь/х.эл. 1,18

JL

2;21 ь1

. Х

Фиг. 2

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля комплексного числа | 1987 |

|

SU1508206A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-07—Публикация

1990-04-23—Подача