ел

ел

СЛ

00

ел ел

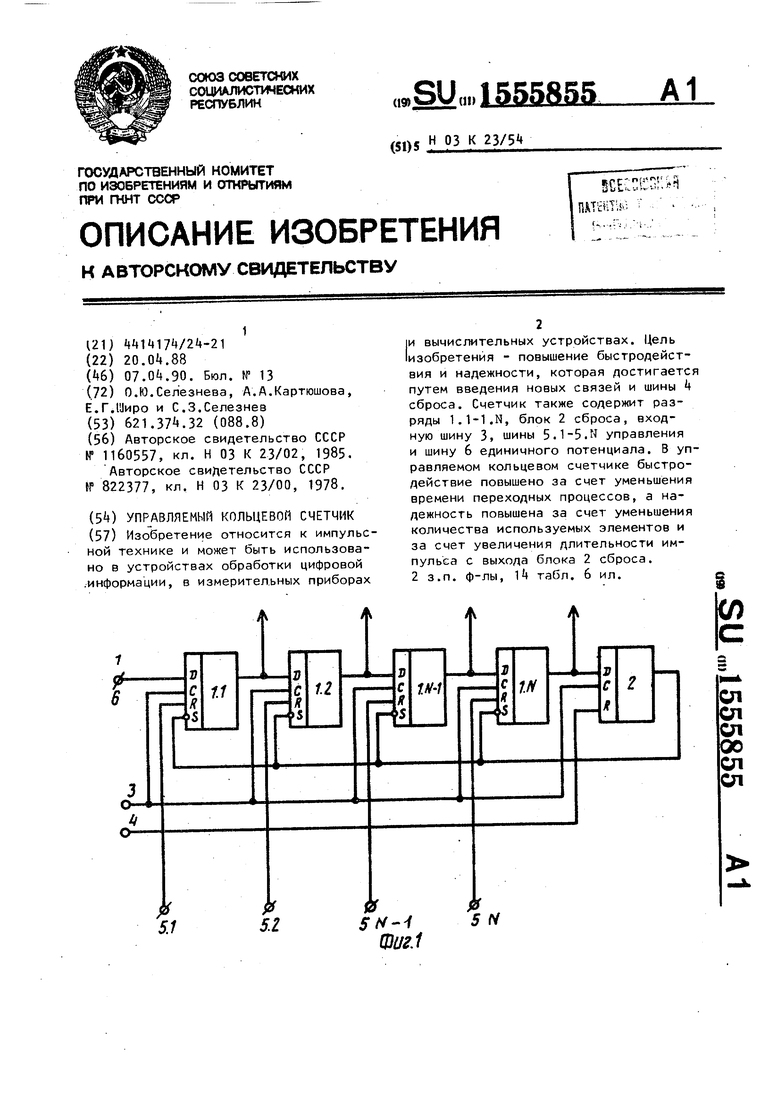

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки цифровой информации, в измерительных приборах и вычислительных устройствах.

Целью изобретения является повышение быстродействия и надежности, которая достигается путем уменьшения времени переходных процессов, за JQ счет увеличения длительности импульса сброса и сокращения амплитудных затрат.

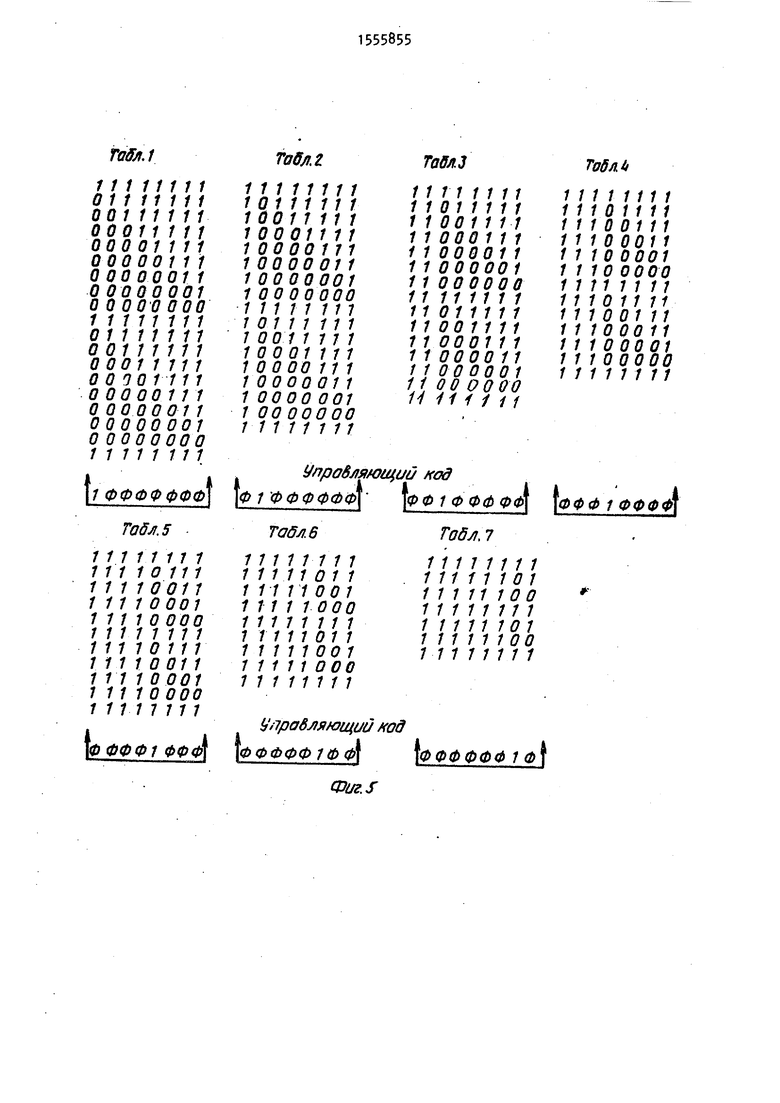

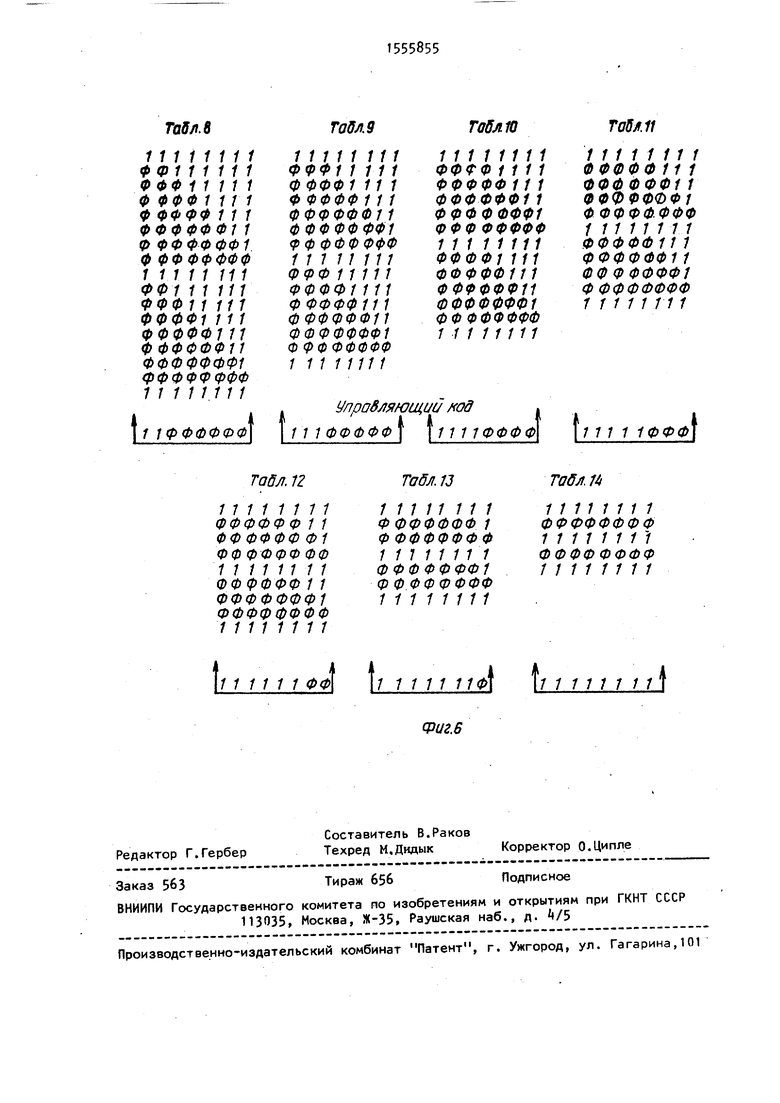

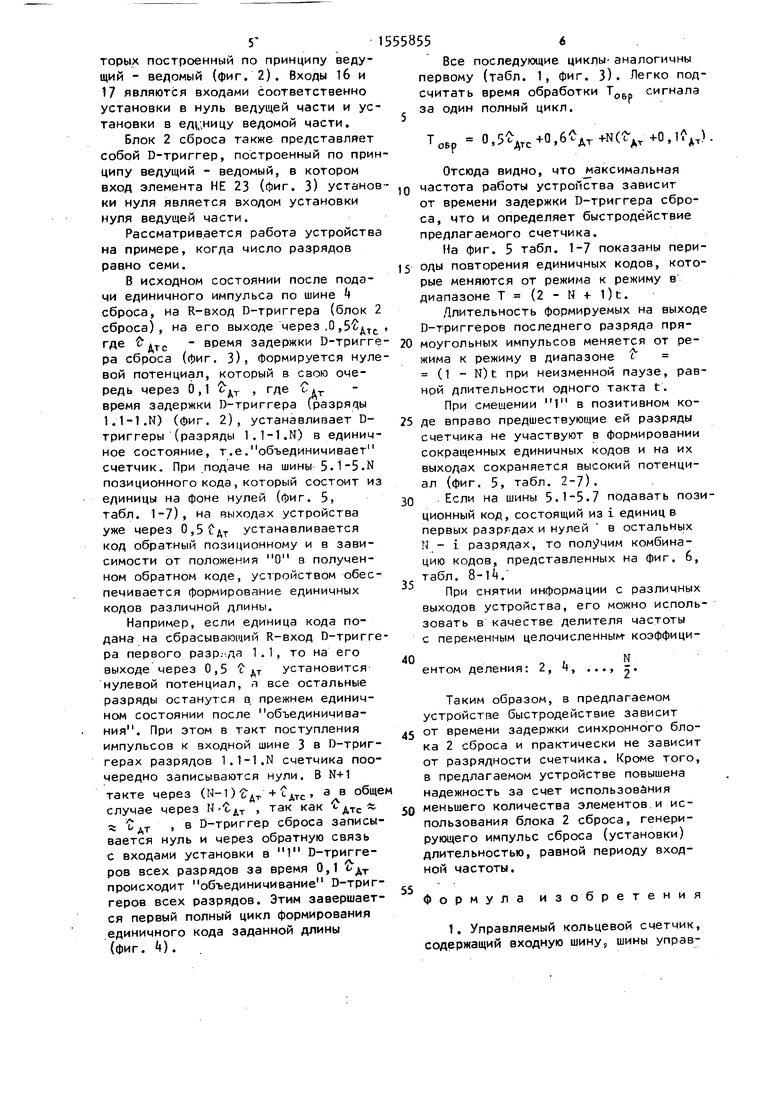

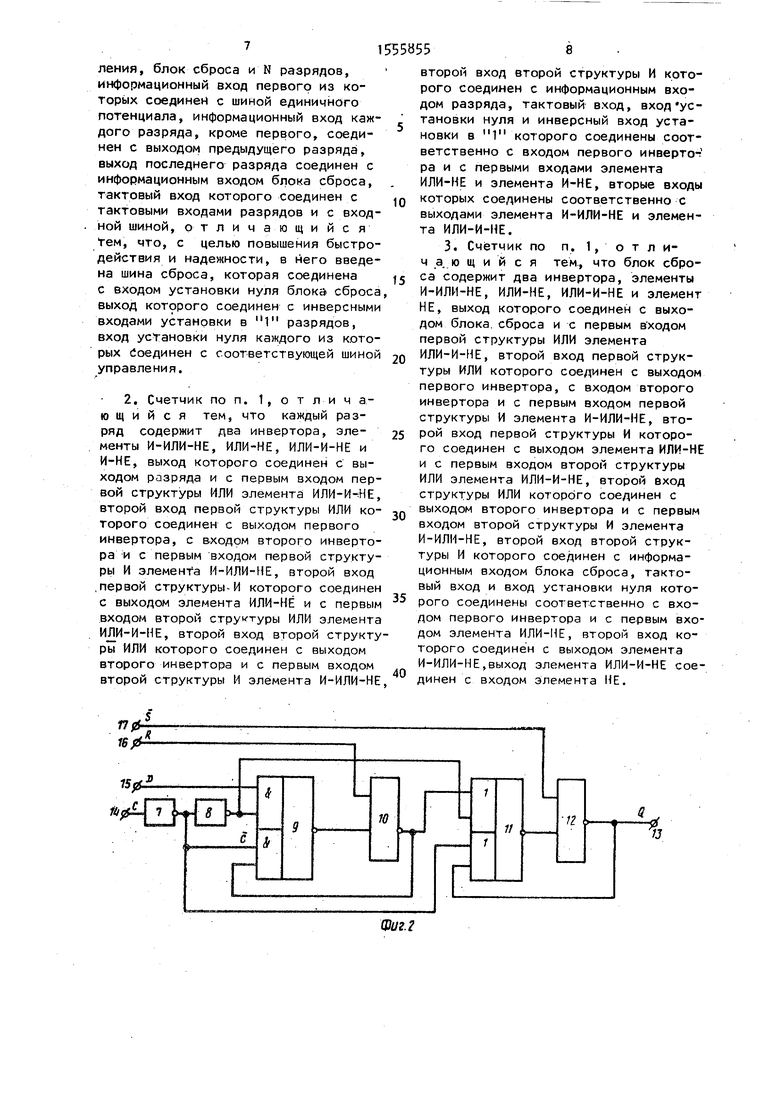

На фиг. 1 приведена структурная схема управляемого кольцевого счет- $ чика; на фиг. 2 - пример реализации разряда устройства; на фиг. 3 - пример реализации блока сброса; на фиг. k - потенциальные диаграммы работы семиразрядного устройства; на 20 фиг. 5 и 6 - таблицы состояний элементов устройства при различных кодах на шинах управления.

На фиг. 1 обозначены: разряды 1.1-1.N, блок 2 сброса, входная шина 25 3, шина k сброса, шины 5.1-5.N управления и шина 6 единичного потенциала.

Информационный вход разряда 1.1 соединен с шиной 6 единичного потенциала, информационные входы разрядов ™ 1.2, 1.3, 1 .N и блока 2 сброса соединены соответственно с выходами раз- урядов 1.1-1.N, тактовый вход блока 2 сброса соединен с тактовыми входами

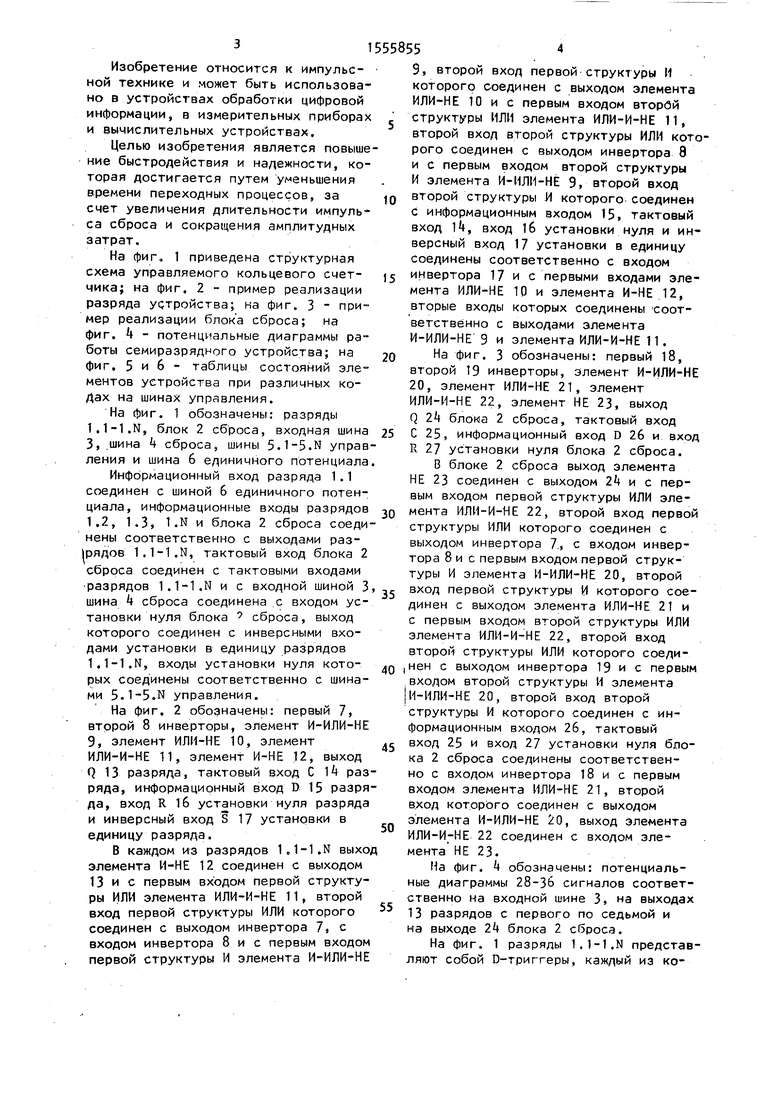

9, второй вход первой структуры И которого соединен с выходом элемента ИЛИ-НЕ 10 и с первым входом вторбй структуры ИЛИ элемента ИЛИ-И-НЕ 11, второй вход второй структуры ИЛИ которого соединен с выходом инвертора 8 и с первым входом второй структуры И элемента И-ИЛИ-НЕ 9, второй вход второй структуры И которого соединен с информационным входом 15, тактовый вход И, вход 16 установки нуля и инверсный вход 17 установки в единицу соединены соответственно с входом инвертора 17 и с первыми входами элемента ИЛИ-НЕ 10 и элемента И-НЕ 12, вторые входы которых соединены -соответственно с выходами элемента И-ИЛИ-НЕ 9 и элемента ИЛИ-И-НЕ 11.

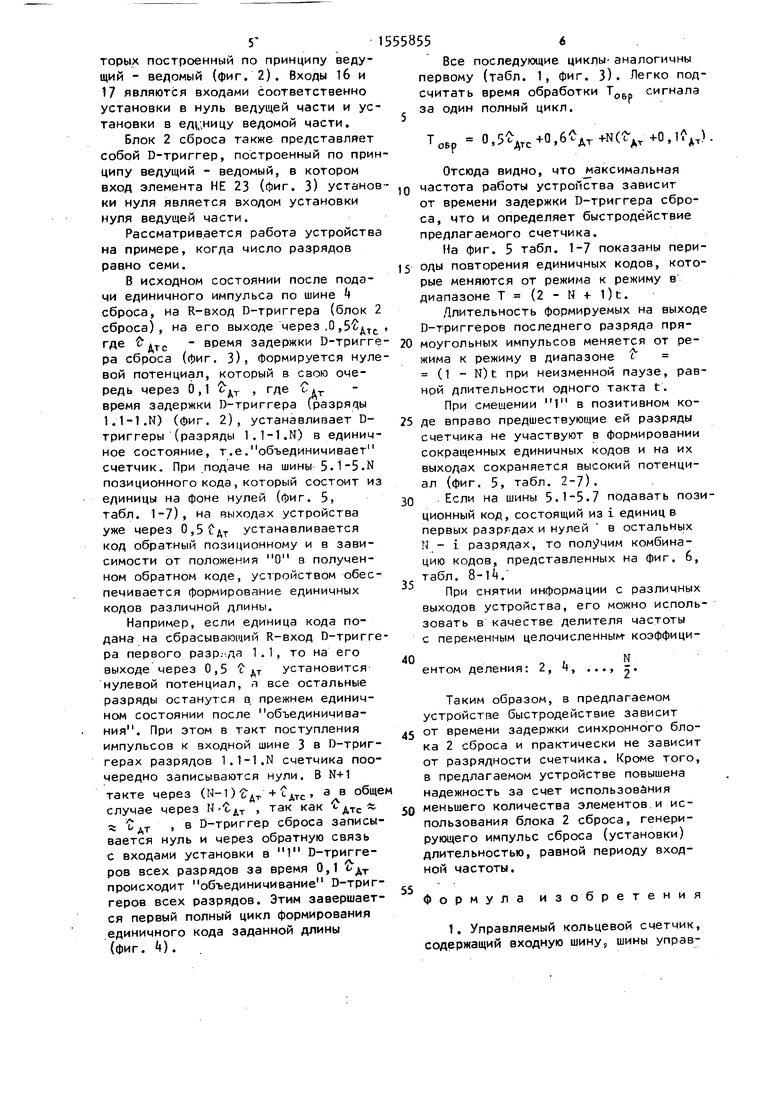

На фиг. 3 обозначены: первый 18, второй 19 инверторы, элемент И-ИЛИ-НЕ 20, элемент ИЛИ-НЕ 21, элемент ИЛИ-И-НЕ 22, элемент НЕ 23, выход Q 2k блока 2 сброса, тактовый вход С 25, информационный вход D 26 и вход R 27 установки нуля блока 2 сброса.

В блоке 2 сброса выход элемента НЕ 23 соединен с выходом 2k и с первым входом первой структуры ИЛИ элемента ИЛИ-И-НЕ 22, второй вход первой структуры ИЛИ которого соединен с выходом инвертора 7, с входом инвертора 8 и с первым входом первой структуры И элемента И-ИЛИ-НЕ 20, второй

разрядов 1.1-1.N и с входной шиной 3, вход первой структуры И которого соешина 4 сброса соединена с входом установки нуля блока сброса, выход которого соединен с инверсными входами установки в единицу разрядов 1.1-1.N, входы установки нуля которых соединены соответственно с шинами 5.1-5.N управления.

На фиг. 2 обозначены: первый 7, второй 8 инверторы, элемент И-ИЛИ-НЕ 9, элемент ИЛИ-НЕ 10, элемент ИЛИ-И-НЕ 11, элемент И-НЕ 12, выход Q 13 разряда, тактовый вход С 14 разряда, информационный вход D 15 разряда, вход R 16 установки нуля разряда и инверсный вход S 17 установки в единицу разряда.

В каждом из разрядов 1.1-1.N выход элемента И-НЕ 12 соединен с выходом 13 и с первым входом первой структуры ИЛИ элемента ИЛИ-И-НЕ 11, второй вход первой структуры ИЛИ которого соединен с выходом инвертора 7, с входом инвертора 8 и с первым входом первой структуры И элемента И-ИЛИ-НЕ

45

динен с выходом элемента ИЛИ-НЕ 21 и с первым входом второй структуры ИЛИ элемента ИЛИ-И-НЕ 22, второй вход второй структуры ИЛИ которого соеди- 4Q ,нен с выходом инвертора 19 и с первым входом второй структуры И элемента И-ИЛИ-НЕ 20, второй вход второй структуры И которого соединен с информационным входом 26, тактовый вход 25 и вход 27 установки нуля блока 2 сброса соединены соответственно с входом инвертора 18 и с первым входом элемента ИЛИ-НЕ 21, второй вход которого соединен с выходом элемента И-ИЛИ-НЕ 20, выход элемента ИЛИ-И-НЕ 22 соединен с входом элемента НЕ 23.

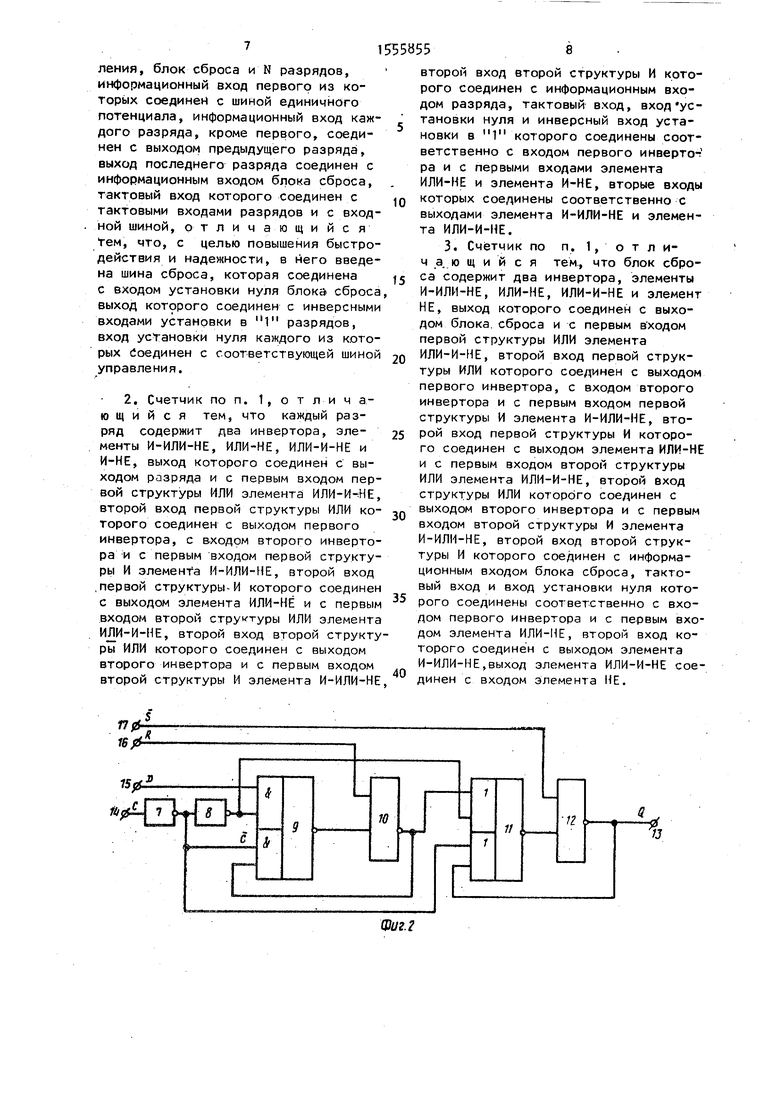

На фиг. k обозначены: потенциальные диаграммы 28-36 сигналов соответственно на входной шине 3, на выходах 13 разрядов с первого по седьмой и на выходе 2k блока 2 сброса.

На фиг. 1 разряды 1.1-1.N представляют собой D-триггеры, каждый из ко50

55

9, второй вход первой структуры И которого соединен с выходом элемента ИЛИ-НЕ 10 и с первым входом вторбй структуры ИЛИ элемента ИЛИ-И-НЕ 11, второй вход второй структуры ИЛИ которого соединен с выходом инвертора 8 и с первым входом второй структуры И элемента И-ИЛИ-НЕ 9, второй вход второй структуры И которого соединен с информационным входом 15, тактовый вход И, вход 16 установки нуля и инверсный вход 17 установки в единицу соединены соответственно с входом инвертора 17 и с первыми входами элемента ИЛИ-НЕ 10 и элемента И-НЕ 12, вторые входы которых соединены -соответственно с выходами элемента И-ИЛИ-НЕ 9 и элемента ИЛИ-И-НЕ 11.

На фиг. 3 обозначены: первый 18, второй 19 инверторы, элемент И-ИЛИ-НЕ 20, элемент ИЛИ-НЕ 21, элемент ИЛИ-И-НЕ 22, элемент НЕ 23, выход Q 2k блока 2 сброса, тактовый вход С 25, информационный вход D 26 и вход R 27 установки нуля блока 2 сброса.

В блоке 2 сброса выход элемента НЕ 23 соединен с выходом 2k и с первым входом первой структуры ИЛИ элемента ИЛИ-И-НЕ 22, второй вход первой структуры ИЛИ которого соединен с выходом инвертора 7, с входом инвертора 8 и с первым входом первой структуры И элемента И-ИЛИ-НЕ 20, второй

вход первой структуры И которого соевход первой структуры И которого сое

динен с выходом элемента ИЛИ-НЕ 21 и с первым входом второй структуры ИЛИ элемента ИЛИ-И-НЕ 22, второй вход второй структуры ИЛИ которого соеди- ,нен с выходом инвертора 19 и с первым входом второй структуры И элемента И-ИЛИ-НЕ 20, второй вход второй структуры И которого соединен с информационным входом 26, тактовый вход 25 и вход 27 установки нуля блока 2 сброса соединены соответственно с входом инвертора 18 и с первым входом элемента ИЛИ-НЕ 21, второй вход которого соединен с выходом элемента И-ИЛИ-НЕ 20, выход элемента ИЛИ-И-НЕ 22 соединен с входом элемента НЕ 23.

На фиг. k обозначены: потенциальные диаграммы 28-36 сигналов соответственно на входной шине 3, на выходах 13 разрядов с первого по седьмой и на выходе 2k блока 2 сброса.

На фиг. 1 разряды 1.1-1.N представляют собой D-триггеры, каждый из ко

s

5 1555855

торых построенный по принципу ведущий - ведомый (фиг. 2). Входы 16 и 17 являются входами соответственно установки в нуль ведущей части и установки в единицу ведомой части.

Блок 2 сброса также представляет собой D-триггер, построенный по принципу ведущий - ведомый, в котором вход элемента НЕ 23 (фиг. 3) установки нуля является входом установки нуля ведущей части.

Рассматривается работа устройства на примере, когда число разрядов равно семи.

В исходном состоянии после подачи единичного импульса по шине k сброса, на R-вход D-триггера (блок 2 сброса), на его выходе через ,0,5Јдтс ,

Все последующие циклы аналогичны первому (табл. 1, фиг. 3) . Легко подсчитать время обработки Т сигнала

за один полный цикл.

овр

Т06р O.SV AT+NCV V

10

гДе дтс

Отсюда видно, что максимальная частота работы устройства зависит от времени задержки D-триггера сброса, что и определяет быстродействие предлагаемого счетчика.

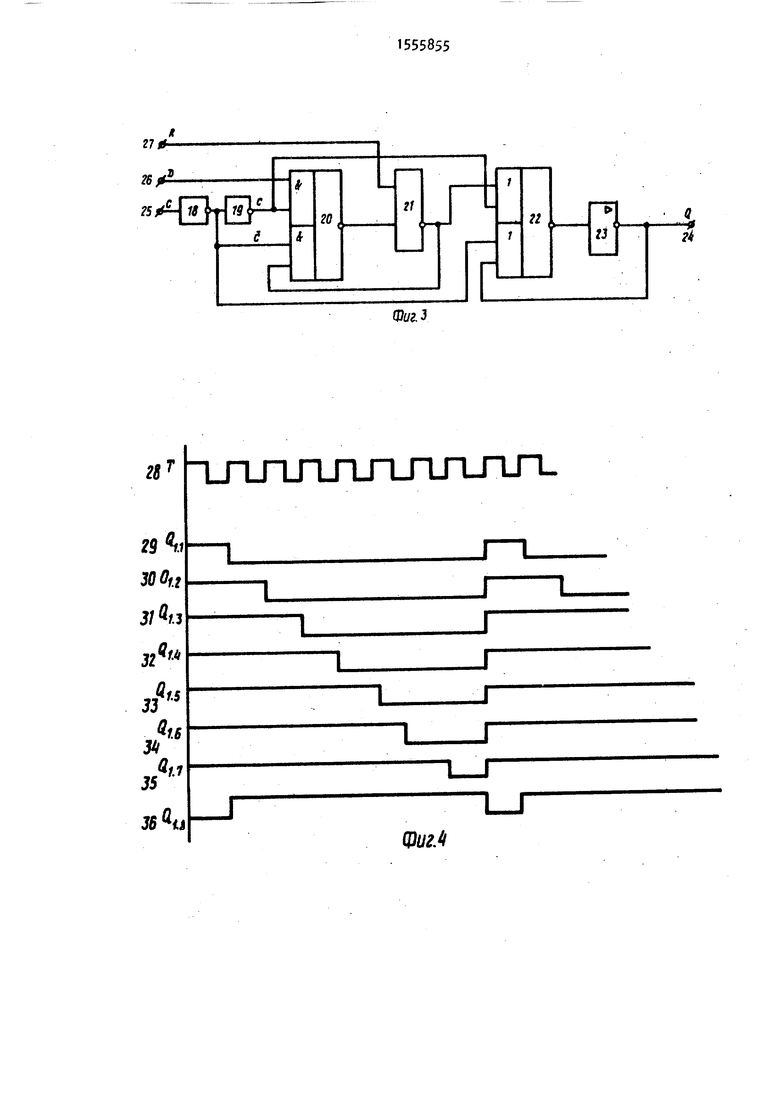

На фиг. 5 табл. 1-7 показаны пери- 15 оды повторения единичных кодов, которые меняются от режима к режиму в диапазоне Т (2 - N + l)t.

Длительность формируемых на выходе D-триггеров последнего разряда пря- - время задержки D-тригге- 20 моугольных импульсов меняется от ревой потенциал, который в саою очередь через 0,1 Јдт , где С

ра сброса (фиг. 3), формируется нулевок

AT время задержки D-триггера (разряцы

1.1-1.N) (фиг. 2), устанавливает D- триггеры (разряды 1.1-1.N) в единичное состояние, т.е.объединичивает счетчик. При подаче на шины 5.1-5.N позиционного кода, который состоит из единицы на фоне нулей (фиг. 5, табл. 1-7), на выходах устройства уже через 0,5Сдт устанавливается код обратный позиционному и в зависимости от положения О в полученном обратном коде, устройством обеспечивается формирование единичных кодов различной длины.

Например, если единица кода подана на сбрасывающий R-вход D-триггера первого разр.-да 1.1, то на его выходе через 0,5 Ј дт установится нулевой потенциал, л все остальные разряды останутся в прежнем единичном состоянии после объединичива- ния. При этом в такт поступления импульсов к входной шине 3 в D-триг- герах разрядов 1.1-1.N счетчика поочередно записываются нули. В N+1 такте через (М-1)ЈДт + сДтс , а в общем случае через N ЈAT , так как ЈАТС « Јдт в D-триггер сброса записывается нуль и через обратную связь с входами установки в 1 D-триггеров всех разрядов за время 0,1 Ьдт происходит объединичивание D-триггеров всех разрядов. Этим завершается первый полный цикл формирования единичного кода заданной длины (фиг. ).

f

жима к режиму в диапазоне (1 - N)t при неизменной паузе, равной длительности одного такта t.

При смешении 1 в позитивном ко- 25 де вправо предшествующие ей разряды счетчика не участвуют в формировании сокращенных единичных кодов и на их выходах сохраняется высокий потенциал (фиг. 5, табл. 2-7).

Если на шины 5.1-5.7 подавать позиционный код, состоящий из i единиц в первых разрядах и нулей в остальных N - i разрядах, то получим комбинацию кодов, представленных на фиг. 6, табл. 8-Й.

При снятии информации с различных выходов устройства, его можно использовать в качестве делителя частоты с переменным целочисленным- коэффици30

35

40

ентом деления: 2, 4,

N Г

Таким образом, в предлагаемом устройстве быстродействие зависит

45 от времени задержки синхронного блока 2 сброса и практически не зависит от разрядности счетчика. Кроме того, в предлагаемом устройстве повышена надежность за счет использования

50 меньшего количества элементов и использования блока 2 сброса, генерирующего импульс сброса (установки) длительностью, равной периоду входной частоты.

55

Формула изобретения

1. Управляемый кольцевой счетчик, содержащий входную шину, шины управ

Все последующие циклы аналогичны первому (табл. 1, фиг. 3) . Легко подсчитать время обработки Т сигнала

за один полный цикл.

овр

Т06р O.SV AT+NCV V

10

Длительность формируемых на выходе D-триггеров последнего разряда пря- 0 моугольных импульсов меняется от реf

жима к режиму в диапазоне (1 - N)t при неизменной паузе, равной длительности одного такта t.

При смешении 1 в позитивном ко- 5 де вправо предшествующие ей разряды счетчика не участвуют в формировании сокращенных единичных кодов и на их выходах сохраняется высокий потенциал (фиг. 5, табл. 2-7).

Если на шины 5.1-5.7 подавать позиционный код, состоящий из i единиц в первых разрядах и нулей в остальных N - i разрядах, то получим комбинацию кодов, представленных на фиг. 6, табл. 8-Й.

При снятии информации с различных выходов устройства, его можно использовать в качестве делителя частоты с переменным целочисленным- коэффици0

5

40

ентом деления: 2, 4,

N Г

Таким образом, в предлагаемом устройстве быстродействие зависит

от времени задержки синхронного блока 2 сброса и практически не зависит от разрядности счетчика. Кроме того, в предлагаемом устройстве повышена надежность за счет использования

меньшего количества элементов и использования блока 2 сброса, генерирующего импульс сброса (установки) длительностью, равной периоду входной частоты.

55

Формула изобретения

1. Управляемый кольцевой счетчик, содержащий входную шину, шины управ7

ления, блок сброса и N разрядов, информационный вход первого из которых соединен с шиной единичного потенциала, информационный вход каждого разряда, кроме первого, соединен с выходом предыдущего разряда, выход последнего разряда соединен с информационным входом блока сброса, тактовый вход которого соединен с тактовыми входами разрядов и с входной шиной, отличающийся Тем, что, с целью повышения быстродействия и надежности, в него введена шина сброса, которая соединена с входом установки нуля блока сброс выход которого соединен с инверсным входами установки в 1 разрядов, вход установки нуля каждого из которых Соединен с соответствующей шино управления.

о т л и ч а- каждый раз

2. Счетчик по п. 1, ю щ и и с я тем, что ряд содержит два инвертора, эле- менты И-ИЛИ-НЕ, ИЛИ-НЕ, ИЛИ-И-НЕ и И-НЕ, выход которого соединен с выходом разряда и с первым входом первой структуры ИЛИ элемента ИЛИ-И-НЕ, второй вход первой структуры ИЛИ которого соединен с выходом первого инвертора, с входом второго инвертора и с первым входом первой структуры И элемента И-ИЛИ-НЕ, второй вход первой структуры-И которого соединен с выходом элемента ИЛИ-НЕ и с первым входом второй структуры ИЛИ элемента ИЛИ-И-НЕ, второй вход второй структуры ИЛИ которого соединен с выходом второго инвертора и с первым входом

второй структуры И элемента И-ИЛИ-НЕ,

0

5

0

0

5

5

8

второй вход второй структуры И которого соединен с информационным входом разряда, тактовый вход, вход установки нуля и инверсный вход установки в 1 которого соединены соответственно с входом первого инверто-1 ра и с первыми входами элемента ИЛИ-НЕ и элемента И-НЕ, вторые входы которых соединены соответственно с выходами элемента И-ИЛИ-НЕ и элемента ИЛИ-И-НЕ.

3. Счетчик по

0

п. 1, отличающийся тем, что блок сброса содержит два инвертора, элементы ИИЛИ-НЕ, ИЛИ-НЕ, ИЛИ-И-НЕ и элемент НЕ, выход которого соединен с выходом блока сброса и с первым входом первой структуры ИЛИ элемента ИЛИ-И-НЕ, второй вход первой структуры ИЛИ которого соединен с выходом первого инвертора, с входом второго инвертора и с первым входом первой структуры И элемента И-ИЛИ-НЕ, второй вход первой структуры И которого соединен с выходом элемента ИЛИ-НЕ и с первым входом второй структуры ИЛИ элемента ИЛИ-И-НЕ, второй вход структуры ИЛИ которого соединен с выходом второго инвертора и с первым входом второй структуры И элемента ИИЛИ-НЕ, второй вход второй структуры И которого соединен с информационным входом блока сброса, тактовый вход и вход установки нуля которого соединены соответственно с входом первого инвертора и с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом элемента ИИЛИ-НЕ,выход элемента ИЛИ-И-НЕ соединен с входом элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронный модуль | 1987 |

|

SU1444940A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2012 |

|

RU2480823C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИМВОЛЬНОМ КОДЕ | 1991 |

|

RU2021644C1 |

| УСТРОЙСТВО ДЛЯ УПЛОТНЕНИЯ ОПТИМАЛЬНОЙ ФОРМЫ T-КОДА | 1991 |

|

RU2025047C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1354416A1 |

| Устройство обмена данными распределенной управляющей системы | 1990 |

|

SU1718226A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Устройство для считывания и обработки изображений | 1988 |

|

SU1513486A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки цифровой информации, в измерительных приборах и вычислительных устройствах. Цель изобретения - повышение быстродействия и надежности, которая достигается путем введения новых связей и шины 4 сброса. Счетчик также содержит разряды 1.1 - 1.N, блок 2 сброса, входную шину 3, шины 5.1 - 5.N управления и шину 6 единичного потенциала. В управляемом кольцевом счетчике быстродействие повышено за счет уменьшения времени переходных процессов, а надежность повышена за счет уменьшения количества используемых элементов и за счет увеличения длительности импульса с выхода блока 2 сброса. 2 з.п. ф-лы, 6 ил.

17 Г6

15

W0L,

MI

ii

п

-9L

13

го

ят njnjnjnjTJTJTJTJTJ L

я h j/e/j

X

5

46

33

t

зл

/

м

п

гз

г

q i РФФФФФ ФФ1ФФФФФ

дом nntootififgDC/itf)

/////

00/ М

1О I П

/////

00t II

1О I I L

/////

Z

t ф ф

Ч f

|(ф фф ф I фф

ij .

Јav nntootwgodufi

ifvgoj.

flfffOJ,

ФФФ 1ффф

1

pz

S lfQOJ.

ФФФФФФФ1

2 1/QBJ.

rvm

5585551

TaO/i.8

11111111 ФФ1111 1 1 ФФФ11 11 1 ФФФФ 1111 ФФФФФ 1 11 ФФФФФФ11 ФФФ фф фф 1 Ф ф ф ф ф фф ф

11111111 ФФ1 1 1 111 ФФФ 11111

ФФФФ1 7 / / ФФФФФ1 11 фффффф11 ФФФФФФФ1 фффффффф

11111111

таЗл.9

11111111 ФФФ11111 ФФФФ1 11 1 ФФФФФf11 ФФфффф11 ФФФФФ фф1 ФФФФФ ффф 11111111 ФФФ 11111 ФФФФ1111 Ф ФФФф ii 1 фФФФФФ11 ФФФФФФФ1 ФФФффффф

1 1111111

Гоблю

111111 ФФФФ 11 ффффф 1

фффФФФ ФФФФ ФФ

ффф ф ф ф

111 111 ФФФФ1 1

фффффfГ

ф фф ФФФ ФФФФФФФ

ффффф фф

1111111

1 1ффффФФ 1/77

Управляющий ход

ффффф у 7 71ФФФ

Таил 12

11111111 фффффф 1 f

фффффф ф 1 Ф ф ф Ффф фф

11111111 фффффф77 ффффффф1 фффффффф 11111111

1/77777 ФФ

TaOf.11

11111111 ФФФФФ 11 /

ФФФФ ФФ11 ФФФФФФФj Ф ф ф ф ф. Ф фф

11111111 ФФФФФ111 ФФФ ф Фф 11 ФФФФФФФ1 Фффффффф 11111111

4 ь

7 7 1 1ФФФ

тобл, и

11111111 ФФФФФФФФ

11111111 ФФФФФФФФ 11111111

1 1 1 1 1 11Ф Фиг.б

11111111

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU822377A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ( УПРАВЛЯЕМЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК | |||

Авторы

Даты

1990-04-07—Публикация

1988-04-20—Подача