Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах обработки двоичной информации.

Цель изобретения - упрощение пре- образователя.

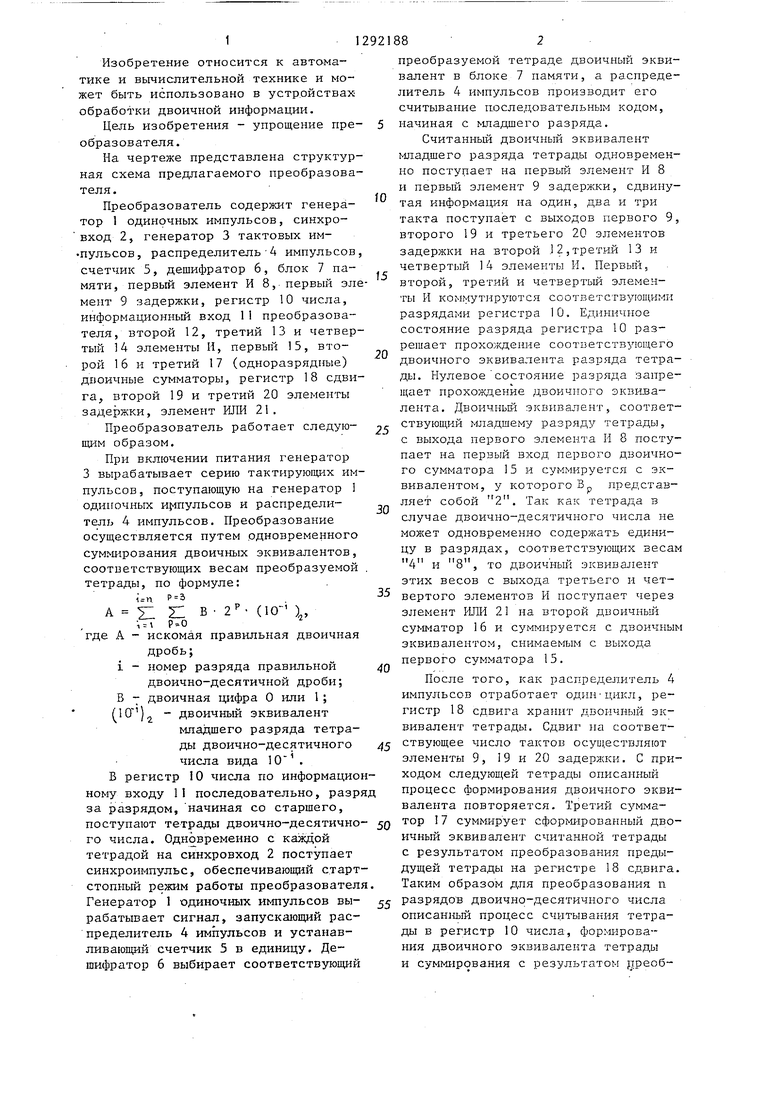

На чертеже представлена структурная схема предлагаемого преобразователя.

Преобразователь содержит генератор 1 одиночных импульсов, синхро- вход 2, генератор 3 тактовых им- пульсов, распределитель4 импульсов счетчик 5, дешифратор 6, блок 7 памяти, первый элемент И 8, первый элемент 9 задержки, регистр 10 числа, информационный вход 11 преобразователя, второй 12, третий 13 и четвертый 14 элементы И, первый 15, второй 16 и третий 17 (одноразрядные) двоичные сумматоры, регистр 18 сдвига, второй 19 и третий 20 элементы задержки, элемент ИЛИ 21.

Преобразователь работает следую- щим образом.

При включении питания генератор 3 вырабатывает серию тактирующих импульсов, поступающую на генератор 1 одиночных и{ пульсов и распредели- тель 4 импульсов. Преобразование осуществляется путем одновременного суммирования двоичных эквивалентов, соответствующих весам преобразуемой тетрады, по формуле:

n .

А Ц Ц В 2- (10- I

где А - искомая правильная двоичная

дробь; i - номер разряда правильной

двоично-десятичной дроби; В - двоичная цифра О или 1; (10) - двоичный эквивалент

младшего разряда тетрады двоично-десятичного числа вида ,

Б регистр 10 числа по информационому входу 11 последовательно, разр за разрядом, начиная со старшего, поступают тетрады двоично-десятично го числа. Одновременно с ка;ждой тетрадой на синхровход 2 поступает синхроимпульс, обеспечивающий старт стопный режим работы преобразовател Генератор 1 одиночных импульсов вы- рабатывает сигнал, запускающий распределитель 4 импульсов и устанавливающий счетчик 5 в единицу. Дешифратор 6 выбирает соответствующий

2

Ш

20

5

, 25

,., .

40

5

няд- 50 - я. 55

35

882

преобразуемой тетраде двоичный эквивалент в блоке 7 памяти, а распределитель 4 импульсов производит его считывапие последовательным кодом, начиная с младшего разряда.

Считанный двоичный эквивалент младшего разряда тетрады одновременно поступает на первый элемент И 8 и первый элемент 9 задержки, сдвинутая информация на один, два и три такта поступает с выходов первого 9, второго 19 и третьего 20 элементов задержки на второй 12,третий 13 и четвертый 14 элементы И, Первый, второй, третий и четвертый элементы И коммутируются соответствугощими разрядами регистра 10. Еднршчиое состояние разряда регистра 10 разрешает прохождение соответствующего двоичного эквивалента разряда тетрады. Нулевое состояние разряда запре- щг1ет прохождение двоичного эквивалента. Двоичный эквюзалент, соответствующий младшему разряду тетрады, с выхода первого элемента И 8 поступает на первый вход первого двоичного сумматора 15 и суммируется с эквивалентом, у которогоВр представляет собой 2. Так как тетрада в случае двоично-десятичного числа не может одновременно содерашть единицу в разрядах, соответствующих весам 4 и 8, то двоичный эквивалент этих весов с выхода третьего и четвертого элементов И поступает iepe3 элемент ИЛИ 21 на второй цвоичньт сумматор 16 и суммируется с двоичным эквивалентом, снимаемым с первого сумматора 15.

После того, как распределитель 4 импульсов отработает один-цикл, регистр 18 сдвига хранит двоичный эквивалент тетрады. Сдвиг на соответствующее число тактов осуществляют элементы 9, 19 и 20 задержки. С приходом следующей тетрады описанный процесс формирования двоичного эквивалента повторяется. Третий сумматор 17 cyм fflpyeт сформированный двоичный эквивалент считанной тетрады с результатом преобразования предыдущей тетрады на регистре 18 сдвига. Таким образом для преобразования п разрядов двоично-десятичного числа описаш1ый процесс считывания тетрады в регистр 10 числа, формирования двоичного эквивалента тетрады и суммирования с результатом дреобразоваиия двух текущих тетрад повторяется еще п-2 раза. С приходом п-й тетрады процесс преобразования заканчивается. Результат преобразования хранится на регистре 18 сдвига.

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный код, содержащий три элемента задержки, генератор одиночных импульсов, синхровход которого соединен с входом, синхронизации преобразователя, а выход - с входом счетчика и входом запуска .распределителя импульсов, тактовый вход которого подключен к выходу генератора тактовых импульсов, соединенному с входом пуска генератора одиночных импульсов, выход счетчика через дешифратор соединен с адресным входом блока памяти, вход считывания которого подключен к выходу распределителя импульсов, выход блока памяти соединен с первым входом первого элемента И, второй вход которого соединен с выходом младшего разряда тетрады регистра числа, выходы осталы1ых разрядов тетрады которого по весам соединены с перРедактор Н.Тупица Заказ 286/58

Техред: И.Попович Корректор О. Луговая

Тираж 902Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое иредпуиятие, г.Ужгород, ул.Проектная, 4

выми входами соответствующих элементов И, выход первого элемента И подключен к первому первого двоичного сумматора, выход которого

соединен с первЕЛм входом второго двоичного сумматора, выход которого соединен с первым входом третьего двоичного сумматора, второй вход - которого через регистр сдвига соединен с его выходом, отличающийся тем, что, с целью упрощения, он содержит элемент ИЛИ, причем выход блока памяти соединен с входом первого элемента задержки,

выход которого соединен с входом второго элемента задержки и вторым входом второго элемента И, выход ко- торого подключен к второму входу первого двоичного сумматора, выход

второго элемента задержки подключен к входу третьего элемента задержки и к второму входу третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого нодключен к выходу четвертого элемента И, второй вход которого соединен с выходом третьего элемента задержки, выход элемента ИЛИ подключен к второму входу второго двоичного сумматора.

Составитель Н.Шелобанова

Техред: И.Попович Корректор О. Луговая

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1975 |

|

SU634267A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичнодесятичного кода в двоичный | 1977 |

|

SU656052A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах обработки двоичной информации Цель изобретения упрощение преобразователя. Поставленная цель достигается тем, что в преобразователь, содержащий генератор 1 одиночных импульсов, три элемента 9, 19, 20 задержки, счетчик 5, распределитель 4 импульсов, генератор 3 тактовых импульсов, дешифратор 6, блок 7 памяти, элементы 8, 12-14 И, регистр 10 числа, двоичные сумматору 16,17, : регистр 18 сдвига, дополнительно .введен элемент ИЛИ 21 и изменены межэлементные связи. 1 ил.

| Универсальный преобразователь двоично-десятичных чисел в двоичные | 1973 |

|

SU473179A1 |

Авторы

Даты

1987-02-23—Публикация

1985-03-12—Подача