2. 1-2.К элементов И поступают на вычитатели 3.1-3.К и через них исходные остатки записываются в регистры 4.1-4.К; так как информация принимается в параллельном коде, то на одном из входов обязательно будет потенциал 1, который одновременно поступает через элемент ИЛИ 7 на вход установки в нуль триггера 6. При поступлении тактового импульса на вход разрешения записи триггера, триггер 6 переводится в нулевое состояние и потенциалом О с прямого выхода закрывает блоки 2.1-2,К элементов И. Сигналы с выходов регистров поступают на дешифратор 5, в котором преобразуются по алгоритму, описанному выше; так как число 19 не лежит в диапазоне 0-m-l, для нашего случая 0-11-1 10, то на всех выходах дешифратора 5 будут потенциалы О, Одновременно с этим сигналы с выходов регистров 4.i-4.К поступают на входы

155

57681

10

15

20

Формула изобрете ния

Преобразователь модулярного кода, содержащий группу вычитателей, константы, группу регистров и первый элемент ИЛИ, причем выходы вычитателей константы группы соединены с информационными входами соответствующих регистров группы, выходы которых соединены с информационными входами соответствующих вычитателей константы группы, вход начальной установки преобразователя соединен с входами установки в О регистров группы, входы разрешения записи которых соединены с тактовым входом преобразователя, выход окончания которого соединен с выходом первого элемента ИЛИ, от- личающиис я тем, что, с целью расширения области применения за счет обеспечения преобразования многоступенчатого модулярного кода в код предыдущей ступени, он содержит

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь позиционного кода в модулярный код | 1987 |

|

SU1460772A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЛА В КВАДРАТИЧЕСКИЕ ОСТАТКИ | 1992 |

|

RU2029436C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯТОРНОМ КОДЕ | 1991 |

|

RU2022472C1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

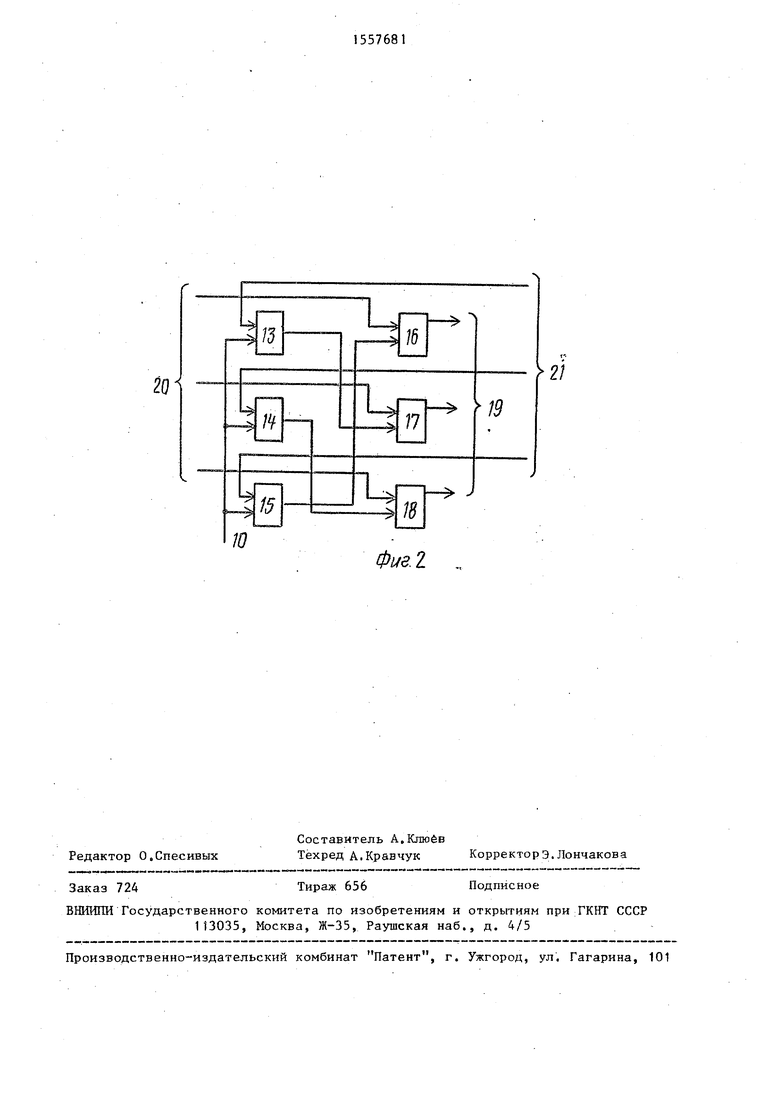

Изобретение относится к вычислительной технике и может быть использовано в системах и устройствах, функционирующих в модулярной арифметике. Цель изобретения - расширение области применения за счет обеспечения преобразования многоступенчатого модулярного кода в код предыдущей ступени. Существует периодическая зависимость остатков кодов меньшей ступени от остатков кодов большей ступени. Поэтому достаточно реализовать только одну повторяющуюся часть таблицы соответствия и путем вычитания определенных констант переходить от одной части к другой. Преобразователь содержит группу блоков элементов И 2, группу вычитателей 3 константы, группу регистров 4, дешифратор 5, триггер 6 и элементы ИЛИ 7 и 9 с соответствующими связями. 2 ил., 2 табл.

вычитателей 3. 1-3.К, в которых проис- 25 группу блоков элементов И, дешифраходит вычитание по модулю от кодов

констант:

Rf 11 mod ;

R2 11 mod

R3 11 mod

S7 (4-1) mod

S3 (5-4) mod .

Данные остатки соответствуют числу 8, действительно, 19 mod .

С соответствующих остаткам выходов регистров 4.1-4.К сигналы поступают на дешифратор 5, в котором функции , соответствует потенциал 111 на выходе дешифратора, соответствующем остатку, равному 8. Сигнал поступает на выход 12, Одновременно данные сигналы поступают на вход элемента ИЛИ 9, на выходе которого будет потенциал 1, так как на одном из его входов был потенциал 1. Данный потенциал поступает на вход 8. На этом преобразование заканчивается и преобразователь готов к обработке следующих остатков.

тор, триггер и второй элемент ИЛИ, причем группа информационных входов преобразователя соединена с первыми входами соответствующих блоков эле30 ментов И группы, вторые входы которы соединены с выходом триггера, входы установки в 1 и в О которого сое динены соответственно с входом начап ной установки преобразователя и с вы ходом второго элемента ИЛИ, входы ко торого соединены соответственно с вы ходами разрядов старшего блока элементов И группы, выходы блоков элеме тов И группы соединены с установочны ми входами соответствующих вычитателей константы группы, входы разрешения которых соединены с входом разре шения записи триггера и с тактовым входом преобразователя, выходы регис ров группы соединены соответственно с входами дешифратора, выходы которо го соединены с соответствующие вход ми первого эпемента ИЛИ и являются информационным выводом пр°образовате

50 ля.

35

40

45

тор, триггер и второй элемент ИЛИ, причем группа информационных входов преобразователя соединена с первыми входами соответствующих блоков элементов И группы, вторые входы которых соединены с выходом триггера, входы установки в 1 и в О которого соединены соответственно с входом начапь-1 ной установки преобразователя и с выходом второго элемента ИЛИ, входы которого соединены соответственно с выходами разрядов старшего блока элементов И группы, выходы блоков элементов И группы соединены с установочны ми входами соответствующих вычитателей константы группы, входы разрешения которых соединены с входом разрешения записи триггера и с тактовым входом преобразователя, выходы регистров группы соединены соответственно с входами дешифратора, выходы которого соединены с соответствующие входами первого эпемента ИЛИ и являются информационным выводом пр°образователя.

/0

Фиг. I „

Авторы

Даты

1990-04-15—Публикация

1988-06-27—Подача