I

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1990 |

|

SU1793548A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Преобразователь чисел из модулярного кода в позиционный код | 1987 |

|

SU1481898A1 |

| Устройство для обнаружения и исправления ошибок в интервально-модулярном коде | 1988 |

|

SU1541784A1 |

| Преобразователь числа в модулярный код | 1987 |

|

SU1444961A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для декодирования модулярного кода | 1987 |

|

SU1411980A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

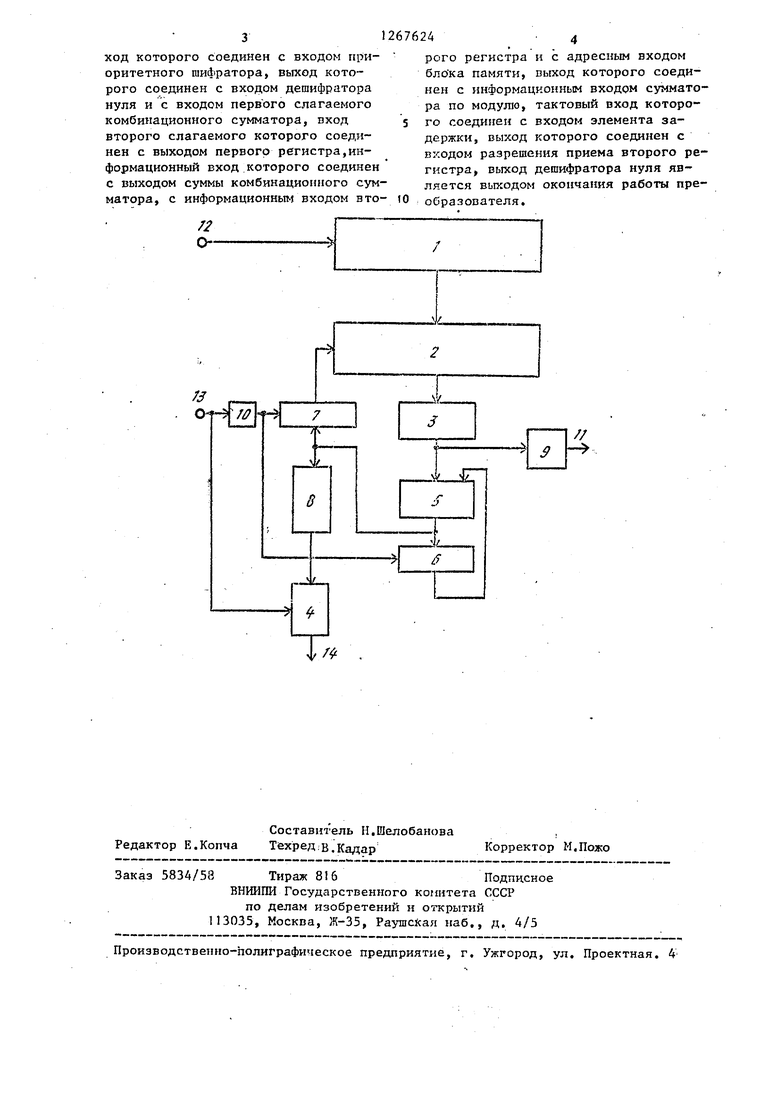

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в преобразователь, содержащий входной регистр, сумматор по модулю, два регистра и элемент задержки, введены мультиплексор, блок памяти, приоритетный шифратор, дешифратор нуля и комбинационный сумматор с соответствующими связями I ил.

О)

О)

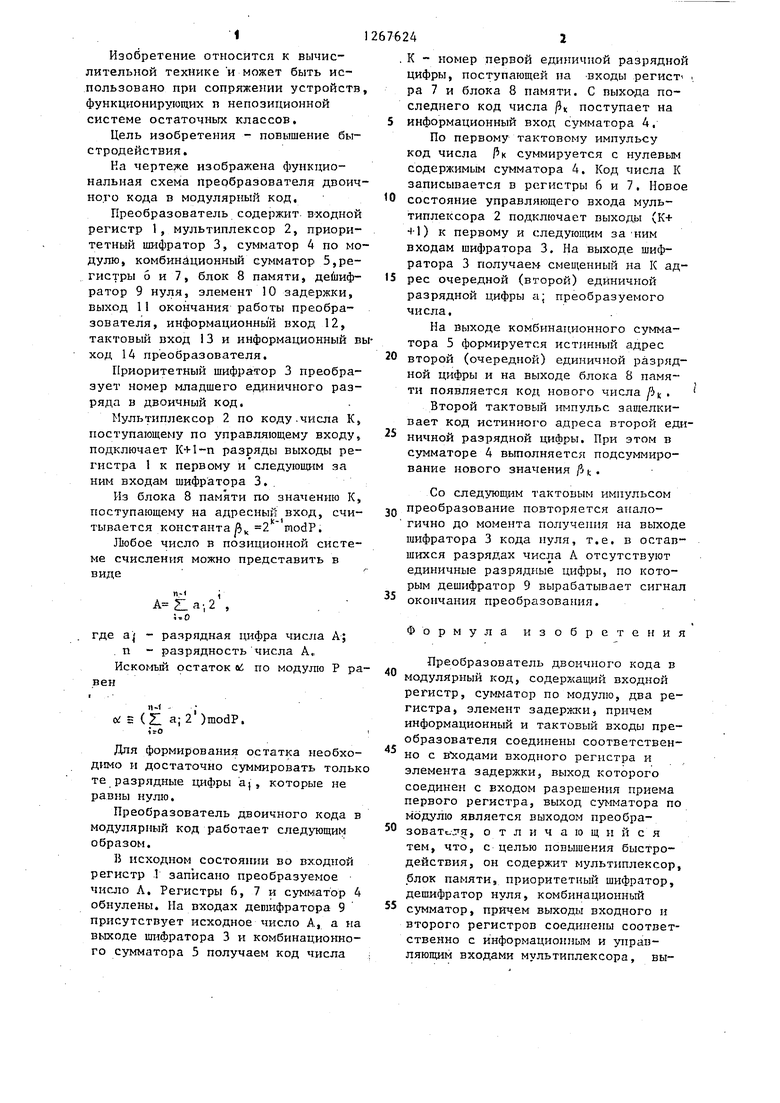

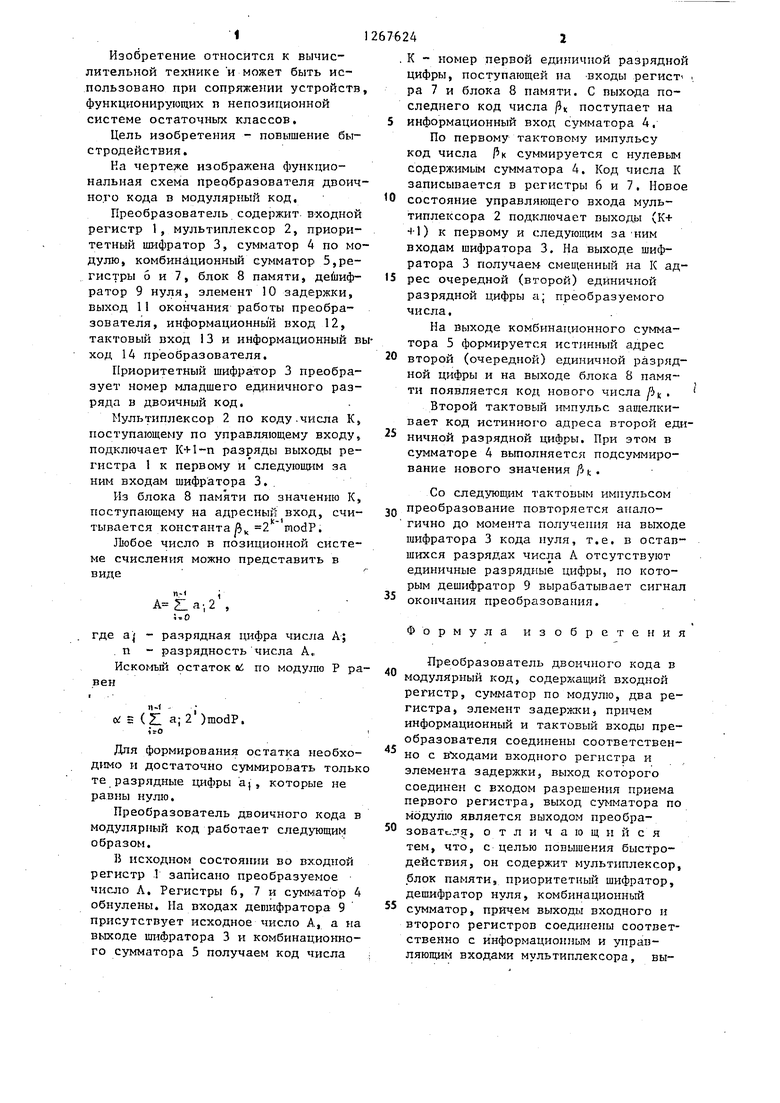

to Изобретение относится к вычислительной технике и может быть использовано при сопряжении устройств функционирующих п непозиционной системе остаточных классов. Цель изобретения - повышение быстродействия. Ка чертеже изображена функциональная схема преобразователя двоич ного кода в модулярный код, Преобразователь содержит в-ходной регистр 1, мультиплексор 2, приоритетный шифратор 3, сумматор 4 по мо дулю, комбинационный сумматор 5,регистры б и 7, блок 8 памяти, дейзифратор 9 нуля, элемент 10 задержки, выход 11 окончания работы преобразователя, информационный вход 12, тактовый вход 13 и информационный в ход 14 преобразователя. Приоритетный шифратор 3 преобразует номер младшего единичного разряда в двоичный код. Мультиплексор 2 по коду.числа К поступающему по управляющему входу подключает К+1-п разряды выходы регистра 1 к первому и следующим за ним входам шифратора 3.. Из блока 8 памяти по значению К поступающему на адресный вход, считывается константа А 2 modP. ХЬобое число в позиционной систепредставить в ме счисления можно виде - ; ,2 , , где а| - разрядная цифра числа А; п - разрядность числа А„ Искомый остаток uf, по модулю Р р 11-f (Z: а; 2 )modP. Для формирования остатка необхо дино и достаточно суммировать толь те разрядные цифры З), которые не равны нулю. Преобразователь двоичного кода модулярный код работает след тощим образом. В исходном состоянии во входной регистр 1 записано преобразуемое число А. Регистры 6, 7 и сумматор обнулены. На входах дешифратора 9 присутств ет исходное число А, а н выходе шифратора 3 и комбинационно го сумматора 5 получаем код числа 42 К - номер первой единичной разрядной цифры, поступающей на -входы регист .. ра 7 и блока 8 памяти. С пыхода последнего код числа /it поступает на информационный вход сумматора 4, По первому тактовому импульсу код числа к суммируется с нулевым содержимым сумматора 4. Код числа К записывается в регистры 6 и 7. Новое состояние управляющего входа мультиплексора 2 подключает выходы (К+ + 1) к первому и следующим заним входам шифратора 3, На выходе шифратора 3 получаем смещенный на К адрес очередной (второй) единичной разрядной цифры а; преобразуемого числа. На Выходе комбинационного сумматора 5 формируется истинный адрес второй (очередной) единичной разрядной цифры и на выходе блока 8 памяти появляется код нового числа |4к , Второй тактовый импульс защелкивает код истинного адреса второй единичной разрядной цифры. При этом в сумматоре 4 выполняется подсуммирование нового значения /It. Со следующим тактовым импульсом преобразование повторяется аналогично до момента получения на выходе шифратора 3 кода нуля, т.е. в оставшихся разрядах числа А отсутствуют единичные разрядные цифры, по которым дешифратор 9 вырабатывает сигнал окончания преобразования. Формула изобретения Преобразователь двоичного кода в модулярный код, содержащий входной регистр, сумматор по модулю, два регистра, элемент задержки, причем информационный и тактовый входы преобразователя соединены соответственно с вводами входного регистра и элемента задержки, выход которого соединен с входом разрешения приема первого регистра, выход сумматора по модулю является выходом преобразоват -ля, отличающийся тем, что, с целью повышения быстродействия, он содержит мультиплексор, блок памяти, приоритетный шифратор, дешифратор нуля, комбинационньп1 сумматор, причем выходы входного и второго регистров соединены соответственно с информационным и управляющим входами мультиплексора, выход которого соединен с входом приоритетного шифратора, выход которого соединен с входом дешифратора нуля и с входом первого слагаемого комбинационного сумматора, вход второго слагаемого которого соединен с выходом первого регистра,информационный вход которого соединен с выходом суммы комбинационного сумматора, с информационным входом второго регистра и с адресным входом блока памяти, выход которого соединен с информационным входом сумматора по модулю, тактовый вход которого соединен с входом элемента задержки, выход которого соединен с входом разрешения приема второго регистра, выход дешифратора нуля является выходом окончания работы преобразователя.

| Компенсатор переменного тока | 1959 |

|

SU125621A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-04-29—Подача