СП

СП

М

С&

00

ьэ

Изобретение относится к области вычислительной техники и может быть использовано для высокопроизводительного преобразования кода и частичног выполнения арифметических операций в цифровых вычислениях, использующих систему остаточных классов (СОК), в других цифровых устройствах.

Целью изобретения является расширение функциональных возможностей за счет преобразования и одновременного суммирования произвольного набора чисел, представленных в позиционном коде.

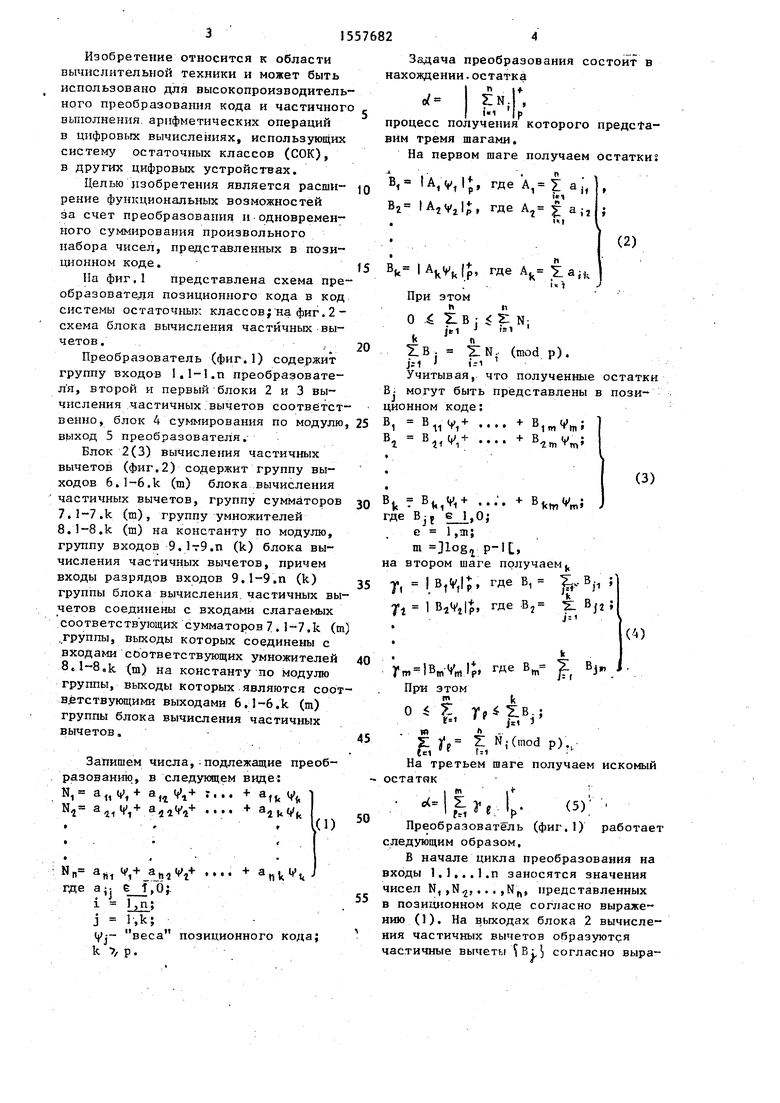

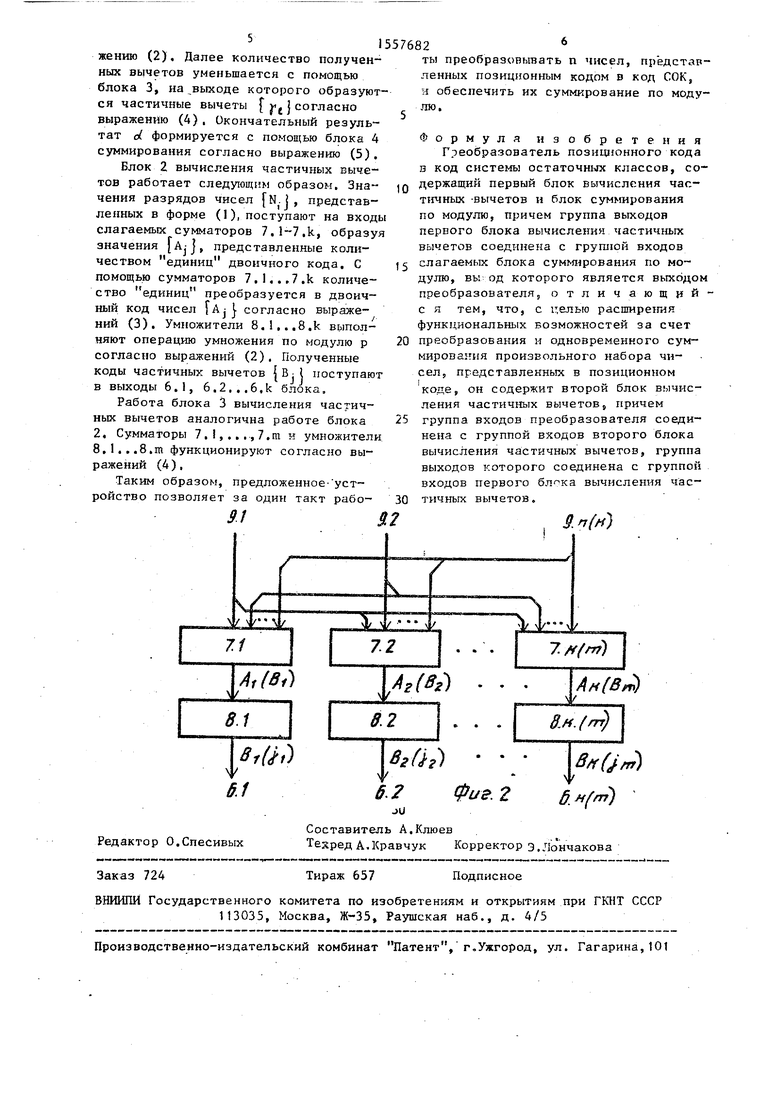

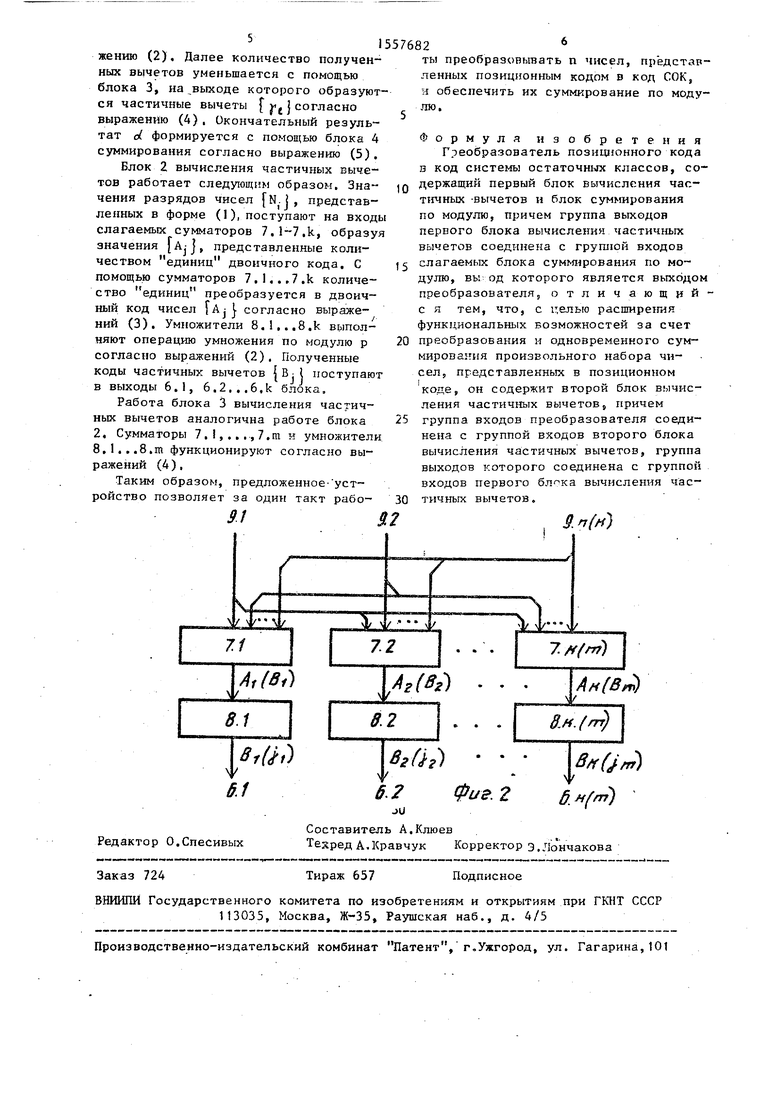

На фиг.1 представлена схема преобразователя позиционного кода в код системы остаточных классов; на фиг.2 - схема блока вычисления частичных вычетов.

Преобразователь (фиг.1) содержит группу входов 1,1-1.п преобразователя, второй и первый блоки 2 и 3 вычисления частичных вычетов соответственно, блок 4 суммирования по модулю выход 5 преобразователя.

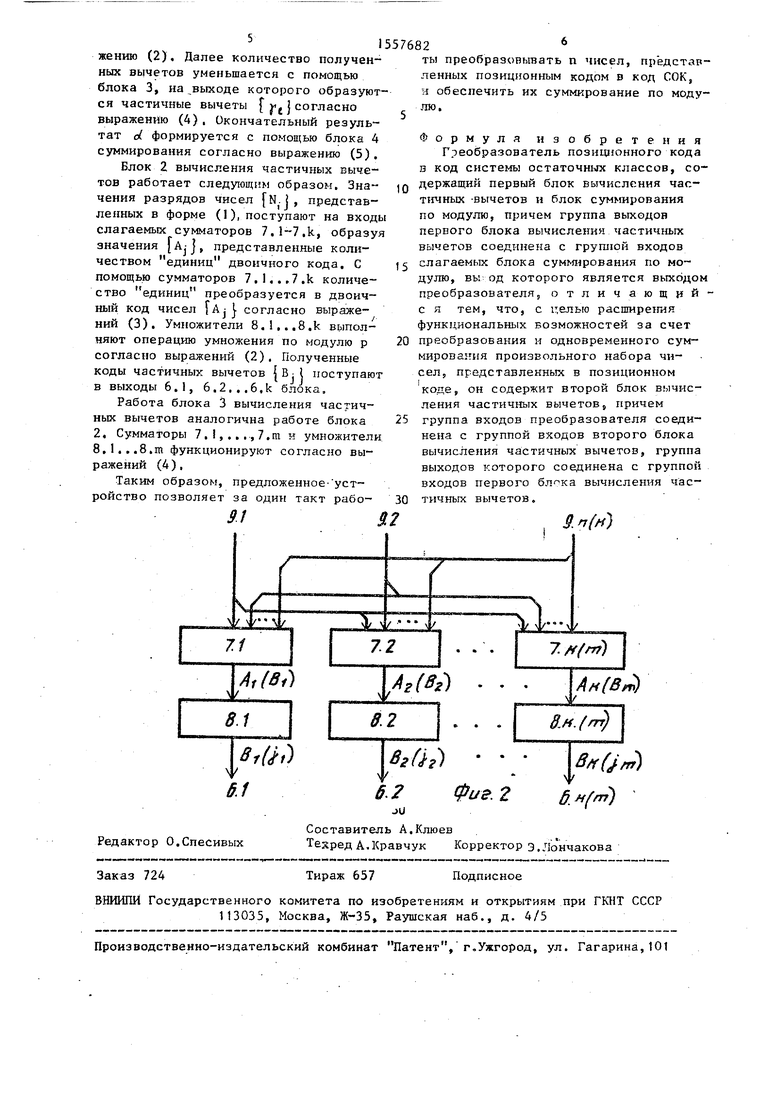

Блок 2(3) вычисления частичных вычетов (фиг,2) содержит группу выходов 6.1-6.k (m) блока вычисления частичных вычетов, группу сумматоров 7.1-7.k (m), группу умножителей 8.1-8.k (m) на константу по модулю, группу входов 9.1т9.п (k) блока вычисления частичных вычетов, причем входы разрядов входов 9.1-9.П (k)

группы блока вычисления частичных вычетов соединены с входами слагаемых

соответствующих сумматоров 7. 1-7.k (m

.группы, выходы которых соединены с

входами соответствующих умножителей

8«l-8.k (m) на константу по модулю

группы, выходы которых являются соответствующими выходами 6.1-6.k (m)

группы блока вычисления частичных

вычетов„

Запишем числа,-подлежащие преобразованию, в следующем виде:

Задача преобразования состоит в

нахождении.остатка n if

Јм«

i«i Мр

процесс получения которого вим тремя шагами.

На первом шаге получаем

10

Bi tAiVf Itf где А I а|

I M

В

г- 1А7ц/г1Ј, где А Ј а;,

ч

(2)

В, ц V,+

Bk |Акуц|+, где Ak Ја

«7

При этом

О Ј I1B ; Г N;

J M

1

ь

ZB. - ZN. (mod р). I 1-1

J-1

Учитывая, что полученные остатки

В- могут быть представлены в позиционном коде:

ц V,+

+ B,mV

Blf(V

+ В

1 т т 1п УЩ

(3)

Bk в

1nVi +

+ Bfci-V,

где BJJ e 1,0; e l,m; m Jloga p-lL, на втором шаге получаем,, )«, lBtVti;, где В, ,, ;

fc r

Гг

1 B4Yt|Ji где В2 JL Bft 5

Js1

СО

40

к

ГтЧВЛ ;, где Вт J( Bjt,

При этом т

°«5. тг«,«

Ј ),- Г В ((mod р).,

На третьем шаге получаем искомый остатяк

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь непозиционного кода в позиционный код | 1984 |

|

SU1481895A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1986 |

|

SU1388996A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД | 2013 |

|

RU2513915C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для расширения системы оснований модулярного кода | 1985 |

|

SU1282134A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД | 2008 |

|

RU2409840C2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств сопряжения специализированных ЦВМ, при реализации цифровых процессоров обработки сигналов. Цель изобретения - расширение функциональных возможностей за счет преобразования и одновременного суммирования произвольного набора чисел, представленных в позиционном коде. Преобразователь содержит первый и второй блоки 3 и 2 вычисления частичных вычетов, блок 4 суммирования по модулю с соответствующими связями. 2 ил.

ativ,+ awVa+ a24V,+

+ affc V

+ alkvfc

(1)

ani а

V,+ a,

J««

,j i -n

j i,k;

Vr

k , p

V,+

+ ankVu

веса позиционного кода;

0

«H Ј

1 M

(5)

работает

5

г V

Преобразователь (фиг.1) следующим образом,

В начале цикла преобразования на входы 1.1... l.n заносятся значения чисел N, ,NЈ,...,Nn, представленных в позиционном коде согласно выражению (1). На выходах блока 2 вычисления частичных вычетов образуются частичные вычеты В:$ согласно выра5

1

жению (2), Далее количество полученных вычетов уменьшается с помощью блока 3, на выходе которого образуются частичные вычеты pt j согласно выражению (4). Окончательный результат d формируется с помощью блока 4 суммирования согласно выражению (5).

Блок 2 вычисления частичных вычетов работает следующим образом. Зна- чения разрядов чисел N j, представленных в форме (1), поступают на входы слагаемых сумматоров 7..k, образуя значения AJ, представленные количеством единиц двоичного кода. С помощью сумматоров 7.1...7.k количество единиц преобразуется в двоичный код чисел AJ } согласно выражений (3). Умножители 8.1...8.k выполняют операцию умножения по модулю р согласно выражений (2). Полученные коды частичных вычетов В I поступают в выходы 6.1, 6.2,..6.k блока,

Работа блока 3 вычисления частичных вычетов аналогична работе блока 2, Сумматоры 7.,...,7.m и умножители 8, 1. . .8.П1 функционируют согласно выражений (4),

Таким образом, предложенное- устройство позволяет за один такт рабо-

91

J/r/W 6.1

Редактор О.Спесивых

В2( (j т ф

Составитель А.Клюев

Техред А.Кравчук Корректор Э.Ло нчакова

Заказ 724

Тираж 657

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

т.

Q

5

0

5

0

ты преобразовывать п чисел, представленных позиционным кодом в код СОК, л обеспечить их суммирование по модулю.

Формула изобретения Преобразователь позиционного кода в код системы остаточных классов, содержащий первый блок вычисления частичных -вычетов и блок суммирования по модулю, причем группа выходов первого блока вычисления частичных вычетов соединена с группой входов слагаемых блока суммирования по модулю, вы од которого является выходом преобразователя, отличающий- с я тем, что, с г,елью расширения функциональных возможностей за счет преобразования и одновременного суммирования произвольного набора чисел, представленных в позиционном коде, он содержит второй блок вычисления частичных вычетов, причем группа входов преобразователя соединена с группой входов второго блока вычисления частичных вычетов, группа выходов которого соединена с группой входов первого вычисления частичных вычетов.

Подписное

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1985 |

|

SU1267625A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в код по модулю | 1980 |

|

SU902013A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-15—Публикация

1988-06-27—Подача