(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1781692A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для обучения основам вычислительной техники | 1988 |

|

SU1564682A1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1714660A1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1775728A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ СРЕДСТВ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 2002 |

|

RU2237927C2 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Устройство для обучения операторов | 1990 |

|

SU1746393A1 |

| Устройство для тренировки операторов | 1990 |

|

SU1709377A1 |

Изобретение относится к учебно- лабораторному оборудованию и может быть использовано в учебном процессе, а также в конструкторских бюро для моделирования и отладки дискретных устройств, построенных на интегральных микросхемах Цель изобретения - расширение дидактических возможное- тей устройства, Устройство содержит пульт 1 оператора, блок 2 индикации, i

1чЭ

to to

П7

I ff J

коммутатор 3 входных снгнапов, наборное поле 4, модули 5 логических Элементов, модули 6 триггеров Каждый модуль 6 состоит из коммутатора 17, элемента 18 памяти, коммутатора 19, светодиода 20, подсоединенного к пря- выходу элемента 18, блока 21 прогнозирования (последующего состояния) , подсоединенного к соответству1

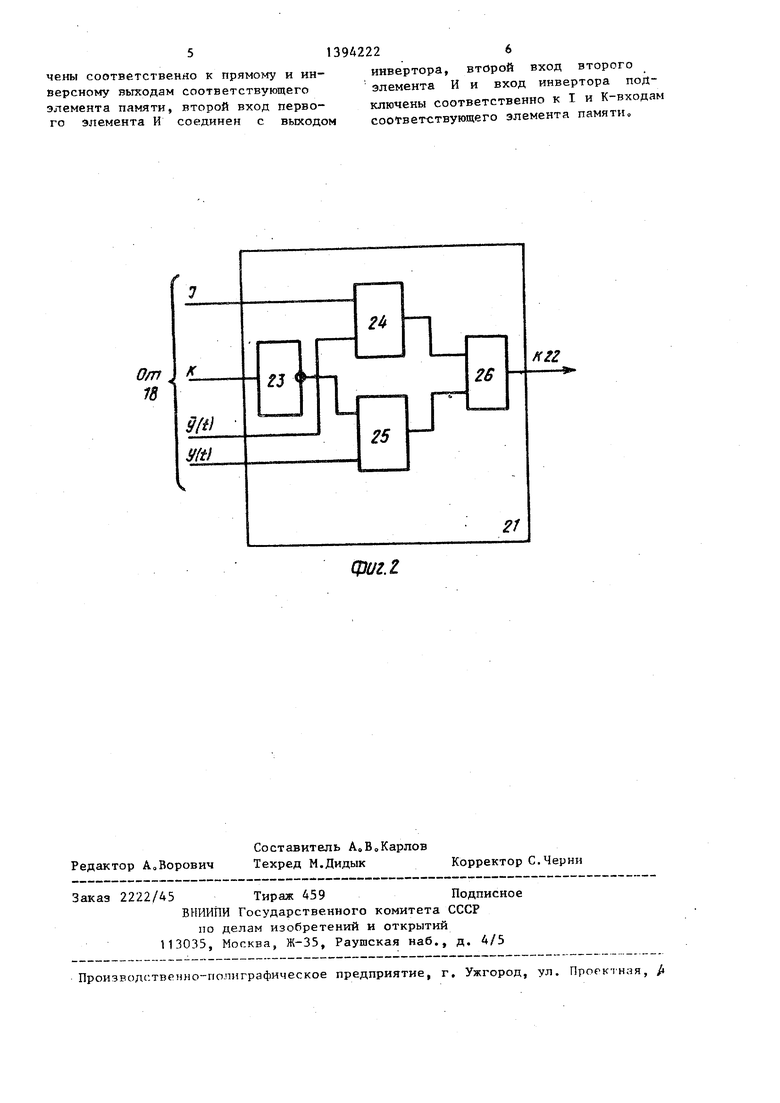

Изобретение относится к учебно- лабораторному оборудованию и может быть использовано в учебном процессе а также в конструкторских бюро для моделирования и отладки дискретных устройств, построенных на интегральных микросхемахо

Целью изобретения является расширение дидактических возможйостей уст ройства путем прогнозирования последующего состояния триггеров в моделируемых схемахо

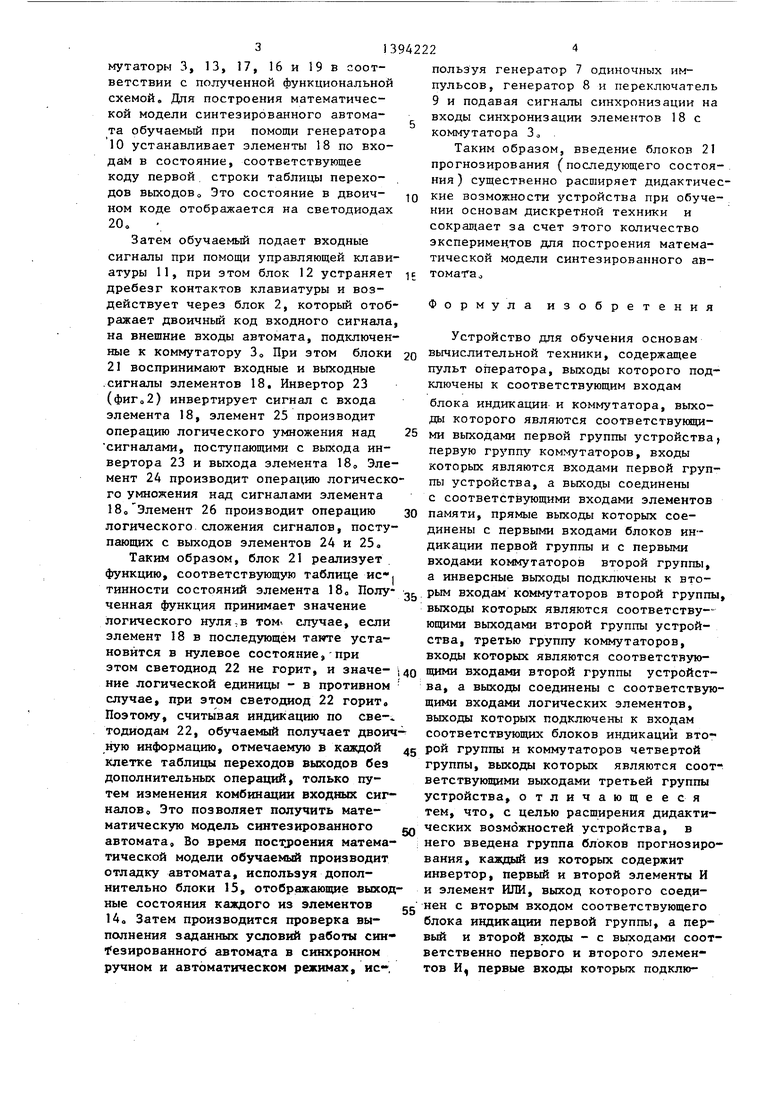

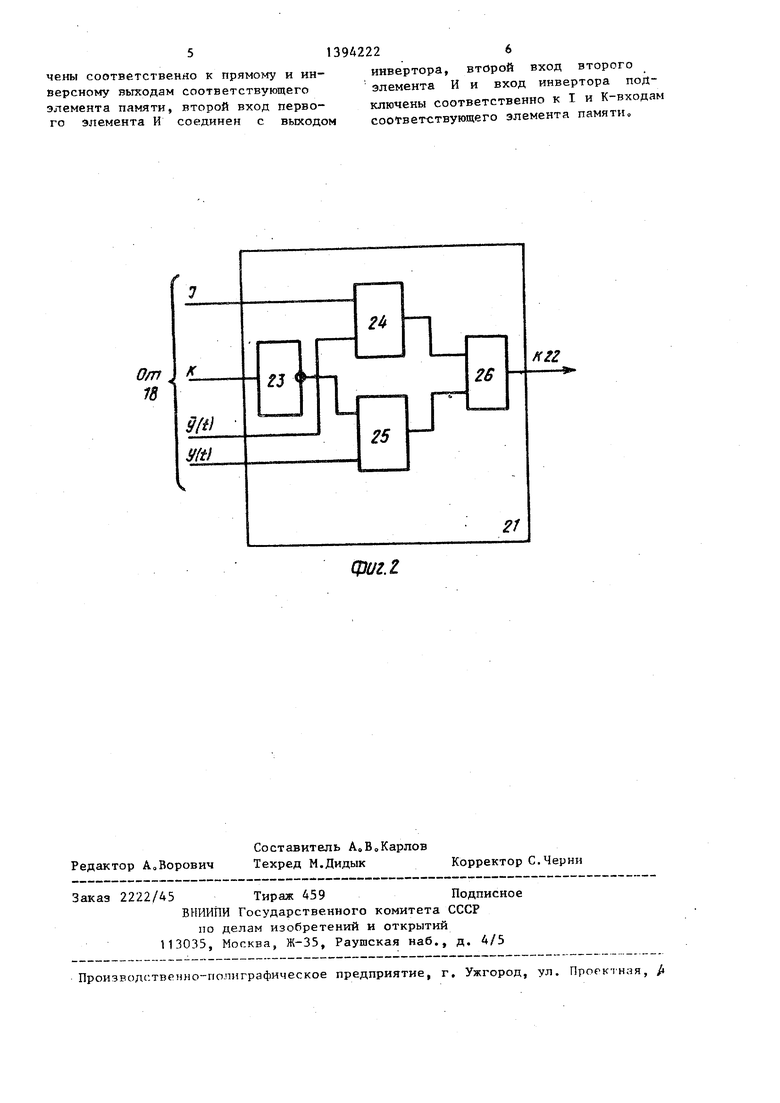

На фиГо представлена структура устройства; на фиГо2 -.функциональ- ная схем,а блока прогнозирования о

Устройство для обучения основам вычислительной техники содержит (фиГо) пульт 1 оператора, блок 2 индикации, коммутатор 3, наборное поле 4, модули 5 логических элементо и модули 6 триггеров Пульт 1 оператора содержит генератор 7 одиночных импульсов i генератор 8 непрерьшной последовательности, переключатель 9 рода работ, генератор 10 нуля, управ лякнцую клавиатуру 11 и блок 12 триггеров

Модуль 5 содержит коммутатор 13, логический элемент 14, блок 15 инди- кации, коммутатор 16о Модуль 6 содержит коммутатор 17, элемент 18 памяти, KOMMyTafop 19, светодиод 20, блок 21 прогнозирования, светоднод 22в Каждый блок 21 (фиг„2) содержит инвертор 23, элементы И 24 и 25, элемент ИЛИ 26,

Генератор 7 представляет собой кнопку без фиксации, подключенную входным контактом к шине -, а выющим входам и выходам элемента 18 и к входу светодиода 22„ Сущность изобретения основана на осуществлении прогнозирования последующего состояния триггера, что сокращает количество экспериментов для построения математической модели синтезированного автомата,, 2 ил

ходными контактами - к входам триггера 6

Генератор 8 представляет собой генератор прямоугольных импульсов амплитудой, равной напряжению логической I11«

Генератор 10 представляет собой ограничительный резистор, подсоединенный одним концом к шине -, а другим - к выходу пульта 1 оператора.

Управляющая клавиатура 11 представляет собой регистр кнопок с фиксацией, необходимых для задания входного сигнапа.

Блок 12 содержит триггеры по числу разрядов управляющей клавиатуры и предназначен для устранения дребезга контактов клавиатурыо

Модули 5 и 6 конструктивно выполнены в виде пластикового корпуса, снабженного кроме контактов входного и выходного полей клеммами подачи питания, с помощью которых и производится установка их на наборное поле, имеющее специальные гнезда. На верхней крышке модулей 5 и б изображено условно-графическое обозначение микросхемы,

Светодиоды 20 и 22 объединены в блок 27 индикации.

Соединения -осуществляются соединительными проводами (не показаны)

Устройство работает следующим образом.

Обучаемый, решив задачу логического синтеза функциональной схемы по заданным условиям работы, набирает ее на наборном поле 4 из модулей 5 и 6 с помощью соединительных проводов (не показаны), соединяющих коммутаторы 3, 13, 17, 16 и 19 в соответствии с полученной функциональной схемой. Для построения математической модели синтезированного автомата обучаемый при помощи генератора 10 устанавливает элементы 18 по входам в состояние, соответствующее коду первой строки таблицы переходов выходов о Это состояние в двоич- ном коде отображается на светодиодах 20

Затем обучаемый подает входные сигналы при помощи управляющей клавиатуры 11, при этом блок 12 устраняет дребезг контактов клавиатуры и воздействует через блок 2, который отображает двоичньй код входного сигнала, на внешние входы автомата, подключенные к коммутатору 3 При этом блоки 21 воспринимают входные и выходные сигналы элементов 18. Инвертор 23 (фиГо2) инвертирует сигнал с входа элемента 18, элемент 25 производит операцию логического умножения над сигналами, поступающими с выхода инвертора 23 и выхода элемента 18„ Элемент 24 производит операцию логического умножения над сигналами элемента

18о Элемент 26 производит операциюзО памяти, прямые выходы которых сое- логического сложения сигналов, посту- динены с первыми входами блоков ин- пающих с выходов элементов 24 и 25, дикации первой группы и с первыми

Таким образом, блок 21 реализует входами коммутаторов второй группы, функцию, соответствующую таблице а инверсные выходы подключены к втотинности состояний элемента IB, Полу- 5 РЫм входам коммутаторов второй группы, ченная функция принимает значение логического нуля,в том-, случае, если элемент 18 в последующем тамте установится в нулевое состояние,-при

выходы которых являются соответству- ющими выходами второй группы устройства, третью группу коммутаторов, входы которых являются соответствую- этом светодиод 22 не горит, и значе- |40 щими входами второй группы устройст- ние логической единицы - в противном ва, а выходы соединены с соответствую- случае, при этом светодиод 22 горит щими входами логических элементов. Поэтому, считывая индикацию по све-: выходы которых подключены к входам тодиодам 22, обучаемый получает двоич- соответствующих блоков индикации вто- ную информацию, отмечаемую в каждой д рой группы и коммутаторов четвертой клетке таблицы переходов выходов без группы, выходы которых являются соот- дополнительных операций, только пу- ветствующими выходами третьей группы тем изменения комбинации входных сиг- устройства, отличающееся налов. Это позволяет получить мате- тем, что, с целью расщирения дидакти- матическую модель синтезированного g ческих возможностей устройства, в автомата. Во время построения матема- него введена группа блоков прогнозиро- тической модели обучаемый производит отладку автомата, используя дополнительно блоки 15, отображающие выходные состояния каждого из элементов 14о Затем производится проверка выполнения заданных условий работы син- feзиpoвaннoг6 автома.та в синхронном ручном и автоматическом режимах, ис,

вания, каждый из которых содержит инвертор, первый и второй элементы И и элемент ИЛИ, выход которого соеди- сс нен с вторым входом соответствующего блока индикации первой группы, а первый и второй входы - с выходами соответственно первого и второго элементов И, первые входы которых подклюпользуя генератор 7 одиночных импульсов, генератор 8 и переключатель 9 и подавая сигналы синхронизации на входы синхронизации элементов 18 с коммутатора Зо

Таким образом, введение блоков 21 прогнозирования (последующего состояния ) существенно расширяет дидактические возможности устройства прн обучении основам дискретной техники и coKpaciaeT за счет этого количество экспериментов для построения математической модели синтезированного автомата

Формула изобретения

Устройство для обучения основам вычислительной техники, содержащее пульт оператора, выходы которого подключены к соответствующим входам

блока индикации и коммутатора, выходы которого являются соответствующи- ми выходами первой группы устройства, первую группу коммутаторов, входы которых являются входами первой группы устройства, а выходы соединены с соответствующими входами элементов

выходы которых являются соответству- ющими выходами второй группы устройства, третью группу коммутаторов, входы которых являются соответствую- щими входами второй группы устройст- ва, а выходы соединены с соответствую- щими входами логических элементов. выходы которых подключены к входам соответствующих блоков индикации вто- рой группы и коммутаторов четвертой группы, выходы которых являются соот- ветствующими выходами третьей группы устройства, отличающееся тем, что, с целью расщирения дидакти- ческих возможностей устройства, в него введена группа блоков прогнозиро-

вания, каждый из которых содержит инвертор, первый и второй элементы И и элемент ИЛИ, выход которого соеди- нен с вторым входом соответствующего блока индикации первой группы, а первый и второй входы - с выходами соответственно первого и второго элементов И, первые входы которых подклю5139А2226

чены соответственно к прямому и ин- инвертора, второй вход второго версному выходам соответствующего элемента И и вход инвертора под- элемента памяти, второй вход перво- ключены соответственно к I и К-входам го элемента И соединен с выходом соответствующего элемента памяти.

От 18

9li}

,

Ш1

26

KIZ

25

Фиг.г

Авторы

Даты

1988-05-07—Публикация

1986-03-11—Подача