Изобретение относится к вычисли-т тельной технике и предназначено для реализации узлов и устройств цифровы вычислительных машин методами интегральной технологии со средним и боль шим уровнями интеграции. Известен комбинированный операционный элемент на RS-триггерах, содержащий КЗ-триггеры, элементы И, элемент НЕ и комбинационный одноразрядный сумматор fl. Недостатками известного элемента йвляются ограниченные функциональные возможности и большая .избыточность аппаратуры из-за,применения сложного устройства в виде комбинационного сумматора. Наиболее близким техническим решением к предлагаемому является упра ляемый арифметический модуль, содержащий основной триггер, первую управ ляемую логическую схему, которая содержит двенадцать элементов И, четыре элемента ИЛИ, ури элемента НЕ и инвертор, вторую управляемую логичес Кую Схему, которая содержит четыре элемента И и один элемент ИЛИ, четыре логических и девять управлякицих входов, а также два выхода, причём выходы первого, второго, третьего и четвертого элементов И через первый элемент ИЛИ соединены с прямым входом основного триггера, а выхода пятого, шестого и седьмого элементов И через второй элемент ИЛИ подключены .к инверсному входу основного триггера, прямой выход которого через nepBidt вход десятого элемента И связан с первым входом четвертого элемента ИЛИ, второй вход которого подключен к выходу одиннадцатого элемента Ир а первые входы первого, третьего, четвертого и восьмого элементов И соединены, соответственно, с первым, вторым, третьим и четвертым управляющими входами, а вторые входы первого, третьего и четвертого элементов И подключены соответственно к первому, второму и третьему логическим входс1М, а первые входы пятого и шестого элементов И соединены со вторым и третьим управляющими входами, второй вход восьмого элемента И связан с первым логическим входом, а выход через первый и второй схемы ИЛИ подключены соответственно к прямому и инверсному .основного триггера, прямой выход которого подключен к первым входам десятого и одиннадцатого элементов И, через ВТОРО.Й вход последнего связаны первый выход модуля и десятый управляющий вход, а одиннадцатый управляющий вход соединен с первым входом второго элемента И, второй вход которого через инвертор связан с первым Iуправляющим входом и вторым входом десятого элемента И двенадцатый управляющий вход соедин |СО вторым входом девятого элемэнта и с первым входом четвертого элемен та ИЛИ, второй вход которого через свой выход и через первый вход двенадцатого элемента И связан с входами первого и второго элементов ИЛИ, второй вход двенадцатого элемента И связан с тринадцатым управляю1цр1М входом и через первый вход тринадцатого элемента И - со вторым выходом МО дул я (, а второй вход этого элемента подключен к выходу третьего элемента ИЛИ, един из входов первого элемента ИЛИ соединен с выходом четырнадцатого элемента И, который через первый вход связан с выходом пятого элемента ИЛИ, первый вход которого подключен к первым входам пятнадцатого и шестнадцатого элементов И и первым логическим вхо дам, второй вход связан с восьмым управляющим входом и вторым входом четырнадцатого элемента И, последНИИ вход первого элемента ИЛИ через второй вход шестнадцатого элемента .И связан с седьмым управляющим входом и первым входом седьмого элемента И,второй вход которого через первый элемент НЕ и через второй вход пятнадцатого элемента И соединен с первым управляющим входом, а второй и третий управляющие входы через второй и третий элементы НЕ подключены ко вторым входам соответственно пятого и шестого элементов И 2 , .. Однако в известном управляемом арифметическом модуле функциональные- возможности ограничены, поэтому невозможноего использование для ре алиэации нерегулярных устройств ЦВМ (например, устройства управления). Цель изобретения - расширение функциональных возможностей за счет увелич ения числа выполняемых операПоставленная цель достигается те что управляемый арифметический моду содержащий основной триггер, тринад цать элементов. И, четыре Элемента ИЛИ,причем выходы первого,второго, третьего и четвертого элементов и с динены со входами первого элемента выход которого соединен о прямш вх дом основного триггера,а выходы пят JC4S,шестого и седьмого элементов И с динены со входами второго элемента ИЛИ, выход которого подключен к инверсному входу основного триггера, прямой выход которого соединен с пе вым входом восьмого элемента И, выод которого соединен с первым вхоом третьего элемента ИЛИ, второй вход которого подключен к выходу девятого элемента И, а первые входы первого, четвертого, третьего и .десятого элементов И соединены соответственно с первым, вторым, третьим и четвертым управляющими входами управляемого арифметического модуля, а вторые входы первого, третьего и четвертого элементов И подключены соответственно к первому, второму и третьему информационным входам управляемого арифметического модуля, первые входы пятого и шестого элементов И соединены со вторым и третьим управляющими входами управляемого арифметического модуля, второй вход десятого элемента И соединен с первым информационным входом управляемого арифметического модуля, дополнительно содержит триггер и три элемента ИЛИ, причем первые входы второго и седьмого элементов И подключены к выходу четвертого элемента ИЛИ, первый и второй входы которого подключены к выходс м соответственно десятого и одиннадцатого элементов И, а вторые входы второго и седьмого элементов И подключены соответственно к первому и в.торому выходу управляемого арифметического модуля ,а также к инверсному и прямому выходам дополнительного триггера, прямой вход которого подключен к выходу третьего элемента ИЛИ, а инверсный вход подключен к выходу пятого элемента ИЛИ, пятый управляющий вход управляемого арифметического модуля соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом двенадцатого элемента И, первый вход которого соединен С инверсным выходом основного триггера и третьим выходе управляемого арифметического модуля, а .второй вход соединен с выходом шестого элемёнт.а ИЛИ, первый вход которого соединен с шестым управляющим входом управляемого арифметического модуля и первым входом седьмого элемента ИЛИ, а седьмой и восьмой управляющие входы управляемого арифметического модуля подключены ко вторь входам соответственно шестого и седьмого элементов ИЛИ, третьи входы которых соединены с выходом тринадцатого элемента И, первый вход которого соединен с девятым управляющим входом управляемого арифметического модуля и с перв/ым входом одиннадцатого элемента Hf.второй вход которого соединен UO вторым информационным входом управляемого арифметического модулу, четвертый информационный вход которого соединен с первым входом девятого элемента И,- второй вход которого подключен к десятому управляющему входу управляемого арифметического модуля, пятый и шестой информаци онные входы которого соединены со вторьдми входами соответственно пято го и шестого,элементов И, причем вт рой вход шестого элемента И соединен со вторым входом тринадцатого элемента И, а одиннадцатый управляю щий вход управляемого арифметическо го модуля соединен с одним из входо второго элемента ИЛИ, а четвертый выход управляемого арифметического модуля соединен с прямым выходом о новного триггера. На чертеже схематически представ лен предлагаемый арифметический мо дуль . Управляемый арифметический модул .содержит основной триггер 1, вспомогательный триггер 2, первый управ ляем1 й логический блок 3 выработки сигналов установки триггера, девять элементов И 4-12, три элемента ИЛИ 13-15, второй управляемый логически блок 16 выработки сигналов установки триггера, четыре элемента И 1720, четыре элемента ИЛИ 21-24, шест информационных 25-30 и одиннадцать управляющих 31-41 входов управляемо го арифметического модуля, а также четыре выхода 42-45 управляемого ло гического модуля. Первый управляемый логический блок 3 выработки сигналов установки триггера включает семь элементов И 4-10, два элемента ИЛИ 13-14, два элемента И 17-18 и элемент ИЛИ 21. Второй управляемый логический блок 16 выработки сигналов установки триггера включает два элемента И 11-12, четыре элемента ИЛИ 15 и 2224 и два элемента И 19-20. На информационные входы модуля подаются следующие сигналы: i-и разряд кода X (вход ,25); i-и разряд кода Y (вход содержимое соседнего старшего разряда (вход содержимое соседнего старшего разряда (вход содержимое соседнего младшего разряда (вход содержимое соседнего младшего разряда (вход 29); V -г V управляющие сигналы (входы 31-41 соответственно) . Сигналы V. - У обеспечивают выпо нение следующих операций: V (вход 31) - прием операнда х в основной триггер 1 и логическое сложение; У (вход 32) - сдвиг в сторону младших разрядов; Vo, (вход 33) - сдвиг в сторону старших - разрядов; V (вход 34) - сложение по mod 2Р Vg. (вход 35) - установка на нуль дополнительного триггера 2; V (вход 36) - перепись кода с основного Триггера 1 в дополнительный триггер 2; V (вход 37) - конъюнкция содержимых основного 1 и дополнительного 2 триггеров; Vg (вход 38) - дизъюнкция содержимых основного 1 и дополнительного 2 триггеров; Vg (йход 39) - двоичный счет; (вход 40) - прием операнда у. в дополнительный триггер 2; V (вход 41) - установка на нуль основного триггера 1. С помощью управляемого арифметического модуля реализуется все 16 функций булевой алгебры двух переменных, некоторые функции трех и четырех переменных, функция двух самостоятельных регистров с числами разрядов п (если имеются п управляемые арифметические модули),функция одного 2 п-разрядного регистра, функция преобразования параллельного, кода в последовательный и наоборот, функция регистра сдвига кода в последовательный и наоборот, функция регистра сдвига кода числа в сторону старших разрядов, функция регистра сдвига числа в сторону младших разрядов, функция двоичного суммирующего или вычитающего счетчика, функция кольцевого регистра сдвига как в сторону младших, так и в сторону старших разрядов, функция распространения единицы нуля и др. С помощью управляемого арифметического модуля реализуется как сингулярные булевые функции и все логические функции двух переменных, так и некоторые функции трех и четырех переменных. В табл.1 приведены все булевые функции двух переменных и логические выражения для их реализации на управляемом арифметическом модуле. С целью иллюстрации реализации логических функций на управляемом арифметическом модуле приведено описание функционирования модуля при реализации конъюнкций, дизъюнкций и сложение по mod 2. Функция поразрядной конъюнкции двух двоичных чисел выполняется следующим образом. Операнд х- подается на четвертый информационный вход 28 и сигналом V,o (вход 40) , через элементы И 12 и ИЛИ 15 V заносится в дополнительный триггер 2. Операнд у. подается на первый инфорационный вход 25 и сигналом V (вход 31) через первый элемент И 4 и первый элемент ИЛИ 13 заносится в основной триггер 1. Предварительно основной 1 и дополнительный 2 триггеры соответственно сигналами V (вход 41) и Vc (вход 35) устанавливаются в нулевое состояние. Для осуществления операции конъюнкции подается сигнал V (вход 37) и содержимое основного триггера. 1 с инверсного выхода через элементы И 19 и ИЛИ 22 переписывается в дополнительный триггер 2, В ре зультате в дополнительном триггере 2 (выход 43) устанавливается логическое произведение . Функция поразряднсэй дизъюнкции выполняется следующим образом. Сигналами V (вход 41) и V5 (вход 35). основной 1 и дополнительный 2 триггеры устанавливаются в нулевое состояние. Сигналами (вход 40) и V (вход 31) аналогично -предыдущей операции соответственно х. заносится в дополнительный 2, а у - в основно 1 триггеры. Дизъюнкция осуществляется сигналом Vg (вход 38). Содержимое основного триггера 1 через элементы И 11 и ИЛИ 21 переписывается в допол нительный триггер 2, в котором окажет ся логическая сумма операндов х и у Функция поразрядной дизъюнкции реализуется также при подаче управляющих сигналов V (вход 31) и .V (вход 40) , Прямые коды у. и х подаются на первый 25 и четвертый 28 информационные входы и через первый 4 и девятый 12 логические элементы И подаются на прямые входы основного 1 и дополнительного 2 триггеров. В результате в основном триггере 1 получаем логическую сумму у. v у., , а в дополнительном триггере 2 - x-fv х.| , где у их,- содержимое основного 1 и дополнительного 2 триггеров, т.е. третий и четвертый переменные. Далее можно получить (у. V у,) V (x.VJ) или (у V у. ) (х N х1)и т.д. Функция сложения по mod 2 двух двоичных операндов и у выполняется ел едующим образом. Сигналами Уд (вход 41) и (вход 35) вспомогательный 2 и основной 1 триггеры устанавливаются в нулевое состояние. Сигналом V (вход 34) через десятый элемент И 17 операнд х от первого информационного входа 25 через четвертый элемент ИЛИ 21 подается на первые входы второго 5 и седьмого 10 элементов И, в результате чего в основном триггере устанавливается сумма D ( ® - сложение по mod 2). Сигналом Vg, (вход 36) содержимое основного триггера 1 переписывается в дополнительный триггер. Повторно подается сигнал V4 (вход 34) и второй операнд у., подаваемый с первого информационного входа 25, пройдя элементы И 8, 17, 5 и 10 в основном триггере устанавливает сумму :х + . Результат выдается на четвертом выходе 45 модуля. Здесь можно осуществить логические функции ( )V (х ® z ) или ( УТ)С&(Х Z-) и др. (здесь z третья переменная). Для реализации функций Пирса;Шеффера и эквивалентности производится дизъюнкция, конъюнкция и сложение по mod 2 соответственно и результаты устанавливаются на инверсном выходе (первый выход модуля, выход 42) дополнительного триггера 2. Таблица

Продолжение табл. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Управляемый арифметический модуль | 1988 |

|

SU1585792A2 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Реверсивный регистр сдвига | 1983 |

|

SU1176385A1 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| Устройство для деления п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU807282A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

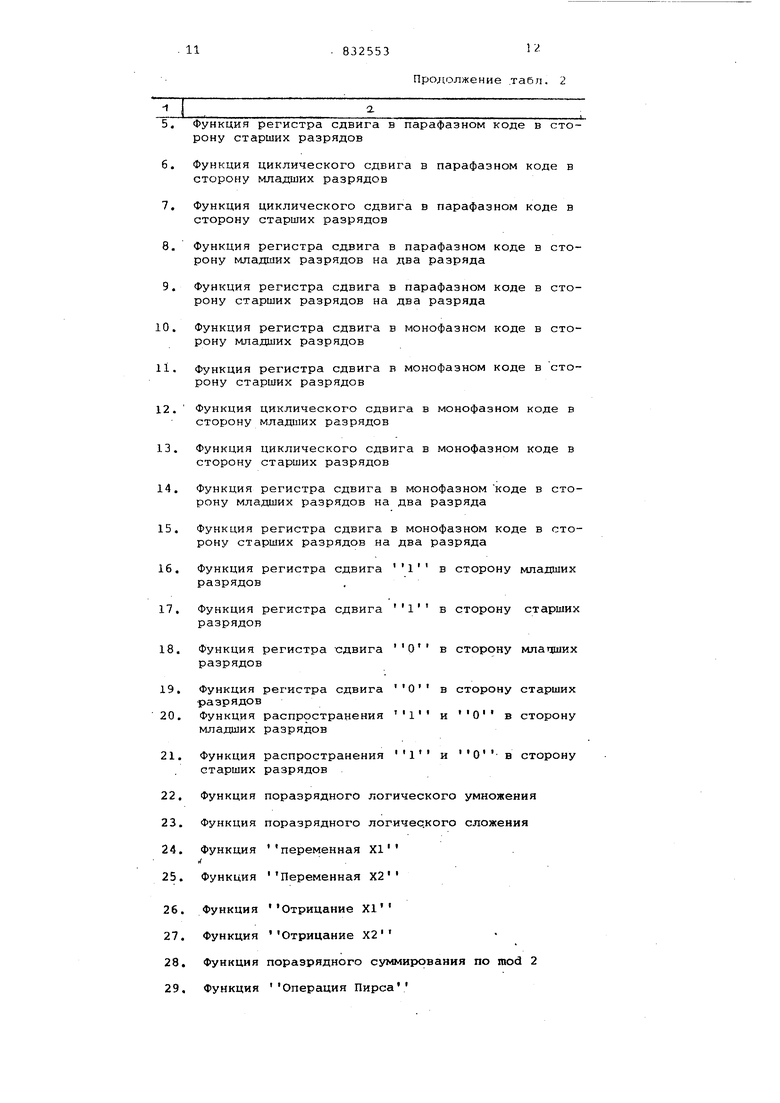

Функция сдвига в сторону младших разрядов осуществляется за два полутакта. В первом полутакте сигналом V (вход 33) парафазный код содержимого.вспомогательного триггера Т. (Q,(b..i) через информационные входы 21 vi 29 и через четвертый и пятый элементы И 7 и 8 переписывается в основной триггер i-ro разряда. Перепись из основ ного триггера Т. 1 в дополнительный триггер осуществляется сигналом V (вход 36). Функция сдвига в сторону старших разрядов осуществляется аналогично предыдущему за два полутакта. Сигна лом V/3L (вход 32) парафазный код содержимого триггера подается на информационные входы 26 и 30 i-ro модуля. Открывается третий элемент И 6 или шестой элемент И 9 и возбуж дается соответствующий вход триггера . Перепись в дополнительный триггер осуществляется сигналом V (вход 36). Счетчик работает как обычный дву тактный суммирующий двоичнЕЛй сче чик с последовательным переносом. Двоичный счет осуществляется пос ле установки на нуль основного 1 и дополнительного 2 триггеров сигналами V (вход 41) и Vj(вход 35), Пр этом первый выход 42 i-ro модуля со диняется с шестым информационным . входом 30 (i Ч--1 )-го модуля, а второй выход 43 - со вторым информационным входом 26. Парафазный импульс счета через второй и шестой информа

№0

Наименование реализуемой функции пп

Функция п -разрядного регистра

Функция п -разрядного регистра с расширенными функциональными возможностями

Функция 2п - разрядного регистра

Функция регистра сдвига в парафазном коде в сторону млада их разрядов ционные входы 26 и 30 поступает на входы одиннадцатого 18 и тринадцатого элементов И 20 первого младшего разряда. До начала счета на второй информационный вход 26 первого младшего разряда подается низкий уровень парафазного импульса счета, а на шестой информационный вход 30 высокий уровень импульса. В первом полупериоде импульс счета через одиннадцатый элемент И 18, четвертый элемент ИЛИ 21 и второй 5.и седьмой 10 элементы И переводит основной триггер 1 первого разряда из состов состояние время дополнительный триггер 2 не изменит своего состояния, так как на шестой информационный вход 30 первого разряда подается низкий уровень парафазного импульса счета. За второй полупериод дополнительный триггер 2 изменит свое состояние. В это время основной триггер 1 второго разряда переходит в состояние 1 , После подачи второго парафазного импульса счета дополнительный триггер 2 первого разряда переходит в состоа дополнительный триггер 2 второго разряда и основной триггер 1 третьего разряда - в состояние 1 и т.д. Благодаря введенному в устройство первому выходу 42 управляемый арифметический модуль работает в режиме двоичного вычитающего счетчика. В табл.2 представлены 39 функций, реализуемые управляемым арифметическим модулем. Таблица2

. 11. 832553

разрядов

старших разрядов

Продолжение .табл. 2

Функция Операция Шеффера

Функция Константа

Функция Запрет по XI

Функция Запрет по Х2

Функция Импликация от XI и Х2

Функция импликация от Х2 к XI

Функция двоичного суммирующего счетчика

Функция двоичного счетчика

Функция преобразования последовательного кода в параллельный и наоборот

Функция счетчика Джонсона Применение управляемого арифметического модуля позволяет получить технический эффект, заключающийся в значительном увеличении функциональных возможностей за счет введения в модуль новых связей и логических элементов. С помощью прототипа можно выполнить 15, ас помощью данного управляемого арифметического модуля 39 различных логических, арифметичес ких и вычислительных функций. Формула изобретения Управляемый арифметический модул содержащий основной триггер, тринад цать элементов И, четыре элемента ИЛИ, причем выходы первого, второго третьего и четвертого элементов И соединены со вхрдами первого элемента ИЛИ, выход которого соединен с прямым входом основного триггера, а выходы,пятого, шестого и седьмого элементов И соединены со входами вто рого элемента ИЛИ, выход которого подключен к инверсному входу основного триггера, прямой выход которого соединен с первым входом восьмого элемента И, выход которого соединен с первым входом третье о элемента ИЛИ, второй вход которого подключен к выходу девятого элемента И, а первые входы первого, четвертого, треть его и десятого элементов И соединены соответственно с первым, вторым, третьим и четвертым управляющими входами управляемого тарифметического модуля, а вторые входы первого, трет его и четвертого элементов И подключены соответственно к первому , второму; и третьему информационным входам управляемого арифметического модуля , первые входы пятого и шестого элементов И соединены со вторым и

Продолжение табл. 2 третьим управляющими входами управляющего арифметического модуля, второй вход десятого элемента И соединен с первым информационным входом управляемого арифметического модуля, отличающийся тем, что, с целью расширения функциональных возможностей за счет выполнения двадцати четырех дополнительных арифметических и логических операций, в него введены дополнительно триггер и три элемента ИЛИ, причем первые входы второго и седьмого элементов И подключены к выходу четвертого элемента ИЛИ, первый и второй входы которого подклю.чены к выходам соответственно десятого и одиннадцатого элементов И, а вторые входы второго и седьмого элементов И подключены соответственно к первому и второму выходу управляемого арифметического модуля, а также к инверсному и прямому выходам . дополнительного триггера, прямой вход которого подключен к выходу третьего элемента ИЛИ, а инверсный вход подключен к выходу пятого элемента ИЛИ, пятый управляющий вход управляемогб арифметического модуля соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом двенадцатого элемента И, первый вход которого соединен с инверсным выходом основного триггера и третьим выходом управляемого арифметического модуля, а второй вход - соединен с выходом шестого элемента ИЛИ, первый вход которого соединен с шестым управляющим входом упргшляемого арифметического моду;1Я и первым входом седьмого элемента ИЛИ, а седьмой и восьмой управляюцие входы управляемого арифметического модуля подключены ко вторым входам соответственно шестого и седь

Авторы

Даты

1981-05-23—Публикация

1979-07-19—Подача