(54) ТРЕХДЕКАДНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1005027A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1193824A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU930313A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Преобразователь дифференциально-разностного кода в двоичный | 1988 |

|

SU1594704A1 |

| Устройство для определения направления и угла поворота вращающегося объекта | 1991 |

|

SU1786441A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| Следящий стохастический интегратор | 1982 |

|

SU1061141A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоичнодесятичных преобразователей в вычислительных машинах и внешних устройствахвычислительных систбм.

Известен преобразователь двоичнодесятичного кода в двоичный, содержащий многоразрядные комбинационные сумматоры, одноразрядные сумматоры и элементы ИЛИ Cl.

Недостаток известного устройства заключается в относительно большом объеме аппаратуры и невысокой скорости преобразования.

Наиболее близким к изсбретению по технической сущности и схемному построению является трехдекадный преобразователь двоично-десятичного двоичный, содержащий первый и второй сумматоры и элементы ИЛИ. Кроме того, данный преобразователь содержит еще два сумматора 2.

Недостаток данного преобразователя также оостоит в относительно большом объеме аппаратуры и низком быстродействии.

Целью изобретения является сокращение аппаратуры и увеличение быстродействия.

Поставленная цепь достигается тем, что в трехдекадный преобразователь двоично-десятичного кода в Двоичный,

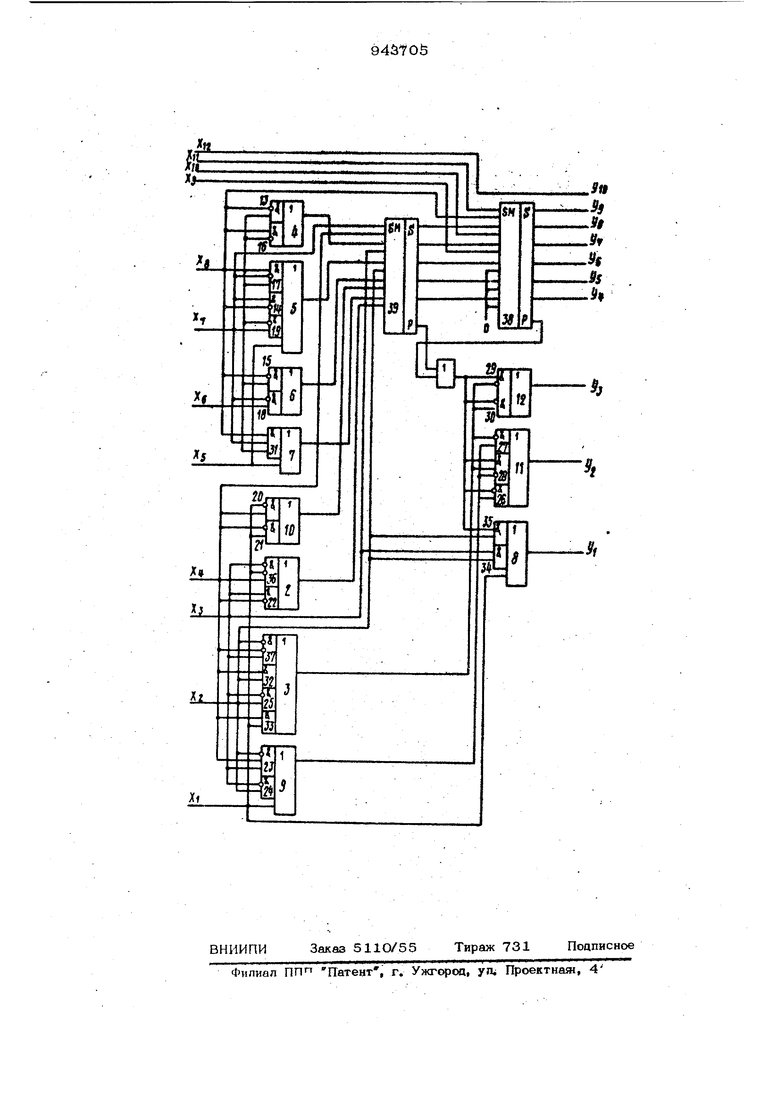

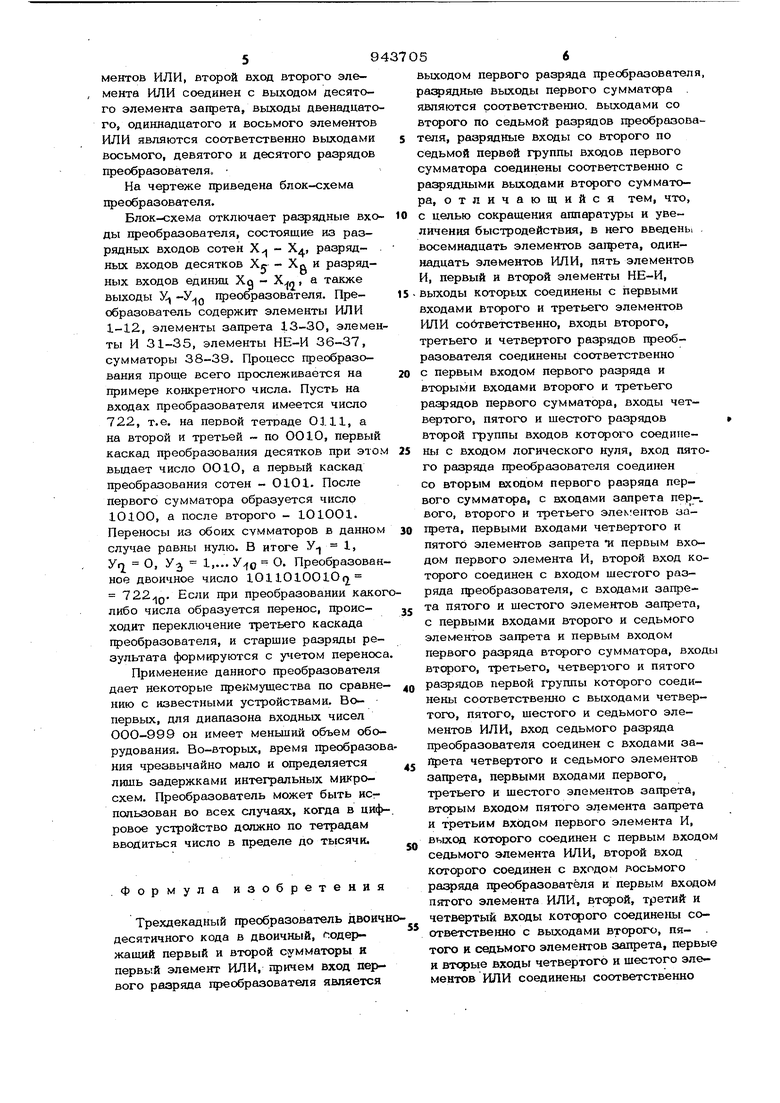

10 содержащий первый и второй сумматоры и первый элемент ИЛИ, причем вход первого разрзда преобразрвателя является выходом первого разряда преобразователя, разрядные выходы первого сумма15тора являются соответственно выходами со второго по седьмой разря.ов хдзеобразователя, разрядные входы со второго tio седьмой первой груш1ы входов первого сумматсра соединены соответствен20но с разрядными выходами второго сум-. матера, введены восемнадцать элементов запрета, одиннадцать элементов ИЛИ., , пять элементов И, первь1Й и второй элементы НЕ-И, выходы которых соединен с первыми входами второго и третьего элементов ИЛИ соответственно, входы второго, третьего и четвертого разрядо преобразователя соединены соответстве но с первым входом первого разряда и вторыми входами второго и третьего разрядов первого сумматора, входы чет вертого, пятого и шестого разрядов вто рой группы входов которого соединены с входом логического нуля, вход пятого разряда преобразователя соединен со вторым входом первого разряда первого сумматора, с входами запрета первого, второго и третьего элементов запрета, первыми входами четвертого и пятого элементов запрета и первым входом первого элемента И, второй вход котор го соединен с входом шестого разряда преобразователя, с входами запрета пятого и шестого элементов за15)ета, с первьши входами второго и седьмого элементов запрета и первым входом первого разряда второго сумматора, входы второго, третьего, четвертого и пятого разрядов первой группы которого соединены соответственно с выходами четвертого, пятого, шестого и седьмого элементов ИЛИ, вход седьмого разряда преобразователя соединен с входами запрета четвертого и седьмого э ементов запрета, первыми входами перво го, третьего и шестого элементов запре та, вторым входом пятого элемента запрета и третьим входом первого элемента И, Выход которого соединен с первым входом седьмого элемента ИЛИ Второй вход которого соединен с входом восьмого разряда преобразователя и первым входом пятого элемента ИЛИ, второй, третий и четвертый входы кото рого соединены соответственно с выходами второго, пятого и седьмого элеме тов запрета, первые и вторые входы четвертого и шестого элементов ИЛИ соединены соответственно с выходами п вого, третьего, четвертого и шестого элементов запрета, вход девятого разряда преобразователя соединен с входом восьмого элемента запрета, с входами запрета девятого и десятого элементов запрета, с первыми входами второго и третьего элементов И, с первым входом одиннадцатого элемента запрета, с прямым и первым инверсным входами первого и второго элементов НЕ-И и с входом первого разряда второй группы второго сумматора, входы второго и третьего разрядов второй группы кото- рого соединены соответственно с входами десятого и одиннадцатого разрядов преобразователя, с первым входом четвертого и первым входом пятого и вторым входом четвертого элементов И, выходы которых соединены соответственно с первым и вторым входами восьмого элемента ИЛИ, третий вход которого со.единен с входом двенадцатого разряда греобразователя, с .первым входом девятого элемента ИЛИ, со вторым входом третьего элемента И, с первым инверсным входом первого элемента НЕ-И, с входом запрета и прямым входом восьмого и девятого элементов загфета, выходы которых соединены с входами десятого элемента ИЛИ, вход десятого разряда преобразователя соединен со вторым инверсным входом первого и прямым входом второго элементов НЕ-И, входами запрета одиннадцатого и двенадцатого элементов запрета и вторым входом одиннадцатого элемента запрета, вход одиннадцатого разряда преобразователя соединен со вторым инверсным входом второго элемента НЕ-И, втсрым входом второго элемента И, входом тринадцатого элемента запрета, входом и входом запрета одиннадцатого, и двенадцатого элементов запрета, выходы которых соединены соответственно со вторым и третьим входами девятого элемента ИЛИ выход которого соединен с Входами четьфнадцатого и пятнадцатого и входом запрета шестнадцатого элементов запрета, выходы которых соединены со входами одиннадцатого элемента ИЛИ, выход второго и третьего эпеме1ггов И и выход тринадцатого элемента запрета соединены соответственно со вторым, третьим и четвертым входами третьего элeмe тa ИЛИ, выход котс ого соединен со вторым входом шестнадцатого и входом запрета пятнадцатого элементов запрета, а также с входом запрета и входом семнадцатого и восемнадцатого элементов запрета, выходы которых соединены с первым и вторым входами двенадцатого элемента ИЛИ, втqpыe входы пятого элемента И, шестнадцатого элемента запрета, входы запрета четьфнадцатого и восемнадцатого элементов запрета и вход семнадцатого элемента защэета через первый элемент ИЛИ соединены с выходами переноса первого и втсрого сумматоров, вторые входы четвертого и пятого разрядов второго сумматора соединены соответственно с выходами десятого и второго эле- i ментов ИЛИ, второй вход второго элемента ИЛИ соединен с выходом десятого элемента защзета, вь1ходы двенадцат го, одиннадцатого и восьмого элементов ИЛИ являются соответственно выходами восьмого, девятого и десятого разрядов преобразователя. На чертеже приведена блок-схема преобразователя. Блок-схема отключает разрядные вхо ды преобразователя, состоящие из разрядных входов сотен Х - X,, разрядных входов десятков Хе - Хп и разрядных входов единиц Хо - Х также выходы У, преобразователя, Преобразователь содержит элементы ИЛИ 1-12, элементы запрета 1.3-ЗО, элеме ты И 31-35, элементы НЕ-И 36-37, сумматоры 38-39. Процесс преобразования проще всего прослеживается на примере конкретного числа. Пусть на входах преобразователя имеется число 722, т.е. на первой тетраде 0111, а на второй и третьей по ОО10, первый каскад преобразования десятков при это вьщает число ОО10, а первый каскад преобразования сотен - 0101. После первого сумматора образуется число 1О100, а после второго - 101001. Переносы из обоих сумматоров в данно случае равны нулю. В итоге У- - 1. Уг О, УЗ 1,... О Преобразован ное двоичное число 10HO100lO(j 722/IQ. Если при преобразовании како либо числа образуется перенос, происходит переключение третьего каскада преобразователя, и старшие разрады результата формируются с учетом перенос Применение данного преобразователя дает некоторые преимущества по сравне нию с известными устройствами. Вопервых, для диапазона входных чисел ООО-999 он имеет меньший объем обо рудования. Во-вторых, время преобразо ния чрезвычайно мало и определяется лишь задержками интегральных микросхем. Преобразователь может быть использован во всех случаях, когда в циф ровое устройство должно по тетрадам вводиться число в пределе до тысячи. Формула изобретения Трехдекадный преобразователь двоич десятичного кода в двоичный, (содержащий первый и второй сумматоры и первый элемент ИЛИ, щ)ичем вход первого разряда преобразователя является ВЫХОДОМ первого разряда преобразователя, ра фящные вькоды первого сумматора . являются соответственно, выходами со второго по седьмой разрядов преобразователя, разрядные входы со второго по седьмой первой группы входов первого сумматора соединены соответственно с разрядными выходами сумматора, отличающийся тем, что, с целью сокращения аппаратуры и увеличения быстродействия, в него введень . восемнадцать элементов защэета, одиннадцать элементов ИЛИ, пять элементов И, первый и второй элементы НЕ-И, выходы которых соединены с первыми входами BTqporo и третьего элементов ИЛИ соответственно, входы второго, третьего и четвертого разрядов преобразователя соединены соответственно с первым входом первого разряда и вторыми входами второго и третьего разрядов первого сумматора, входы четвертого, пятого и шестого разрядов второй группы входов соединены с входом логического нуля, вход пятого разряда преобразователя соединен со вторым входом первого разряда первого сумматора, с входами запрета пер-, вого, второго и третьего элe eмтoв аатфета, первыми входами четвертого и пятого элементов запрета и первым входом первого элемента И, второй вход котс ого соединен с входом шестого разряда гфеобразователя, с входами запрета пятого и шестого элементов запрета, с первыми входами второго и седьмого элементов запрета и первым входом первого разряда втсрого сумматора, входы Второго, третьего, четвера ого и пятого разрядов первой группы которого соединены соответственно с вьосодами четвертого, пятого, шестого и седьмого элементов ИЛИ, вход седьмого разряда преобразователя соединен с входами запрета четвертого и седьмого элементов запрета, первыми входами первого, третьего и шестого элементов запрета, вторым входом пятого элемента запрета и третьим входом первого элемента И, выход которого соединен с первым входом седьмого элемента ИЛИ, второй вход которого соединен с входом восьмого разряда преобразователя и первым входом пятого элемента ИЛИ, , третий и четвертый входы которого соединены соответственно с выходами второго, пятого к седьмого элементов запрета, первые и вторые входы четвертого н шестого элементов ИЛИ соединены соответственно

с выходами первого, третьего, четвертого к шестого элементов , вход девятого разряда преобразователя соединен с входом восьмого элемента запрета, с входами запрета девятого и десятого 5 элементов запрета, с первыми входами BTqjoro и третьего элементов И, с первым входом одиннадцатого элемента запрета, с прямым и первым инверсным входами первого и второго элементов НЕ-И ю и fc входом первого разряда второй группы второго сумматора, входы второго и .-третьего разрядов второй группы которого соединены соответственно с входами десятого и одиннадцатого разря- $ дов преобразователя, с первым входом четвертого и первым входом пятого и вторым входом четвертого элементов И, выходы котсрых соединены соответственно с первым и вторым входами восьмого jo элемента ИЛИ, третий вход которого соединен с входом двенадцатого разряда преобразователя, с первым входом девятого элемента ИЛИ, со вторым входом третьего элемента И, с первым инверс- 25 ным входом первого элемента НЕ-И, с входом запрета и прямым входом восьмого и девятого элементов запрета, выходы которых соединены с входами десятого элемента ИЛИ, вход десятого разряда преобразователя соединен со йЬорым инверсным входом первого и прямым входом второго элементов НЕ-И, входами запрета одиннадцатого и двенадцатого элеме1ггов запрета и вторым входом одиннадцатого элемента запрета, вход один-, надцатого разряда преобразователя соединен со вторым инверсным входом второго элемента НЕ-И, вторым входом второго элемента И, входом тринадцато- д. го элемента запрета, входом и входом запрета одиннадцатого и двенадцатого элементов защэета, выходы которых соединены соответственно со вторым я третьим Входами девятого элемента ИЛИ выход которого соединен с входами четьфнадцатого и пятнадцатого и входом за)прета шестнадцатого элементов загфета, выходы котсрых соединены со входами одиннадцатого элемента ИЛИ, выход второго и третьего элементов И и выход тринадцатого элемента запрета соединены соответственно со вторым, третьим и четвертым входами третьего элемента ИЛИ, выход которого соединен со вторым входом шестнадцатого и входом запрета пятнадцатого элементов защэета, а также с входом запрета и вход семнадцатого и восемнадцатого элементо , выходы которых соединены с первым и Вторым входами двенадцатого элемента ИЛИ, вторые входы пятого элемента И, шестнадцатого элемента запрета, входы запрета четырнадцатого и восемнадцатогЬ элементов защзета и вход семнадцатого элемента загфета через первый элемент ИЛИ соединены с выходми переноса первого и второго сумматоров, вторые входы четвертого к пятого разрядов второхчэ сумматора соединены соответственно с выходами десятого и второго элементов ИЛИ, второй вход второго элемента ИЛИ соединен с выходом десятого элемента запрета, выходы двенадцатого, одиннадцатого и восьмого элементов ИЛИ являются соответственно выходами восьмого, девятого и десятого разрядов преобразователя.

Источники информации, щзинятые во внимание при экспертизе

кл. G 06 F 5/О2, 21.О8.8О.

Авторы

Даты

1982-07-15—Публикация

1980-12-29—Подача