Изобретение относится к вычисли- Ъельной технике, предназначено для вычисления дискретного преобразования Фурье (ДПФ) и процедуры цифровой фильтрации и может быть использовано и системах цифровой обработки сигна- лов.

Цель изобретения - упрощение устройства .

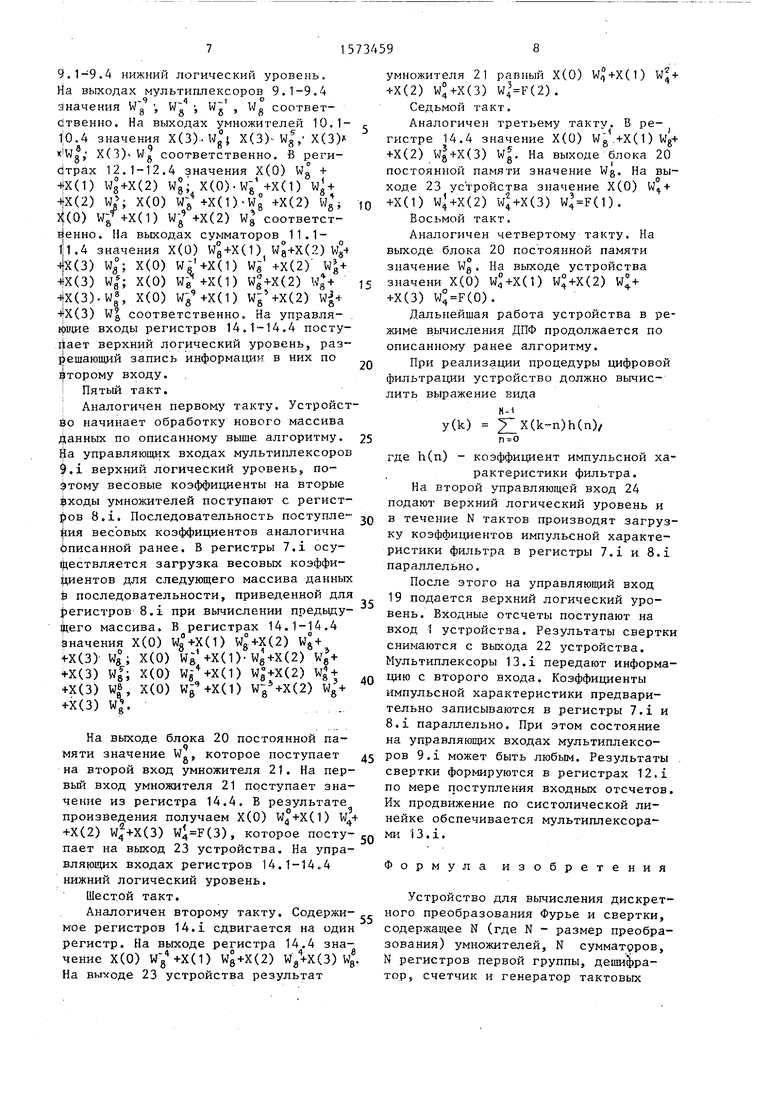

На чертеже изображена структурная схема устройства.

Устройство содержит первый информационный вход 1, второй информационный вход 2 (входной), мультиплексор 3, входной умножитель 4--, (входной) блок 5 постоянной памяти, блок 6 по- стоянной памяти весовых коэффициен- тов, регистры 7.1 (,N) весовых коэффициентов, регистры 8.1 весовых коэффициентов, мультиплексоры 9.1 весовых коэффициентов, умножители 10.1, сумматоры 11.1, регистры 12.1, мультиплексоры 13.1 передачи данных, Двухвходовые регистры 14.1, генератор 15 тактовых импульсов, счетчик 16, дешифратор 17, элемент-ИЛИ 18, вход 19 задания режима, блок 20 постоянной памяти, выходной умножитель 21, выход 22 свертки, выход 23 ДПФ, вход 24 задания режима, элемент И 25.

Рассмотрим работу устройства в режиме вычисления ДПФ, которое определяется выражением

N Е

К XN

F(0) F(1) F(2) F(3)

(1)

Wo

wa

W0

w

где XN - исходный комплексный вектор размерности N с элементами X(w)

FM - результирующий комплексный вектор размерности N с элементами F(k)}

Е - матрица весовых коэффициентов размерности N-N с элементами WJJ exp() J

1 лРТ.

Выражение (1) можно записать в следующем виде:

FKI GN TN GM

X

N

(2)

где Т м - теплицева матрица вида

- диагональная матрица

( ч

diag(W

2N

,w

N

Для описания примера работы устройства примем . В этом случае выражение (2) имеет вид

X(0) X(1) X(2) X(3)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления дискретного преобразования Фурье | 1988 |

|

SU1575202A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1577072A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1508233A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| ПОЛИНОМИАЛЬНЫЙ МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ С ОБНАРУЖЕНИЕМ ОШИБОК | 2015 |

|

RU2586574C1 |

| Устройство для вычисления свертки | 1989 |

|

SU1688259A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1545230A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1988 |

|

SU1589289A1 |

| Цифровой фильтр | 1986 |

|

SU1348981A1 |

Изобретение относится к вычислительной технике, предназначено для вычисления дискретного преобразования Фурье (ДПФ) и процедуры цифровой фильтрации и может быть использовано в системах цифровой обработки сигналов. Цель изобретения - упрощение устройства. В состав устройства входят входной умножитель 4, блоки постоянной памяти 5,6,20, регистры 7.I, 8.I (I=1,N

N - размер преобразования), 12.I, 14.I мультиплексоры 3, 9.I, 13.I, умножители 10.I, сумматоры 11.I, генератор тактовых импульсов 15, счетчик 16, дешифратор 17, элементы ИЛИ 18, И 25, ВЫХОДНОЙ УМНОЖИТЕЛЬ 21. ИМЕЮТСЯ ТАКЖЕ ИНФОРМАЦИОННЫЕ ВХОДЫ 1,2, ВЫХОД СВЕРТКИ 22, ВЫХОД ДПФ 23, ВХОДЫ ЗАДАНИЯ РЕЖИМА 19, 24. 1 ИЛ.

Будем полагать, что сумматоры 11.1 осуществляют операцию суммирования операндов при нижнем уровне на управляющем входе и операцию пересылки операнда с первого входа на выход при высоком уровне на управляющем входе. Регистры 14.1 осуществля

ют прием информации с первого входа при нижнем уровне на управляющем входе и с второго входа при высоком уровне на управляющем входе. При нижнем уровне на входе 19 устройства производится вычисление ДПФ, а при верхнем вычисляется свертка. Инфор515

нация с входа 2 устройства через умножитель 4 и мультиплексор 3 поступает без дополнительных тактировок, хотя дпя повышения быстродействия

за сч(- г увеличения тактовой частоты целесообразно ее протактировать после мультиплексора 3 или умножителя 4. Поскольку данная тактировка не нарушает принципов работы устройства, мы ее .не будем учитывать в дальнейшем описании работы устройства. На входе 24 устройства нижний логический уровень. При наличии нижнего логического уровня на управляющих входах ре- гистров 7.1 и 8.1 они производлт прие информации (при наличии синхроимпульса) . При верхнем логическом уровне на управляющих входах этих регистров они находятся в режиме хранения ин- формации. Информация во все регистры записывается положительным фронтом синхросигнала. Все мультиплексоры осуществляют передачу информации с первого входа на выход при нижнем ,уровне на управляющем входе, а с второго входа - при высоком уровне на управляющем входе. Считаем, что в регистры 7.1, 7.2, 7.3, 7.4 произведена предварительная запись информации

8 8 в я се опеРаВДы в Ре гистрах и арифметические операции

над ними комплексные.

Первый такт.

На управляющих входах сумматоров 14.1 в этом такте присутствует верхний логический уровень. С первого выхода блока 6 поступает значение Wg , с второго выхода блока 6 - Wa , с выхода блока 5 постоянной памяти - Wg3, на вход 2 устройства - Х(0). С выъода умножителя 4 снимается значение X(0)W°, которое через мультиплексор 3 поступает на первые входы умно- жителей 10.1-10.4. На управляющих входах мультиплексоров 9.1-9.4 нижний логический уровень, который поступает с соответствующего выхода счетчика 16. Поэтому на выходах мультиплексоров 9.1-9.4 будут значения Wg, Wg , Wg , W , поступающие на вторые входы соответствующих умножителей 10.1- 10.4. На выходах умножителей 10.1- 10.4 будут значения Х(0)- (0)-

x(o).w° W8 x(o).w-1 x(G).w8.Wg4

X(0). X(0). K°.(0)-W-/.

На выходах сумматоров 11.1-11.4 имеются значения X(0)-W8, Х(0) Wg ; X(0)-Wg4; X(0)-Wg соответственно,

59

В юрой такт.

Q 0 5 0

с

С первого выхода блока 6 поступает значение W , с второго выхода 4

WJ . В регистрах 7.1-7.4 значения Wg( ; W -, Wg ; Wg4 соответственно. В регистре 8.1 значение W8 . С выхода блока Ь поступает значение Wg . На входе 2 устройства значение Х(1). На выходе мультиплексора 3 значение X(1) Wg. На управляющих входах мультиплексоров 9.1-9.4 нижний логический уровень. На выходах мультиплексоров

8

w;

W

-4

Третий такт.

С первого выхода блока 6 поступает

- Qj

значение Ws , с второго выхода - Wg . В регистрах 7.1-7.4 значения W.41

w-« -- -8

-1

W,,,1 W соответственно. В реги 4

,-Ч

5

страх 8.1 и 8.2 значения Wg и We соответственно. На выходе блока 5 значение W. На входе 2 устройства значение Х(2). На выходе мультиплексора 3 значение Х(2)- W. На управляющих входах мультиплексоров 9.1-9.4 нижний логический уровень. На выходах мультиплексоров 9.1-9.4 значения

W

-4

W

-1

0

, wft , Wgj W соответственно. На выходаъ умножителей 10.1-10.4 значения X(2).W°i X(2 Wj, X(2) X(2) «Wg соответственно. В регистрах 12.1- 12.4 значения X(0)W°+X( 1 )Wg,-X(0) + +X(1)WJ,- X(0)Wg4+X(1)Wgi X(0)W89 + +X(1)W83 соответственно. В сумматорах 11.1-11.4 значения Х(0)Wg+X(1)Wg+ +X(2)W, X(0)W8 +X(1)W +X(2)W, X(0)(1)W8° +X(2) Wg% X(0)-Wg + +X(1) Wg +X(2) Wg соответственно.

Четвертый такт.

С первого выхода блока 6 поступает

- Ч

значение Wg , с второго выхода - значение Wa. В регистрах 7.1-7.4 значе } О J г | О

ния Wft ; Wft ; Wg ; W8 соответственно. В регистрах 8.1-8.3 значения W,- W , Wg соответственно. На выходе блока 5 значение W8, на входе 2 устройства значение Х(3), на выходе мультиплексора 3 значение Х(3). На управляющих выходах мультиплексоров

На выходах мультиплексоров 9.1-9.4

,,-9

значения W0

W , Wg , Wg соответс твенно. На выходах умножителей 10.1- 10.4 значения X(3).Wg°j X(3)-w|,- Х(3 Wo, X(3)W соответственно. В региООQ

4(3) wa°; x(o w; +x(D (2) w|+

4x(3) W85; X(0) ) WЈ+X(2) ttX(3).W83, X(0) Wg9+X(1) Wg +X(2) 4X(3) Wg соответственно. На управля- $щие входы регистров 14.1-14.4 посту- Йает верхний логический уровень, разрешающий запись информации в них по торому входу.

Пятый такт.

Аналогичен первому такту. Устройст- Йо начинает обработку нового массива данных по описанному выше алгоритму. На управляющих входах мультиплексоров $.1 верхний логический уровень, по- $тому весовые коэффициенты на вторые Входы умножителей поступают с регистров 8.1. Последовательность поступле- ия весовых коэффициентов аналогична писанной ранее. В регистры 7.1 осуществляется загрузка весовых коэффи- |щентов для следующего массива данных Ј последовательности, приведенной для регистров 8.1 при вычислении предыдущего массива. В регистрах 14.1-14.4 Значения Х(0) Wg+X(1) Wg+X(2) W + +Х(3) We°; X(0) We +Xd)- Wg+X(2) W.+ X(3) W|; X(0) We-4+X(1) (2) W +

+x(3) w|, x(o) ) Wg3+x(2) ws+

+X(3) W .

На выходе блока 20 постоянной памяти значение W , которое поступает на второй вход умножителя 21. На первый вход умножителя 21 поступает значение из регистра 14.4. В результате произведения получаем Х(0) W4+X(1) W4+ +Х(2) (3) (3), которое поступает на выход 23 устройства. На управляющих входах регистров 14.1-14.4 нижний логический уровень.

Шестой такт.

Аналогичен второму такту. Содержимое регистров 14.1 сдвигается на один регистр. На выходе регистра 14.4 значение Х(0) Wg4+X(1) Wg+X(2) W/+X(3) Wg На выходе 23 устройства результат

,-

5 o

5

5

0

5

умножителя 21 равный Х(0) (1) +Х(2) W°+X(3) (2).

Седьмой такт.

Аналогичен третьему такту. В регистре 14.4 значение Х(0) Wg +X(1) Wg+ +Х(2) Wg+X(3) Wg. На выходе блока 20 постоянной памяти значение W8. На выходе 23 устройства значение Х(0) +Х(1) (2) wJ+X(3) (1).

Восьмой такт.

Аналогичен четвертому такту. На выходе блока 20 постоянной памяти значение Wg. На выходе устройства значени Х(0) (1) W°+X(2) W°+ +Х(3) (0).

Дальнейшая работа устройства в режиме вычисления ДПФ продолжается по описанному ранее алгоритму.

При реализации процедуры цифровой фильтрации устройство должно вычислить выражение вида

y(k) ;r x(k-n)h(n),

где h(n) - коэффициент импульсной характеристики фильтра.

На второй управляющей вход 24 подают верхний логический уровень и в течение N тактов производят загрузку коэффициентов импульсной характеристики фильтра в регистры 7.1 и 8.1 параллельно.

После этого на управляющий вход 19 подается верхний логический уровень. Входные отсчеты поступают на вход 1 устройства. Результаты свертки снимаются с выхода 22 устройства. Мультиплексоры 13.1 передают информацию с второго входа. Коэффициенты импульсной характеристики предварительно записываются в регистры 7.1 и 8.1 параллельно. При этом состояние на управляющих входах мультиплексоров 9.1 может быть любым. Результаты свертки формируются в регистрах 12.1 по мере поступления входных отсчетов. Их продвижение по систолической линейке обспечивается мультиплексорами i 3.1.

Формула изобретения

Устройство для вычисления дискретного преобразования Фурье и свертки, содержащее N (где N - размер преобразования) умножителей, N сумматоров, N регистров первой группы, дешифратор, счетчик и генератор тактовых

импульсов, выход которого подключен к счетному входу счетчика, информационный выход которого подключен к

входу дешифратора, выход i-го (,N умножителя подключен к первому входу 1-го сумматора, выход j-го (,N-1) регистра первой группы подключен к первому информационному входу (j+1)- го регистра первой группы, а установочный вход счетчика является первым входом задания режима устройства, отличающееся тем, что, с целью упрощения, оно содержит три блока постоянной памяти, вторую, тре тью и четвертую группы из N регистров каждая, первую и вторую группы из N мультиплексоров, входной умножитель, выходной умножитель, элемент И, элемент ИЛИ и мультиплексор, выходы j-x регистров второй и третьей групп подключены к информационным входам (j+1)-x регистров соответственно второй и третьей групп, а выходы 1-х регистров второй и третьей групп подключены соответственно к первому и второму информационным входам 1-го мультиплексора первой груп

пы, выход которого подключен к первому входу 1-го умножителя, второй вход которого подключен к выходу мультиплексора, первый информационный вход которого является первым информационным входом устройства, вторым инфор- .мационным входом которого является первый вход входного умножителя, выход которого подключен к.второму информационному входу мультиплексора, выход 1-го сумматора подключен к второму информационному входу 1-го регистра первой группы и информационному входу 1-го регистра четвертой группы, выход которого подключен к первому информационному входу 1-го мультиплексора второй группы, а выход j-ro регистра четвертой группы подключен к второму информационному входу (j+1)-ro мультиплексора второй

10

J5 73459Ю

группы, выход 1-го мультиплексора второй группы подключен к второму входу 1-го сумматора, второй информационный вход первого мультиплексора второй группы является входом логического нуля устройства, выходом свертки которого является выход М-го регистра первой группы, выход первого блока постоянной памяти подключен к второму входу входного умножителя, первый и второй выходы второго блока постоянной памяти подключены к информационным входам первых регистров соответственно второй и третьей групп, выход третьего блока постоянной памяти подключен к первому входу выходного умножителя, второй вход которого подключен к выходу N-ro регистра первой группы, первый выход дешифратора подключен к первому входу элемента ИЛИ, выход которого подключен к тактовым входам регистров первой группы, второй выход дешифратора подключен к первому входу элемента И, выход которого подключен к входу синхронизации 1-го сумматора, вторые входы элемента И и элемента ИЛИ соединены с управляющим входом 1-го мультиплексора

20

25

второй группы, тактовыми входами 1-х регистров второй и третьей групп, управляющим входом мультиплексора и подключены к первому входу задания режима устройства, выходом дискретного преобразователя Фурье которого является выход выходного умножителя, выход переполнения счетчика подключен к управляющему входу i-го мультиплексора второй группы, информационный выход счетчика подключен к адресным входам первого и третьего и первому адресному входу второго блоков постоянной памяти, второй адресный вход которого является вторым входом задания режима устройства, а выход генератора тактовых импульсов подключен к тактовому входу i-ro регистра четвертой группы.

| Уильяме Ф | |||

| Цифровая интегральная микросхема для фильтрации видеосигналов | |||

| - Электроника, 1983, № 20, с.74-79, рис.4 | |||

| Устройство для цифровой фильтрации | 1984 |

|

SU1196894A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-23—Публикация

1988-02-15—Подача