-4

W,

W

,-

W,

-ie

W,

,-zs

W

-4

Wc

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1988 |

|

SU1545230A1 |

| Устройство для вычисления дискретного преобразования Фурье и свертки | 1988 |

|

SU1573459A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1988 |

|

SU1589289A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| Цифровой фильтр | 1986 |

|

SU1387014A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1211748A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1508233A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1596347A1 |

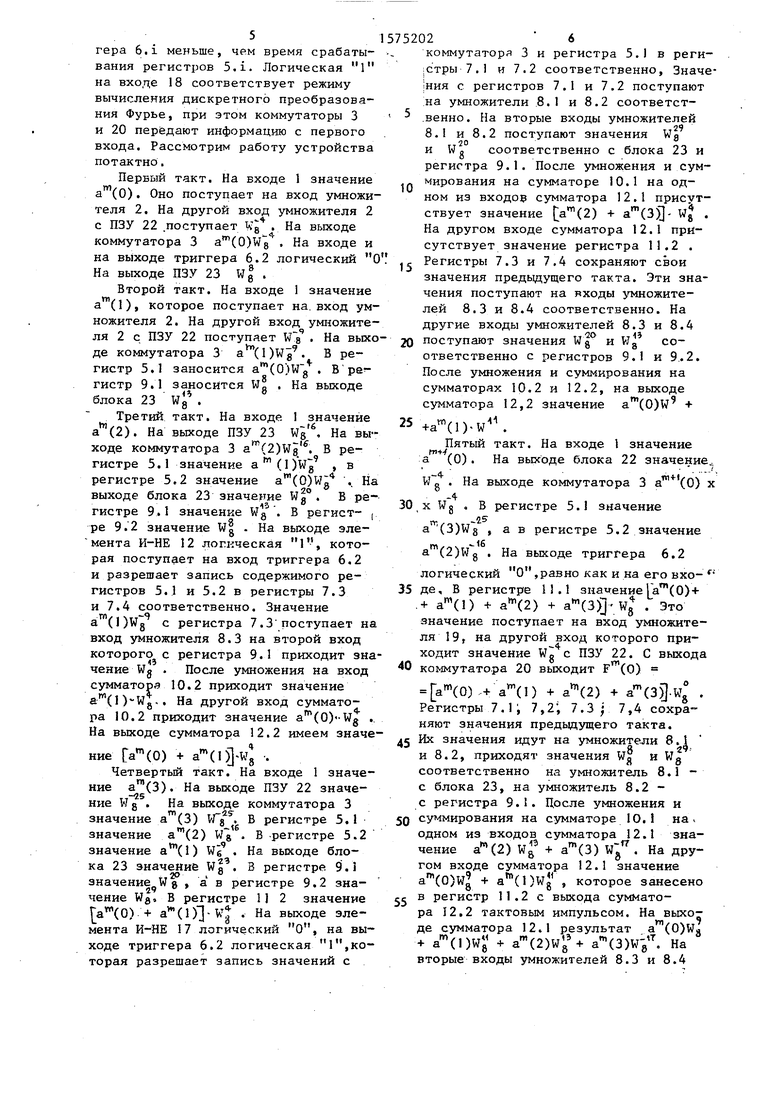

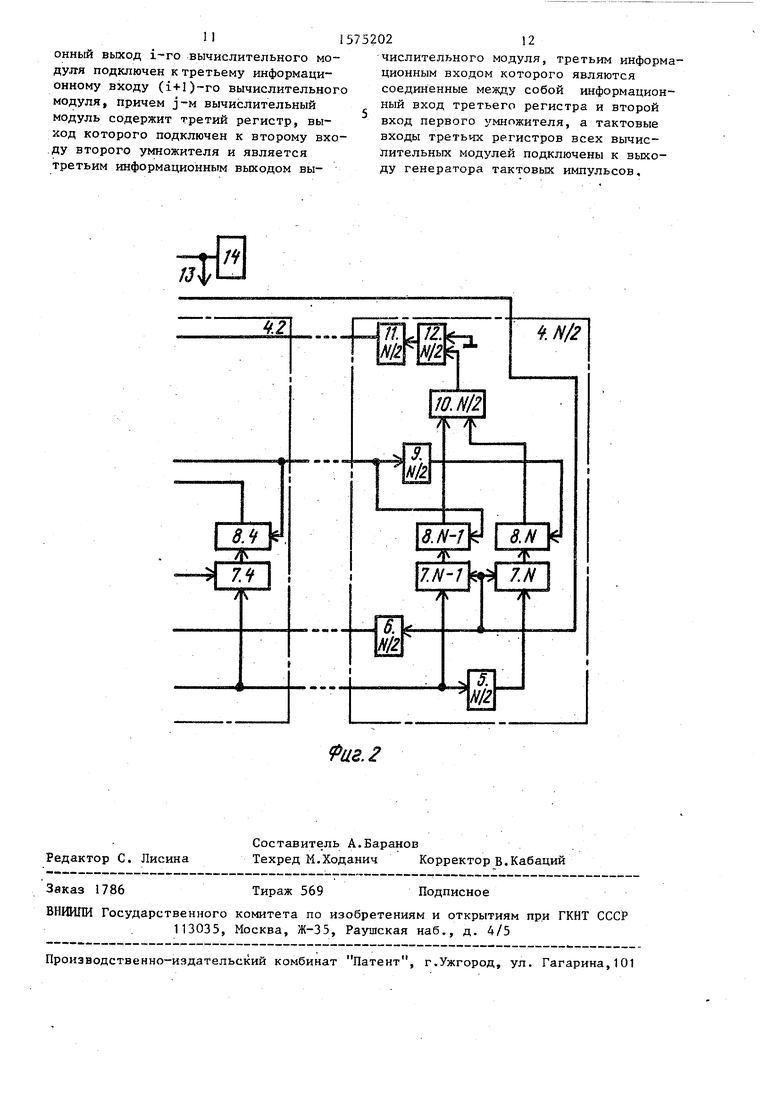

Изобретение относится к вычислительной технике, предназначено для вычисления дискретного преобразования Фурье и цифровой фильтрации и может быть использовано в системах цифровой обработки сигналов. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что в состав устройства входят информационный вход 1, умножитель 2, коммутатор 3, N/2 (где N - размер преобразования) вычислительных модулей 4, каждый из которых содержит регистр 5, триггер 6, два буферных регистра 7, два умножителя 8, регистры 9,11, сумматоры 10 и 12. Кроме того, устройство содержит шину синхронизации, генератор 14 тактовых импульсов, счетчик 15, дешифратор 16, элемент И-НЕ 17, вход 18 задания режима, умножитель 19, коммутатор 20, информационный выход 21 и блоки 22,23 постоянной памяти. 2 ил.

Во второй диагональной и лево- циркулярной матрицах индексы приведены до модулю 8.

Входные отсчеты поступают непрерывным потоком на вход I устройства с частотой тактового генератора 14, с выхода которого поступает последовательность прямоугольных импульсов типа меандр. Полагаем, что счетчик 15, регистры 5.1, 9.1. 11 синхронизиру0

ются положительным перепадом тактовых импульсов. Регистры 7.1 имеют потенциальные синхровходы. Логическая 1 ня синхровходе соответствует передачи информации с входа на выход. При переходе синхросигнала г логической 1 в О регистр переходит в режим хранения. Полагаем время формирования сигнала на выходе элемента 17 и время переключения триггера 6.1 меньше, чем время срабатывания регистров 5.1. Логическая 1 на входе 18 соответствует режиму вычисления дискретного преобразования Фурье, при этом коммутаторы 3 и 20 передают информацию с первого входа. Рассмотрим работу устройства потактно.

Первый такт. На входе 1 значение ат(0). Оно поступает на вход умножителя 2. На другой вход умножителя 2 с ПЗУ 22 .поступает Wjj . На выходе коммутатора 3 am(0)Wg . На входе и на выходе триггера 6.2 логический На выходе ПЗУ 23 Wg .

Второй такт. На входе 1 значение а (1), которое поступает на вход умножителя 2. На другой вход умножите. На выхо-9 -Ч

ля 2 с ПЗУ 22 поступает

де коммутатора 3

В регистр 5.1 заносится atn(0) . В регистр 9.1 заносится Wg . На выходе блока 23 w

tb

8

Третий такт. На входе 1 значение ат(2). На выходе ПЗУ 23 Wg 6. На вырев

ходе коммутатора 3 а гистре 5.1 значение регистре 5,2 значение

№(2)Wg. В

aMcnw;9 .

iw(0)W

т 20

-4 8

На В ревыходе блока 23 значение W8 гистре 9.1 значение W8 . В регист- ре 9.2 значение w| . На выходе эле- мента И-НЕ 12 логическая 1, которая поступает на вход триггера 6.2 и разрешает запись содержимого регистров 5.1 и 5.2 в регистры 7.3 и 7.4 соответственно. Значение

т-

a 0)Wg с регистра 7.3 поступает на вход умножителя 8.3 на второй вход которого с регистра 9.1 приходит значение W

8

После умножения на вход

сумматора 10.2 приходит значение am(l)Wg.. На другой вход сумматора 10.2 приходит значение am(0)-Wg . На выходе сумматора 12.2 имеем значение am(0) + am(l)-Wg .

Четвертый такт. На входе 1 значение а™(3). На выходе ПЗУ 22 значе- На выходе коммутатора 3

ние W g .

значение атл(3) . В регистре 5.1 значение am(2) W . В регистре 5.2

На выходе бло- В регистре 9.J

значение а (1) Wg ка 23 значение Wo

in О

23

2Р

значение Wg , а в регистре 9.2 значение Wg, В регистре 1J 2 значение aw(0) + (I) . На выходе элемента И-НЕ 17 логический О, на выходе триггера 6.2 логическая 1,которая разрешает запись значений с

1575202

0

коммутатора 3 и регистра 5.1 в регистры 7.1 и 7.2 соответственно, Значе- ния с регистров 7.1 и 7.2 поступают на умножители 8.1 и 8.2 соответственно. На вторые входы умножителей 8.1 и 8.2 поступают значения Wfl

20

и Wa соответственно с блока 23 и

о

регистра 9.1. После умножения и суммирования на сумматоре 10.1 на одном из входов сумматора 12.1 присутствует значение am(2) + am(3)- Wg . На другом входе сумматора 12.1 присутствует значение регистра 11.2 . Регистры 7.3 и 7.4 сохраняют свои значения предыдущего такта. Эти значения поступают на входы умножителей 8.3 и 8.4 соответственно. На другие входы умножителей 8.3 и 8.4

,1О

,&

0 поступают значения W8 и Wg соответственно с регистров 9.1 и 9.2. После умножения и суммирования на сумматорах 10.2 и 12.2, на выходе сумматора 12,2 значение am(0)W9 +

25

+aw(l)V1

m-t-f

Пятый такт. На входе 1 значение (0) . На выходе блока 22 значение..

W

-4На выходе коммутатора 3 (0) х

-4

х Wg . В регистре 5.1 значение

-is

a (3)Ws , а в регистре 5.2 значение

m - a (2)Wg . На выходе триггера 6.2

логический О,равно как и на его вхо- г де, В регистре 11.1 значение 1агп(0) +

М -Ъи, - 4- + ат(1) + а№(2) + ам(3

W

8

Это

значение поступает на вход умножителя 19, на другой вход которого приходит значение Wg с ПЗУ 22. С выхода 40 коммутатора 20 выходит F (О)

am(0) + aw(l) + а(2) + am(3)-W& . Регистры 7.1; 7,2, 7.3J 7,4 сохраняют значения предыдущего такта.

5 Их значения идут на умножители 8.5 и 8.2, приходят значения WJj и W8 соответственно на умножитель 8.1 - с блока 23, на умножитель 8.2 - с регистра 9.1. После умножения и

Q суммирования на сумматоре 10.1 на . одном из входов сумматора 12.1 значение а (2) wj9 + am(3) W . На другом входе сумматора 12.1 значение ani(0)w + am(l)wj1 , которое занесено

5

Я

в регистр 11.2 с выхода сумматора 12.2 тактовым импульсом. На выходе сумматора 12.1 результат a (0)Wa

(V) / 1 v . -

a (l)Wg

+ а

(2)WJ4

im(3)W

-IT 8

На

вторые входы умножителей 8.3 и 8.4

wg

поступают значения и Wg, которые находятся в регистрах 9.1 и 9.2 соответственно. После умножения и суммирования на сумматорах 10.2 и 12.2 на выходе сумматора 12.2 рем , . . - .

зультат

am(0)wj6 + am(l)Wg

ния предыдущего такта после умноже ния на умножителях 8.1 и 8.2 и сум мирования на сумматорах 10.1 и 12. причем вторым слагаемым сумматора 12,1

г.т25

Шестой такт. На выходе 1 значение

а™(1). На выходе блока 22 значение Wg На выходе коммутатора 3 а1 х W8 .В регистре 5.1 значение , а в регистре 5.2 значение.

является значение am(0) + + am(l)Wg -регистра 11,2. На выход

a№(0)wf ч-а-(ОС+ am(2)W-83 + ат(3)Г . На

8

сумматора 12.1 результат

1я / 1 т V- Т , ГО / л т ,-

8 + a (2)Wa (1) х ю вых°Де элемента И-НЕ 17 появляется

логическая 1 , которая разрешает запись содержимого регистров 5.1 и 5.2 в регистры 7.3 и 7.4 соответственно. После умножения на умножите- 15 лях 8.3 и 8.4 и суммирования на сум маторах 10,2 и 12.2 на выходе сумма

a 3)Wf,

На выходе блока 23 значе лч

ние W8 . В регистре 9.1 значение W«f f

а в регистре 9.2 - значение Wg В регистре 11.1 значение arT1(0)W8 + + am(l)We + a)(2)Wg3+ am(3)W/, которое подается на вход умножителя 19, на второй вход которого поступает значение с блока 22. На выходе коммутатора 20 результат F (1) (l)w2 + )W +

)W° .

Регистры 7.1; 7.2; 7.3; 7.4 сохраняют свои значения, Дальше происходит аналогичный процесс - в умножителе 8.1 умножается содержимое регистра 7.1 и значение на выходе блока 23, в умножителе 8.2 - значение регистров 7.2 и 9.1 В регистре 11.2 заносится am(0)Wg6 + aft(l)Wg°. После суммирования результатов на сумматорах 10.1 и 12.1 на выходе сумматора 12.1

Г

aw(2)w;8 +

имеем n)(0)Wg6+ am(l)W )1. В умножителе 8.3 умножаются значения регистров 7.3 и 9.1, а в умножителе 8.4 - значения регистров 7,4°и 9.2. После суммирования на сумматорах 10.2 и 12.2 на выходе сумматора 12.2 значение 3(0)Wg + + am(l) .

Седьмой такт. На входе 1 значение

.-16

(2) . На выходе 22 значение W На выходе коммутатора 3 значение

В регистре 5.1 значение

am+ (2)wf

(l)Wj , а в регистре 5.2 значение

ami(0)w;4

На выходе блока 23 значение . В регистре 9.1 значение Wg,

а в регистре 9.2

8

В

значение WQ

У71 46

регистре 11.1 значение a (0)W8 + +a (l) aT(2)w;H aw(3)Wg2, которое поступает на вход умножителя 19, на второй вход которого поступает значение с блока 22. На выходе мутатора 20 результат Fm(2) am(0)W8 + am(l)W64 + am(2)wT+ ani(3)w;z8 . - Регистры 7.1 и 7.2 сохраняют

ния предыдущего такта после умножения на умножителях 8.1 и 8.2 и суммирования на сумматорах 10.1 и 12.1 причем вторым слагаемым сумматора 12,1

г.т25

является значение am(0) + + am(l)Wg -регистра 11,2. На выходе

a№(0)wf + ч-а-(ОС+ am(2)W-83 + ат(3)Г . На

8

сумматора 12.1 результат

1я / 1 т V- Т , ГО / л т ,-

8 + a (2)Wa вых°Де элемента И-НЕ 17 появляется

логическая 1 , которая разрешает запись содержимого регистров 5.1 и 5.2 в регистры 7.3 и 7.4 соответственно. После умножения на умножите- 5 лях 8.3 и 8.4 и суммирования на сумматорах 10,2 и 12.2 на выходе суммато5

0

5

pa 12.2 значение am+l(0)Wg + a

0

т+4

0 W8

Восьмой такт. На входе 1 значение На выходе блока 22 значение . На выходе коммутатора 3 значение

,-25

1(3).

(3)W

ние а

т-м

(2)W,

-Z5 a .

Vie

В регистре 5.1 значезначениё am+l(l)

ка 23

, а в регистре 5.2

g . На выходе блоW

29

В регистре 9. 1

значение п„

10

.значение Wg ,в регистре 9.2 значение W (0)иГ+ aw(l)w; + am(2) +

-Щ,

В регистре m,

a 40JWe + a (l)Wg . „ 4fc/«$

+ a (3)Wg ,которое поступает на умно- 0 житель 19, на второй вход которого поступает значение с ПЗУ 22. Ка выходе коммутатора 20 результат F (3) .- am (0)W8° + arn(l)W-8z6+ am (

hi &

+ a (3)We. На выходе триггера-6.2 5 логическая 1, которая разрешает запись информации с выхода коммутатора и регистра 5.1 в.регистры 7.1 и 7.2 согУ. ответственно. Б регистр 11.1 зако- {

1 т.т4

Ч- /лЧт-Л

сится a (0)W

8

f (l)Wg . После умножения в умножителях 8.1 и 8.2 и суммирования в сумматорах 10.1 и 12.1 на выходе сумматора 12.1

результат а™ (0) + (О +

+ам+1(2)

+ a1™ (3).Wg . Регистры 7.3

и 7.4 сохраняют информацию предыдущего такта. После умножения на умножителях 8.3 и 8.4 и суммирования на сумматорах 10.2 и 11.2 на выхо5

BYV

(0)-UR +

де сумматора 12.2 значение а

f . ..W

+ а (1) Wa .

Девятый такт. Аналогичен пятому. На вход устройства поступают значе- ния 3(0).

Дальнейшая работа устройства продолжается по указанному алгоритму.

При реализации процедуры цифровой фильтрации устройство вычисляет выходные отсчеты фильтра в соответствии с выражением

X(k) Г a(k-n).h(n) (3)

где h(n) - коэффициенты импульсной

характе ристики;

а(п) - отсчеты входного сигнала При работе в режиме цифровой фильтрации на вход 18 поступает логический О, который обеспечивает установку всех триггеров 6.1 в единичное состояние. Этим обеспечивается запись информации в регистры 7.1 в каждом такте. между регистрами 9.1 и вторыми входами умножителей 8.1-разрываются.. На вторые входы умножителей 8.1 поступают значения коэффициентов h(n) . Коммутаторы 3 и 20 передают информацию с вторых входов. С выхода 21 в каждом такте снимается отфильтрованное значение Х(Ю .

Формула изобретени

Устройство для вычисления дискретного преобразования- Фурье, содержащее N/2 (N - размер преобразования) вычислительных модулей, элемент И-НЕ, дешифратор, счетчик и генератор тактовых импульсов, выход которЛго подключен к счетному входу счетчика, информационный выход которого подключен к входу дешифратора, выход которого подключен к первому входу элемента И-НЕ, выход которого подключен к тактовому входу N/2-го вычислительного модуля, первый информационный вход 1-го (1 l,N/2-l) вычислительного модуля подключен к первому информационному выходу (1+1)-го вычислительного модуля, тактовый выход которого подключен к тактовому входу 1-го вычислительного модуля, второй информационный выход которого подключен к второму информационному входу (1+1)-го вычислительного модуля, при этом j-й (, N/2) вычислительный модуль содержит первый и второй регистры, первый и второй сумматоры, первый и второй1 умножители, первый и второй буферные регистры и триггер, выход которого является тактовым выходом вычислительного модуля, первым информационным выходом которого является выход первого регистра, ин10

15

575202 10

формационный вход которого подключен к выходу первого сумматора, первый вход которого подключен к выходу второго сумматора, первый и второй входы

5 которого подключены к выходам соответственно первого и второго умножителей, первые входы которых подключены к выходам соответственно первого и второго буферных регистров, тактовые входы которых соединены с тактовым входом триггера и подключены к тактовому входу вычислительного модуля, вторым информационным входом которого является второй вход первого сумматора, информационный вход первого буферного регистра соединен с информационным входом второго регистра и является вторым информационным вхо20 дом вычислительного модуля, а выход второго регистра подключен к информационному входу второго буферного регистра и является вторым информационным выходом вычислительного модуля,

25 при отом тактовые входы первых и вторых регистров всех вычислительных модулей подключены к выходу генератора тактовых импульсов, отличающееся тем, что, с целью упрощения, оно содержит первый и второй коммутаторы, первый и второй умножи-- тель, первый и второй блоки постоянной памяти, адресные входы которых подключены к информационному выходу счетчика, выход первого блока постоянной памяти подключен к первым входам первого и второго умножителей, выходы которых подключены к первым информационным входам соответственно первого и второго коммутаторов, управляющие входы которых соединены с вторым входом элемента И-НЕ, и является входом задания режима устройства, информационным выходом которого является выход второго коммутатора, второй информационный вход которого соединен с вторым входом второго умножителя и подключен к первому информационному выходу первого вычисли50 тельного модуля, второй информационный вход которого подключен к выходу первого коммутатора, второй информационный вход которого соединен с вто- рым входом первого умножителя и явсс ляется информационным входом устройства, а выход второго блока постоянной памяти подключен к третьему информационному входу первого вычислим- тельного модуля, третий информаци30

35

40

45

онный выход i-го вычислительного модуля подключен к третьему информационному входу (i+l)-ro вычислительного модуля, причем j-м вычислительный модуль содержит третий регистр, выход которого подключен к второму входу второго умножителя и является третьим информационным выходом выФае. 2

Редактор С. Лисина

Составитель А.Баранов

Техред М.Ходанич Корректор В.Кабаций

Заказ 1786

Тираж 569

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

числительного модуля, третьим информационным входом которого являются соединенные между собой информационный вход третьего регистра и второй вход первого умножителя, а тактовые входы третьих регистров всех вычислительных модулей подключены к выходу генератора тактовых импульсов.

Подписное

| Устройство для цифровой фильтрации | 1984 |

|

SU1196894A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1388891A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-05-30—Подача