1

Устройство относится к измерительной технике, в частности к устройствам измерения верности передачи информации в цифровых трактах, и может быть использовано для выделения ошибочных символов из информационных последовательное- тей, поступающих из цифрового тракта на вход измерителей коэффициента ошибок передачи.

Цель изобретения - повышение точности.

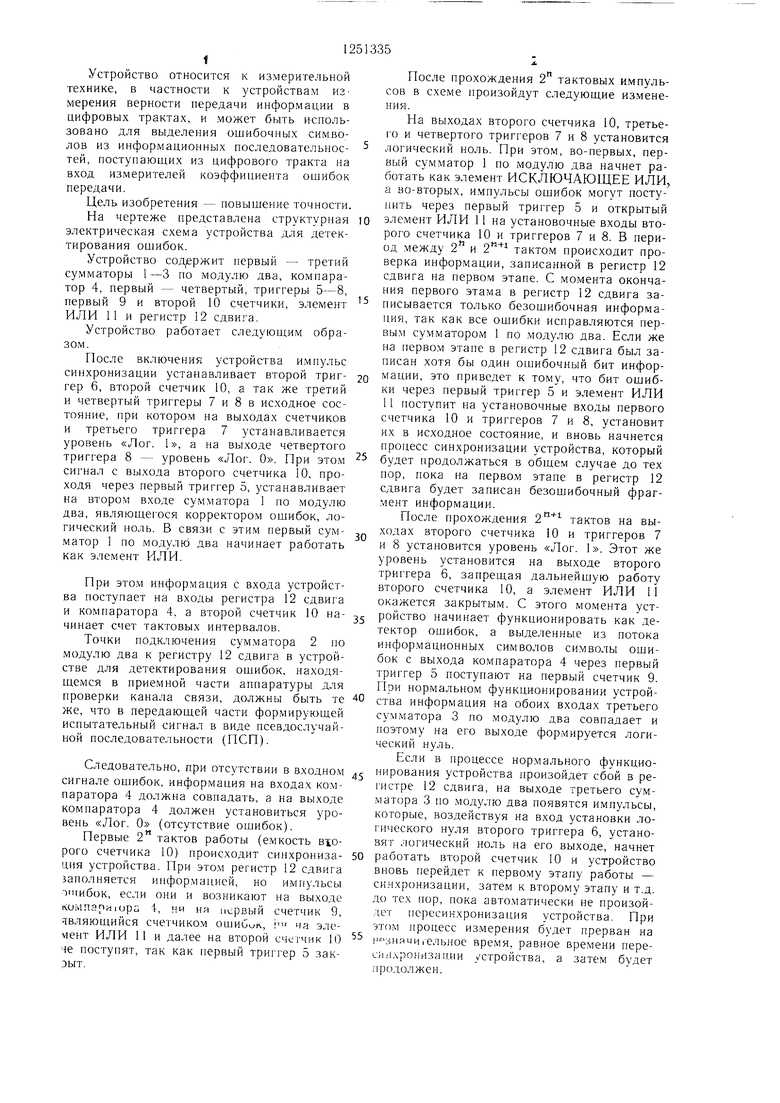

На чертеже представлена структурная электрическая схема устройства для детектирования ошибок.

Устройство содержит первый - третий сумматоры 1-3 по модулю два, компаратор 4, первый - четвертый, триггеры 5-8, первый 9 и второй 10 счетчики, элемент ИЛИ 11 и регистр 12 сдвига.

Устройство работает следующим образом.

После включения устройства и.мпульс синхронизации устанавливает второй триг- гер 6, второй счетчик 10, а так же третий и четвертый триггеры 7 и 8 в исходное состояние, нри котором па выходах счетчиков и третьего триггера 7 устанавливается уровень «Лог. 1, а па выходе четвертого триггера 8 - уровень «Ло1 О. При этом сигнал с выхода второго счетчика 10, проходя через первый триггер 5, устанавливает на втором входе сумматора 1 по модулю два, являющегося корректором ошибок, логический ноль. В связи с этим первый сум- матор 1 по модулю два начинает работать как элемент ИЛИ.

При этом информация с входа устройства поступает па входы регистра 12 сдвига и компаратора 4, а второй счетчик 10 на- чинает счет тактовых интервалов.

Точки подключения сумматора 2 по модулю два к регистру 12 сдвига в устройстве для детектирования ощибок, находящемся в приемной части аппаратурь для проверки канала связи, должны быть те же, что в передающей части формирующей испытательный сигнал в виде псевдослучайной последовательности (ПСП).

Следовательно, при отсутствии в входном сигнале ошибок, информация на входах компаратора 4 должна совпадать, а на выходе компаратора 4 должен установиться уровень «Лог. О (отсутствие ощибок).

Первые 2 тактов работы (емкость BI;O- рого счетчика 10) происходит синхрониза- ция устройства. При это.м регистр 12 сдвига заполняется информацией, но и.мнульсы тчибок, если они и возникают на выходе | импапи Ора 4, ня первый счетчик 9, являющийся счетчико.м ошиоил, на эле- vieHT ИЛИ 11 и далее на второй счетчик К) не поступят, так как первый триггер 5 зак- эыт.

После прохождения 2 тактовых импульсов в схеме произойдут следующие изменения.

На выходах второго счетчика 10, третьего и четвертого триггеров 7 и 8 установится логический ноль. При этом, во-первых, первый сум.матор 1 по модулю два начнет работать как элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, а во-вторых, и.мпульсы ощибок могут поступить через первый триггер 5 и открытый элемент ИЛИ 11 на установочные входы второго счетчика 10 и триггеров 7 и 8. В период между 2 и 2 тактом происходит проверка информации, записанной в регистр 12 сдвига на первом этапе. С момента окончания первого этама в регистр 12 сдвига записывается только безошибочная информация, так как все ощибки исправляются первым сумматором 1 по модулю два. Если же па перво.м этапе в регистр 12 сдвига был за- писап хотя бы один ошибочный бит информации, это приведет к тому, что бит ощибки через первый триггер 5 и элемент ИЛИ 11 поступит на установочные входы первого счетчика 10 и триггеров 7 и 8, установит их в исходное состояние, и вновь начнется процесс синхронизации устройства, который будет нродолжаться в обще.м случае до тех пор, пока на первом этапе в регистр 12 сдвига будет записан безошибочный фрагмент информации.

После прохождения тактов на выходах второго счетчика 10 и триггеров 7 и 8 установится уровень «Лог. 1. Этот же уровень установится на выходе второго триггера 6, запрещая дальнейщую работу второго счетчика 10, а элемент ИЛИ 11 окажется закрытым. С этого момента устройство начинает функционировать как детектор ошибок, а выделенные из потока ипформационных символов символы ошибок с выхода компаратора 4 через первый триггер 5 поступают на первый счетчик 9. При нормальном функционировании устройства информация па обоих входах третьего сумматора 3 по модулю два совпадает и поэтому па его выходе формируется логический нуль.

Если в процессе нормального функционирования устройства произойдет сбой в регистре 12 сдвига, на выходе третьего сумматора 3 но модулю два появятся импульсы, которые, воздействуя на вход установки логического пуля второго триггера 6, установят логический ноль на его выходе, начнет работать второй счетчик 10 и устройство вновь перейдет к первому этапу работы - синхронизации, затем к второму этапу и т.д. до тех пор, пока автоматически не произойдет пересинхронизация устройства. При этом процесс из.мерения будет прерван на .зняии.ельное время, равное времени пере- .ропизации устройства, а затем будет продолжен.

Формула изобретения

Устройство для детектирования ошибок содержащее последовательно соединенные первый сумматор по модулю два, регистр сдвига, второй сумматор по модулю два, компаратор, первый триггер и первый счетчик, при этом первый вход первого сумматора по модулю два соединен с другим входом компаратора и является информационным входом устройства, дополнительный выход регистра сдвига соединен с другим входом второго сумматора по модулю два, отличающееся тем, что, с целью повышения точности, в него введены элемент ИЛИ и последовательно соединенные третий сумматор по модулю два, второй триггер, второй счетчик, третий триггер и четвертый триггер, выход которого подключен к вхо

ду установки логической единицы второго триггера, первый вход третьего сумматора по модулю два соединен с выходом первого сумматора по модулю два, второй вход соединен с выходом второго сумматора по модулю два, а выход является установочным входом устройства, тактовым входом которого является тактовый вход второго счетчика, прямой выход первого триггера подключен к второму входу первого сумматора по модулю два, вход установки логической единицы соединен с выходом второго счетчика, а инверсный выход через элемент ИЛИ соединен с информационным входом второго счетчика, с входом установки логической единицы четвертого триггера и с входом установки логического нуля третьего триггера, выход которого подключен к другому входу элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2279184C2 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Устройство для детектирования ошибок | 1990 |

|

SU1709542A1 |

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1317484A1 |

| Устройство для детектирования ошибок | 1989 |

|

SU1663771A1 |

| Декодирующее устройство | 1980 |

|

SU907846A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2270527C1 |

| Устройство для детектирования ошибок | 1988 |

|

SU1573545A1 |

Изобретение может быть использовано в устройствах измерения верности передачи информации в цифровых трактах. Цель изобретения - повышение точности. Устройство содержит три сумматора 1, 2 и 3 по модулю два (СМД), компаратор 4, четыре триггера (Т) 5, 6, 7 и 8 два счетчика (С) 9 и 10, элемент ИЛИ 11 и регистр Устонобоцный дход сдвига 12. При поступлении информации на вход устройства С 10 начинает счет тактовых интервалов. После прохождения 2 тактов на выходах С 10 и Т 6, 7 и 8 устанавливается логическая единица и устройство начинает функционировать как детектор ошибок. Если произойдет сбой в регистре сдвига 12, то на выходе СМД 3 появятся импульсы, которые, воздействуя на Т 6, установят на его выходе логический ноль. С 10 начнет работать и устройство перейдет к последовательным этапам синхронизации работы до тех пор, пока автоматически не произойдет пересинхронизация устройства. Процесс измерения прерывается на незначительное время, равное времени пересинхронизации устройства, а затем продолжается. Цель достигается введением СМД 3, Т 6, 7 и 8 и С 10. 1 ил. Тактовый Вход (Л ю 01 со ел

| Авторское свидетельство СССР № 760463, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Патент Великобритании № 1431218, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-08-15—Публикация

1985-02-22—Подача