1

(21)4443228/24-24

(22)23,05.88

(46) 30.06.90. Бюл № 24

(71)Харьковский политехнический институт им„ В оИ,Ленина

(72)А,И.Овчаренко,и Л.В.Рябуха (53) 681,325(088.8)

(56) Авторское свидетельство СССР 596941, кл„ G 06 F 7/38, 1973.

Смолов В,Б. Функциональные преобразователи информации, - Л,: Энерго- издат, Ленингр, отд-ние, 1981, рис, 4-1, с„ 134,

(54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ

(57) Изобретение относится к вычислительной технике и может быть использог- вано в качестве специализированных вычислителей автономно или в составе больших ЭВМ в качестве функциональных расширителей арифметики. Целью изобретения является расширение класса решат емых задач за счет возможности возведения в произвольную дробно-рациональную степень с погрешностью, не превышающей половины единицы младшего раз

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления дробно-рациональных функций | 1980 |

|

SU934482A1 |

| Устройство для вычисления значений многомерного полинома | 1990 |

|

SU1742829A1 |

| Устройство для воспроизведения функций | 1981 |

|

SU991435A1 |

| Устройство для возведения в степень и извлечения корня | 1983 |

|

SU1084790A1 |

| Устройство для извлечения корня третьей степени | 1983 |

|

SU1129609A1 |

| Аналого-цифровое вычислительное устройство | 1987 |

|

SU1425725A2 |

| Устройство для вычисления функций | 1985 |

|

SU1287150A1 |

| Логический вычислитель в системе остаточных классов | 2016 |

|

RU2637488C1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1363405A1 |

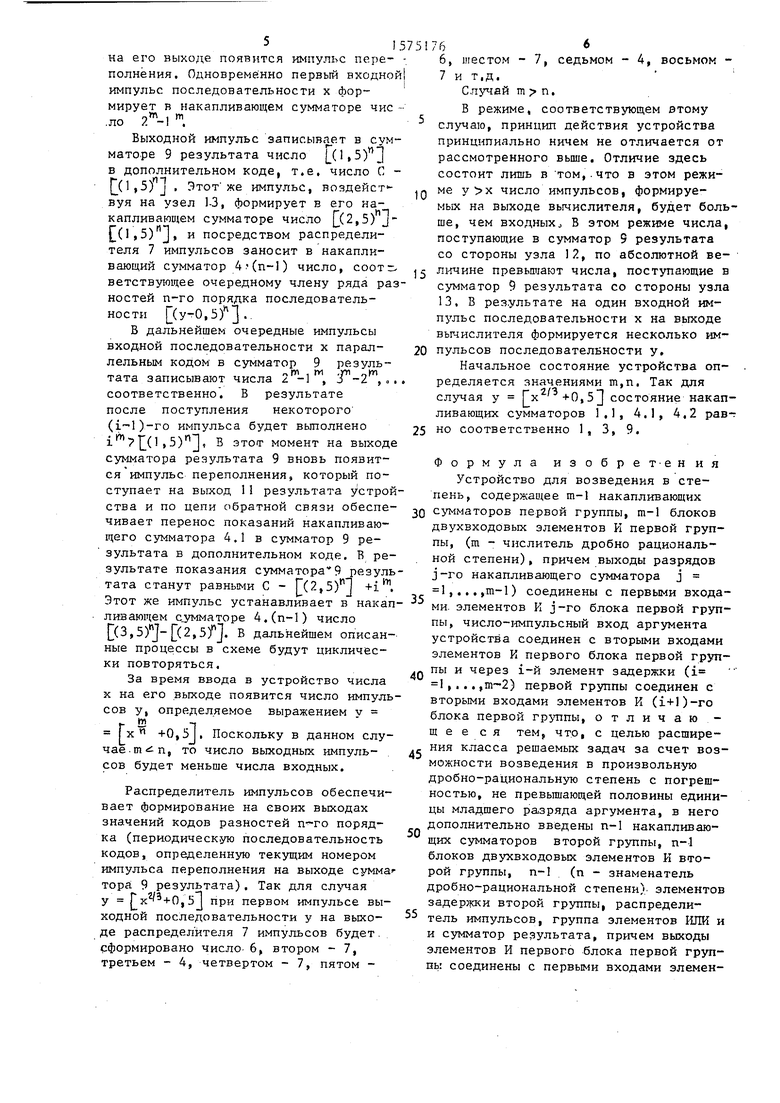

Изобретение относится к вычислительной технике и может быть использовано в качестве специализированных вычислителей автономно или в составе больших ЭВМ в качестве функциональных расширителей арифметики. Целью изобретения является расширение класса решаемых задач за счет возможности возведения в произвольную дробно-рациональную степень с погрешностью, не превышающей половины единицы младшего разряда аргумента. Устройство содержит J накапливающих сумматоров 1 (J=1,...,M-1) (M - числитель дробно-рациональной степени) первой группы, J блоков 2 двухвходовых элементов И первой группы, J элементов задержки 3 (J=1,...,M-2), K накапливающих сумматоров 4 (K = 1, ... ,N-1) (N - знаменатель дробно-рациональной степени) второй группы, K блоков 5 двухвходовых элементов И второй группы, K элементов задержки 6 второй группы, распределитель импульсов 7, группу 8 элементов ИЛИ, сумматор 9 результата, число-импульсный вход 10 аргумента, выход 11 результата, первый 12 и второй 13 узлы формирования разностей первого порядка. 1 ил.

Ю

Р сл

М

о

ряда аргумента„ Устройство содержит j накапливающих сумматоров 1 (j 1,.,..т-) (m - числитель дробно-рациональной степени) первой группы, j блоков 2 двухвхрдовых элементов И первой группы, i элементов задержки 3 (), к накапливающих сумматоров 4 (,.,.,) (п - знаменатель дробно-рациональной степени BTO-JQ

Изобретение относится к вычислительной технике и может быть использовано в качестве специализированных вычислителей автономно или в составе больших ЭВМ в качестве функциональ- ных расширителей арифметики.

Цель изобретения - расширение класса решаемых задач за счет возможности возведения в произвольную дробно-рациональную степень с погрешностью, не превышающей половины единицы младшего разряда аргумента,

На чертеже представлена функциональная схема устройства.

Устройство содержит j накапливаю- щих сумматоров 1 (,,,.,) (m - числитель дробно-рациональной степени) первой группы, j блоков 2 двухрходовых элементов И первой группы, i элементов задержки 3 (,,,.,т-2) К накапливающих сумматоров 4 (, о ,. ,п-) (п знаменатель дробно-рациональной степени) второй группы, К блоков 5 двух входовых элементов И второй группы, К элементов задержки 6 второй группы, распределитель 7 импульсов, группу элементов ИЛИ 8, сумматор

9результата, число-импульсный вход

10аргумента, выход 11 результата первый 12 и второй 13 узлы формирования разностей первого порядка.

Устройство функционирует следующим образом.

Устройство позволяет воспроизводи степенные функции вида у ,5j где m, n r целые положительные числа х 1,2,3, Квадратные скобки означают целую часть числа.

Узлы 12 и 13 предназначены для Лормирования кодов чисел 1 , 2 -1 , 3w-2n;...; и 1.5)4- (0.5)4. (2.5)(l,5)nJ, (3,5)} (2,5) , . , : соответственно,

рой группы.К блоков 5 двухвходовых элементов И второй группы, К элементов эадержки 6 второй группы, распределитель импульсов 7, группу 8 элементов ИЛИ, сумматор 9 результата, числот-им- пульсный вход 10 аргумента, выход 11 результата/;первый 12 и второй 13 узлы формирования разностей первого порядка, 1 ил.

Арифметический ряд разностей п-го порядка числовой последовательности с общим членом Xy-O.S)1 +1, где у 1, 2, 3,.vC| содержит постоянные периодически чередующиеся 2 члена. Так, например, для исходная последовательность py-OjS) 5 +1 имеет следующий вид: 1, 4, 16, 43, 92, 167, 275, 422, 615, 858, 1158, .,,

Для данной последовательности запишем арифметические ряды разносте первого, второго и третьего порядка соответственно:

ДЗ, 12, 27, 49, 75, 108, 147, 193, 243, 300 ..,;

йг9, 15, 22, 26, 33, 39, 46, 50, 57, ,,0;

Д36, 7, 4, 7, 6, 7, 4, 7

Данньй арифметический ряд разностей третьего порядка содержит постояные периодические чередующиеся четыре члена (6, 7, 4, 7), В устройстве посредством распределителя импульсов члены ряда разностей пто порядка последовательности Q(,5)n +1 вводятся выходными импульсами устройства в узел 13,

В процессе воспроизведения устройством функции у Гх™ + 0, целесообразно рассмотреть два режима его работы, которые соответствуют случая т п и т п.

Случай т п,

Исходное состояние основных узлов схемы следующее, В сумматоре 9 результата записано число С-1 (С - емкость сумматора), а в накапливающих сумматорах - числа 1 и J

соответственно. Первый импульс вход ной последовательности х переносит прямой код числа 1 из узла 1 2 в сумматор 9 результата, В результате показания сумматора 9 результата станут равными нулю (С-1+1), а

515

на его выходе появится импульс пере- - полнения. Одновременно первый входной импульс последовательности х формирует в накапливающем сумматоре чис

Ow , m

ло 2 - .

Выходной импульс записывает в сумматоре 9 результата число 0|5)П3 в дополнительном коде, т.е. число С - Г(1,5)п . Этот же импульс, воздейст1- вуя на узел 1-3, формирует в его накапливающем сумматоре число (2,5) j- Ј(1,5), и посредством распределителя 7 импульсов заносит в накапливающий сумматор 4(п-1) число, соотг- ветствующее очередному члену ряда разностей n-го порядка последовательности (у-0,5).

В дальнейшем очередные импульсы входной последовательности х парал-

лельным кодом в сумматор 9 резуль„т , м .гп „сп тата записывают числа -1 , 3 -I ,...

соответственно. В результате после поступления некоторого (i-l)-ro импульса будет выполнено i1 { , 5)п, В этот момент на выходе сумматора результата 9 вновь появится импульс переполнения, который поступает на выход 11 результата устройства и по цепи обратной связи обеспе- чивает перенос показаний накапливающего сумматора 4.1 в сумматор 9 результата в дополнительном коде. В результате показания сумматора 9 результата станут равными С - Г(2,5)П1 +irn. Этот же импульс устанавливает в накап- ливающем сумматоре 4.(п-1) число (3,5)nJ- Ј(2,5)Pj. В дальнейшем описанные процессы в схеме будут циклически повторяться.

За время ввода в устройство числа х на его выходе появится число импульсов у, определяемое выражением у

Г - 1

х +0,51. Поскольку в данном случае , то число выходных импуль- сов будет меньше числа входных.

Распределитель импульсов обеспечивает формирование на своих выходах значений кодов разностей пто порядка (периодическую последовательность кодов, определенную текущим номером импульса переполнения на выходе сумма тора 9 результата). Так для случая у Гх + О,) при первом импульсе выходной последовательности у на выхо- де распределителя 7 импульсов будет сформировано число 6, втором - 7, третьем - 4, четвертом - 7, пятом

5

-

- -

0

5 « 5

5

0

5

h6

6, шестом - 7, седьмом - 4, восьмом 7 и т.д.

Случай m п.

В режиме, соответствующем этому случаю, принцип действия устройства принципиально ничем не отличается от рассмотренного выше. Отличие здесь состоит лишь в том, что в этом режиме число импульсов, формируемых на выходе вычислителя, будет больше, чем входныхj В этом режиме числа, поступающие в сумматор 9 результата со стороны узла 12, по абсолютной величине превышают числа, поступающие в сумматор 9 результата со стороны узла 13, В результате на один входной импульс последовательности х на выходе вычислителя формируется несколько импульсов последовательности у.

Начальное состояние устройства определяется значениями т,п. Так для случая у Гх +0,5 состояние накапливающих сумматоров 1.1, 4.1, 4,2 равно соответственно 1, 3, 9.

Формула изобретения

Устройство для возведения в степень, содержащее т-1 накапливающих сумматоров первой группы, т-1 блоков двухвходовых элементов К первой группы, (т - числитель дробно рациональной степени), причем выходы разрядов j-го накапливающего сумматора j 1,...,m-l) соединены с первыми входами элементов К j-го блока первой группы, число-импульсный вход аргумента устройства соединен с вторыми входами элементов К первого блока первой группы и через i-й элемент задержки (i l,...,m-2) первой группы соединен с вторыми входами элементов К (i+l)-ro блока первой группы, отличаю - щ е е с я тем, что, с целью расширения класса решаемых задач за счет возможности возведения в произвольную дробно-рациональную степень с погрешностью, не превышающей половины единицы младшего разряда аргумента, в него дополнительно введены п-1 накапливающих сумматоров второй группы, п-1 блоков двухвходовых элементов И второй группы, п-1 (п - знаменатель дробно-рациональной степени) элементов задержки второй группы, распределитель импульсов, группа элементов ИЛИ и и сумматор результата, причем выходы элементов И первого блока первой группы соединены с первыми входами элементов ШШьРруппы, выходы которых соеди- нены с информационными входами сумматора результата, выход переполнения которого соединен с входом запуска распределителя импульсов и череэ k-й элемент задержки второй группы (k «1,..,п-1) соединен с первыми входами элементов И блока второй группы вторые входы которых соединены с выл

Составитель С.Куликов Редактор Н.Киштулинец Техред Л.С.ердюкова Корректор С.Шекмар

Заказ 1785

Тираж 564

ВЕШИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент ., г.Ужгород, ул. Гагарина, 101

ходами разрядов k-ro накапливающего сумматора второй группы, а выходы элементов И 1-го (1«2,.,,, блока второй группы соединены с информационными входами (1-1)-го накапливающего сумматора второй группы, выходы элементов И первого блока второй группы соединены с вторыми вход-ами элементов ИЛИ группы.

Подписное

Авторы

Даты

1990-06-30—Публикация

1988-05-23—Подача