Изобретение относится к радиотехнике и может использоваться для получения изменяющейся по произвольному закону частоты выходного сигнала, в том числе и по псевдослучайному, для измерения частоты Доплера в радиолокации и гидролокации, адаптивных широкополосных системах связи, для формирования тестовых и маскирующих сигналов в аудиометрах.

Известны синтезаторы изменяющейся частоты, содержащие датчик кода длительности сигнала, первый делитель частоты с переменным коэффициентом деления, датчик кода диапазона частот, первый делитель частоты с дробно-переменным коэффициентом деления, датчик кода начальной частоты, реверсивный счетчик, второй делитель частоты с дробно-переменным коэффициентом деления, счетчик приращения фазы, вычислитель амплитуд, цифро-аналоговый преобразователь, задающий генератор, второй делитель частоты с переменным коэффициентом деления, счетчик, блок памяти и датчик адреса функции [1, 2].

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор изменяющейся частоты, содержащий датчик кода длительности сигнала, датчик адреса функции, датчик кода диапазона частот, датчик кода начальной частоты, блок памяти, перемножитель, делитель частоты с переменным коэффициентом деления, накапливающий сумматор, сумматор, генератор тактовых импульсов, блок вычисления фазы, вычислитель амплитуды и цифро-аналоговый преобразователь [3].

Однако недостатком таких синтезаторов является невозможность формирования произвольного закона изменения частоты сигнала, в том числе скачкообразного и псевдослучайного.

Цель изобретения - формирование произвольных законов изменения частоты не только монотонных, но и скачкообразных, в том числе и псевдослучайных.

Поставленная цель достигается тем, что в цифровой синтезатор изменяющейся частоты, содержащий последовательно соединенные датчик кода диапазона частот, перемножитель, сумматор, блок вычисления фазы, блок вычисления амплитуды, цифро-аналоговый преобразователь и фильтр нижних частот, а также последовательно соединенные датчик адреса периодической функции и блок вычисления периодической функции, последовательно соединенные датчик кода длительности сигнала и делитель с переменным коэффициентом деления, выход которого соединен с тактовым входом блока вычисления периодической функции, датчик кода начальной частоты, выход которого соединен со вторым входом сумматора, и генератор тактовых импульсов, выход которого соединен с тактовыми входами делителя с переменным коэффициентом деления и блока вычисления фазы, дополнительно введены последовательно соединенные датчик длины псевдослучайной последовательности и блок формирования псевдослучайной последовательности и коммутатор, выход которого соединен со вторым входом перемножителя, а второй вход коммутатора соединен с выходом блока вычисления периодической функции и тактовый вход блока формирования случайной последовательности соединен с выходом делителя с переменным коэффициентом деления.

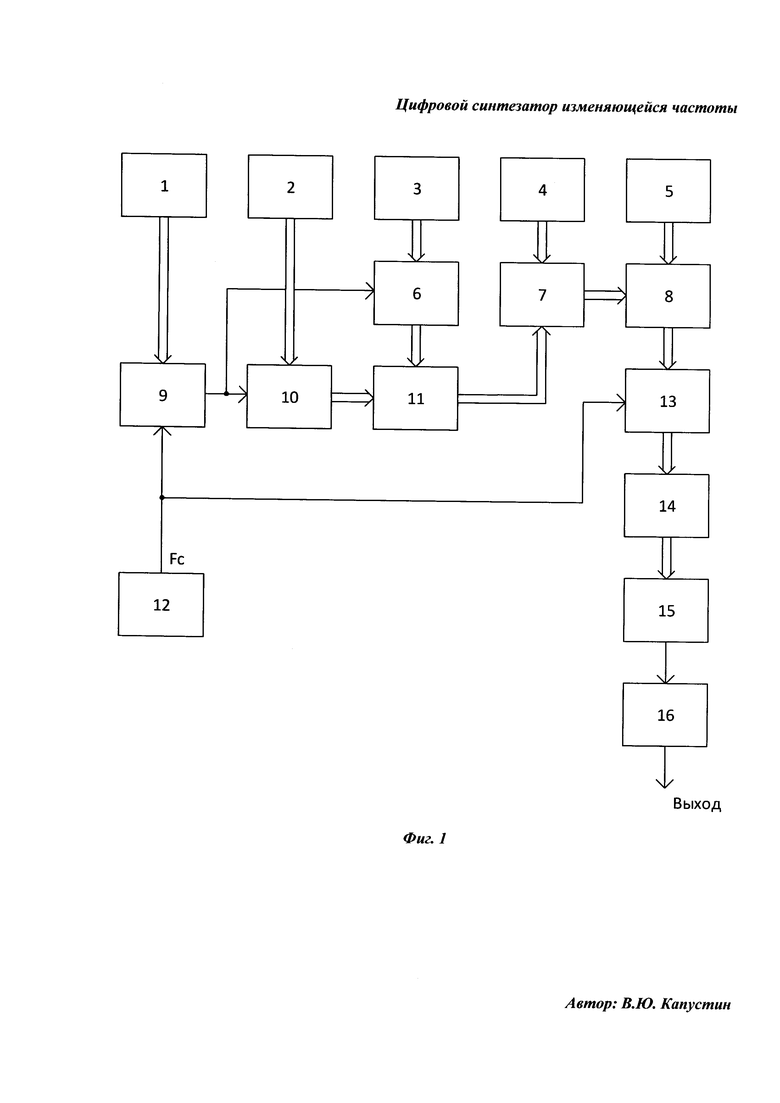

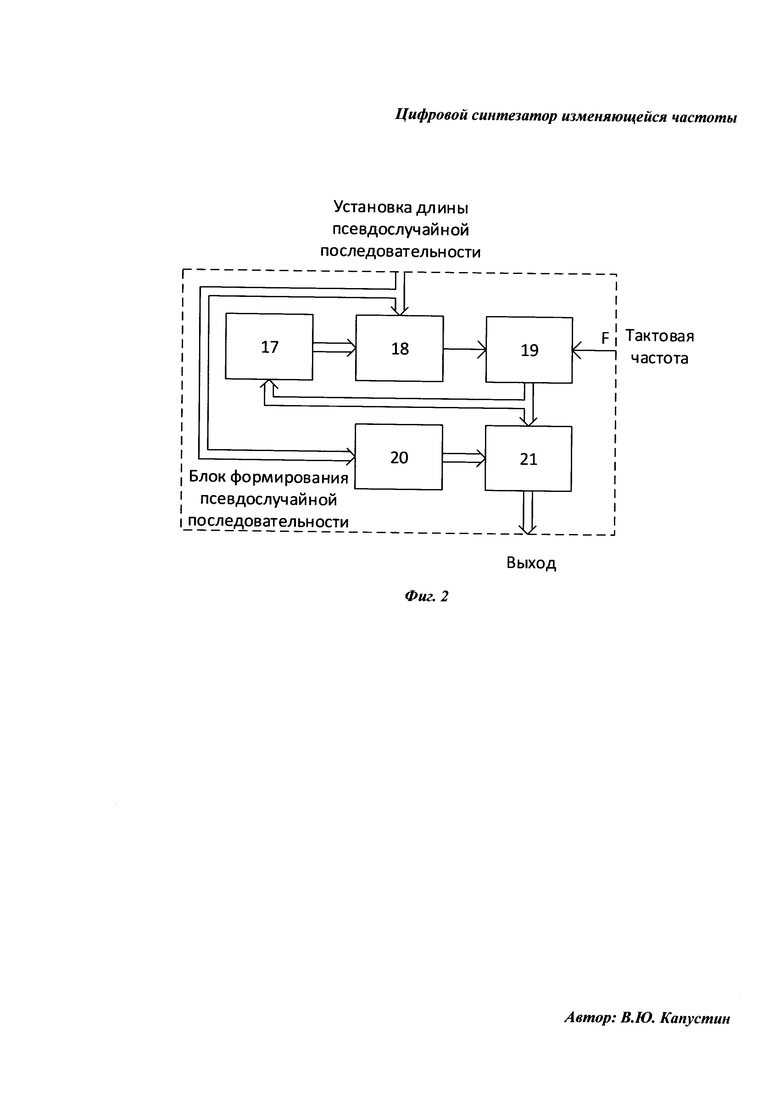

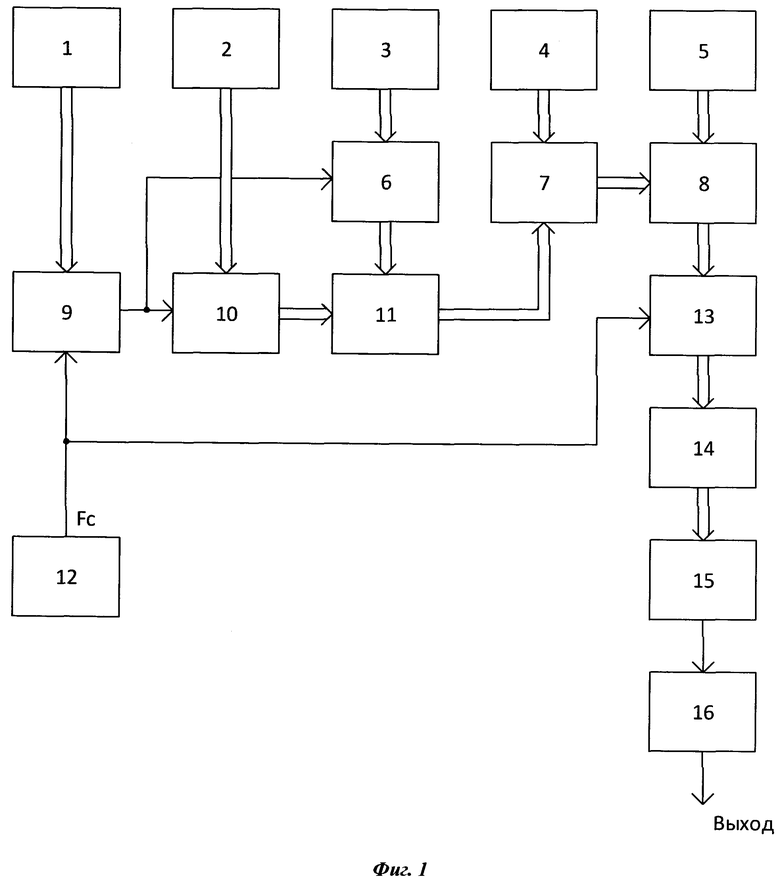

На Фиг. 1 приведена структурная схема цифрового синтезатора частот изменяющейся частоты. На Фиг. 2 приведена структурная схема блока формирования псевдослучайной последовательности.

Цифровой синтезатор изменяющейся частоты содержит последовательно соединенные датчик адреса периодической функции 2, блок вычисления периодической функции 10, коммутатор 11, перемножитель 7, сумматор 8, блок вычисления фазы 13, блок вычисления амплитуды 14, цифро-аналоговый преобразователь 15 и фильтр нижних частот 16, а также последовательно соединенные датчик длины псевдослучайной последовательности 3 и блок формирования случайной последовательности 6, выход которого соединен со вторым входом коммутатора 11, последовательно соединенные датчик кода длительности сигнала 1 и делитель с переменным коэффициентом деления 9, выход которого соединен с тактовыми входами блока вычисления периодической функции 10 и блока формирования псевдослучайной последовательности 6, датчик кода диапазона частот 4, выход которого соединен со вторым входом перемножителя 7, датчик кода начальной частоты 5, выход которого соединен с вторым входом сумматора 8, и генератор тактовых импульсов 12, выход которого соединен с тактовыми входами делителя с переменным коэффициентом деления 9 и блока вычисления фазы 13.

Цифровой синтезатор изменяющейся частоты работает следующим образом.

С помощью датчиков 1-5 устанавливают необходимые значения длительности сигнала Тс, адреса требуемой функции изменения частоты или длины формируемой М-последовательности, диапазона D изменения частоты и начальной частоты F0. В зависимости от того, какой выбран закон изменения частоты, регулярный или псевдослучайный, на вход перемножителя 8 через коммутатор 11 будет поступать код qi закона изменения частоты либо с выхода блока вычисления периодической функции 10, либо с выхода блока формирования псевдослучайной последовательности 6. По каждому импульсу с выхода делителя с переменным коэффициентом деления 9 на вход перемножителя 7 будет поступать новое значение кода qi изменения частоты. Делитель с переменным коэффициентом деления 9 обеспечивает отработку необходимой длительности закона изменения частоты Тч=К·Тмин.

Отработка необходимого диапазона D изменения частоты обеспечивается перемножителем 8, в котором код qi умножается на величину D и далее полученный код суммируется сумматором 8 с кодом начальной частоты F0. Полученный код Q поступает на вход блока вычисления фазы 13, т.е.

Q=F0+D·qi.

Блок вычисления фазы 13 и блок вычисления амплитуды 14 обеспечивают формирование выходной синусоидальной функции с частотой, определяемой выражением:

Fвых=Fc·Q/2n=(F0+D·qi) ·Fc/2n,

и при условии, что Fc численно равна 2n, имеем Fвых, численно равную Q.

Таким образом величина Q полностью определяет значение выходной частоты. При установленном диапазоне изменения частот, равном нулю, частота выходного сигнала будет фиксированной и равной значению кода F0, т.е. на выходе мы получим тональный сигнал. Если в качестве периодической функции изменения частоты будет использована какая-либо монотонная возрастающая функция, например линейная, то частоты выходного сигнала будет меняться от значения F0 до F0+D и, наоборот, если будет использована монотонная ниспадающая функция, то частота выходного сигнала будет изменяться от величины F0-D до F0. При использовании в качестве периодической функции изменения частоты знакопеременной функции, например синусоидальной, частота выходного сигнала будет колебаться от значения F0-D до значения F0+D.

Таким образом видно, что величина F0 в зависимости от используемой функции изменения частоты может быть значением начальной частоты, конечной частоты и средней частоты. Точно также, при использовании в качестве функции изменения выходной частоты псевдослучайной М-последовательности можно получить в качестве выходного сигнала узкополосный шум с центральной частотой F0 полосой от F0-D до F0+D и при фиксированном знаковом разряде, плюсовом или минусовом, получим соответственно полосовой шум в диапазоне от F0 до F0+D или от F0-D до F0.

В качестве блока вычисления периодической функции может быть использовано постоянное запоминающее устройство, в которое заранее прошиты значения используемой функции изменения частоты или любое другое вычислительное устройство, например микропроцессор, который обеспечивает вычисления функции изменения частоты по заранее определенному алгоритму. Блок формирования псевдослучайной последовательности 6 может представлять собой обычный генератор М-последовательности, один из вариантов реализации которого представлен на фиг. 2.

Такой генератор состоит из сдвигающего регистра 19 с блоком сумматоров 17 по модулю два и коммутатором 18 в цепи обратной связи. Длина М-последовательности и соответственно разрядность сдвигающего регистра 19 определяются выходным кодом датчика длины псевдослучайной последовательности. Этот код обеспечивает подключение необходимых выходов блока сумматоров 17 по модулю два с помощью коммутатора 18 к последовательному входу регистра сдвига 19. Этот же код одновременно поступает на вход преобразователя кодов 20, который преобразует входной двоичный код в выходной позиционный, в результате на его младших разрядах появятся разрешающие сигналы. Количество разрядов разрешающих сигналов соответствует разрядности регистра сдвига 19. Эти сигналы пропускают через второй коммутатор 21 на выход блока формирования псевдослучайной последовательности только те разряды регистра сдвига 19, которые участвуют в формировании псевдослучайной последовательности.

Реализован блок формирования псевдослучайной последовательности 6 может быть также с использованием микропроцессора. Перемножитель 7 представляет собой устройство умножения кода без знака, поступающего с датчика кода диапазона частот 4, на код со знаком, поступающий с выхода коммутатора 11. В качестве сумматора 8 используется обычный двоичный сумматор кодов со знаками. Блок вычисления фазы 13 представляет собой накопительный сумматор. В качестве блока вычисления амплитуды 14 может быть использовано постоянное запоминающее устройство, в которое заранее занесены значения выходного сигнала, например синусоидального сигнала, либо любое вычислительное устройство, например на основе микропроцессора. При выборе достаточно мощного и быстродействующего микропроцессора цифровой синтезатор изменяющейся частоты может быть весь реализован на его основе.

Таким образом, предлагаемый цифровой синтезатор изменяющейся частоты обеспечивает формирование произвольных законов изменения частоты, в том числе скачкообразных и псевдослучайных, с изменяемыми длительностью периода повторения и диапазоном изменения частоты.

Литература

1. Авторское свидетельство СССР №1197044, кл. Н03В 23/00, 1985. Цифровой синтезатор изменяющейся частоты. В.С. Григорьев, В.Ю. Капустин, П.А. Гадяцкий и С.В. Попов.

2. Авторское свидетельство СССР №1298836, кл. Н03В 29/00, 1987. Цифровой синтезатор изменяющейся частоты. В.Ю. Капустин, В.С. Григорьев, С.В. Попов и Л.В. Иволга.

3. Авторское свидетельство СССР №1578800, кл. Н03В 23/00, 1990. Цифровой синтезатор изменяющейся частоты. В.Ю. Капустин, В.С. Григорьев и О.Л. Лапаухова.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2021 |

|

RU2765264C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2023 |

|

RU2809550C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2022 |

|

RU2792012C1 |

| АУДИОМЕТР | 2022 |

|

RU2791159C1 |

| ИМИТАТОР УШНОГО ШУМА | 2022 |

|

RU2815507C1 |

| АУДИОМЕТР | 2023 |

|

RU2809013C1 |

| ДВУХКАНАЛЬНЫЙ АУДИОМЕТР | 2024 |

|

RU2835841C1 |

| АВТОМАТИЧЕСКИЙ АУДИОМЕТР | 2024 |

|

RU2840436C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ШУМОВЫХ СИГНАЛОВ | 2015 |

|

RU2586006C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

Изобретение относится к радиотехнике и может использоваться для получения изменяющейся по произвольному закону частоты выходного сигнала, в том числе и по псевдослучайному, и может использоваться для измерения частоты Доплера в радиолокации и гидролокации, для формирования тестовых и маскирующих сигналов в аудиометрии. Цифровой синтезатор изменяющейся частоты содержит последовательно соединенные датчик адреса периодической функции 2, блок вычисления периодической функции 10, коммутатор 11, перемножитель 7, сумматор 8, блок вычисления фазы 13, блок вычисления амплитуды 14, цифро-аналоговый преобразователь 15 и фильтр нижних частот 16, а также последовательно соединенные датчик длины псевдослучайной последовательности 3 и блок формирования псевдослучайной последовательности 6, выход которого соединен с вторым входом коммутатора 11, последовательно соединенные датчик кода длительности сигнала 1 и делитель с переменным коэффициентом деления 9, выход которого соединен с тактовыми входами блока вычисления периодической функции 10 и блока формирования случайной последовательности 6, датчик кода диапазона частот 4, выход которого соединен с вторым входом перемножителя 7, датчик кода начальной частоты 5, выход которого соединен с вторым входом сумматора 8, и генератор тактовых импульсов 12, выход которого соединен с тактовыми входами делителя с переменным коэффициентом деления 9 и блока вычисления фазы 13. Достигаемый технический результат - обеспечение возможности синтеза сигнала с устанавливаемыми длительностью, диапазоном, начальной (центральной) частотой и произвольным законом частотной модуляции, в том числе и псевдослучайным. 2 ил.

Цифровой синтезатор изменяющейся частоты, содержащий последовательно соединенные датчик кода диапазона частот, перемножитель, сумматор, блок вычисления фазы, блок вычисления амплитуды, цифро-аналоговый преобразователь и фильтр нижних частот, а также последовательно соединенные датчик адреса периодической функции и блок вычисления периодической функции, последовательно соединенные датчик кода длительности сигнала и делитель с переменным коэффициентом деления, выход которого соединен с тактовым входом блока вычисления периодической функции, датчик кода начальной частоты, выход которого соединен с вторым входом сумматора, и генератор тактовых импульсов, выход которого соединен с тактовыми входами делителя с переменным коэффициентом деления и блока вычисления фазы, отличающийся тем, что с целью формирования произвольных законов изменения частоты выходного сигнала, в том числе и псевдослучайных, введены последовательно соединенные датчик длины псевдослучайной последовательности и блок формирования случайной последовательности и коммутатор, выход которого соединен со вторым входом перемножителя, а второй вход коммутатора соединен с выходом блока вычисления периодической функции и тактовый вход блока формирования случайной последовательности соединен с выходом делителя с переменным коэффициентом деления.

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1578800A1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Цифровой синтезатор частоты | 1988 |

|

SU1584065A1 |

| Приспособление к шелкомотальному станку для автоматического регулирования толщины наматываемой нити | 1929 |

|

SU18215A1 |

| US 8120389 B2 21.02.2012 | |||

| US 4410954 A1 18.10.1983. | |||

Авторы

Даты

2016-09-20—Публикация

2015-05-27—Подача