Изобретение относится к импульсной технике, может быть использовано в автоматических устройствах и устройствах синтеза сигналов дискретизации и является усовершенствованием формирователя по авт.св. № 1198744.

Целью изобретения является повышение точности формирования временного интервала.

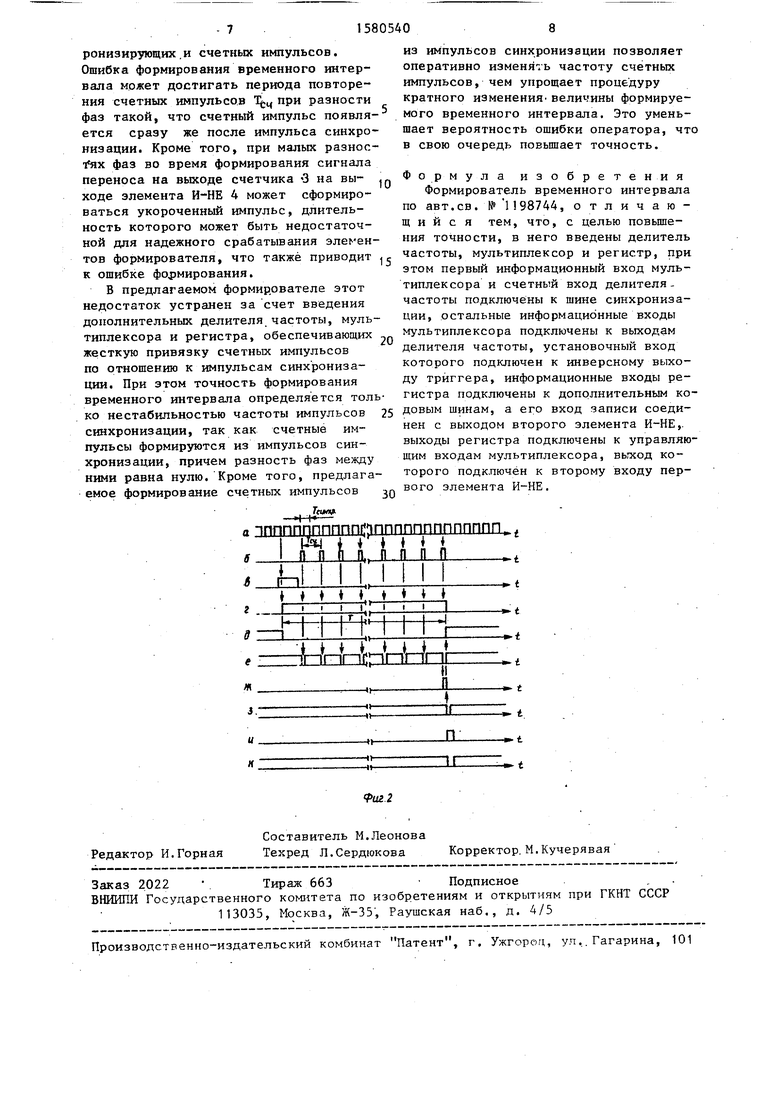

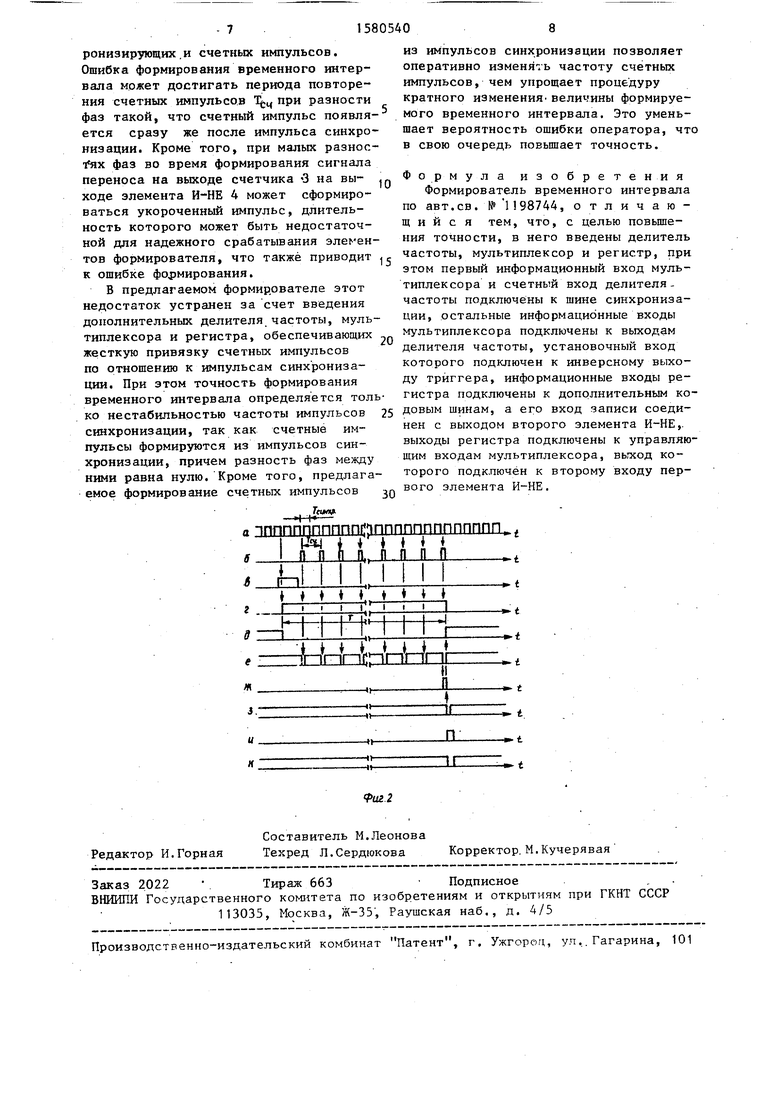

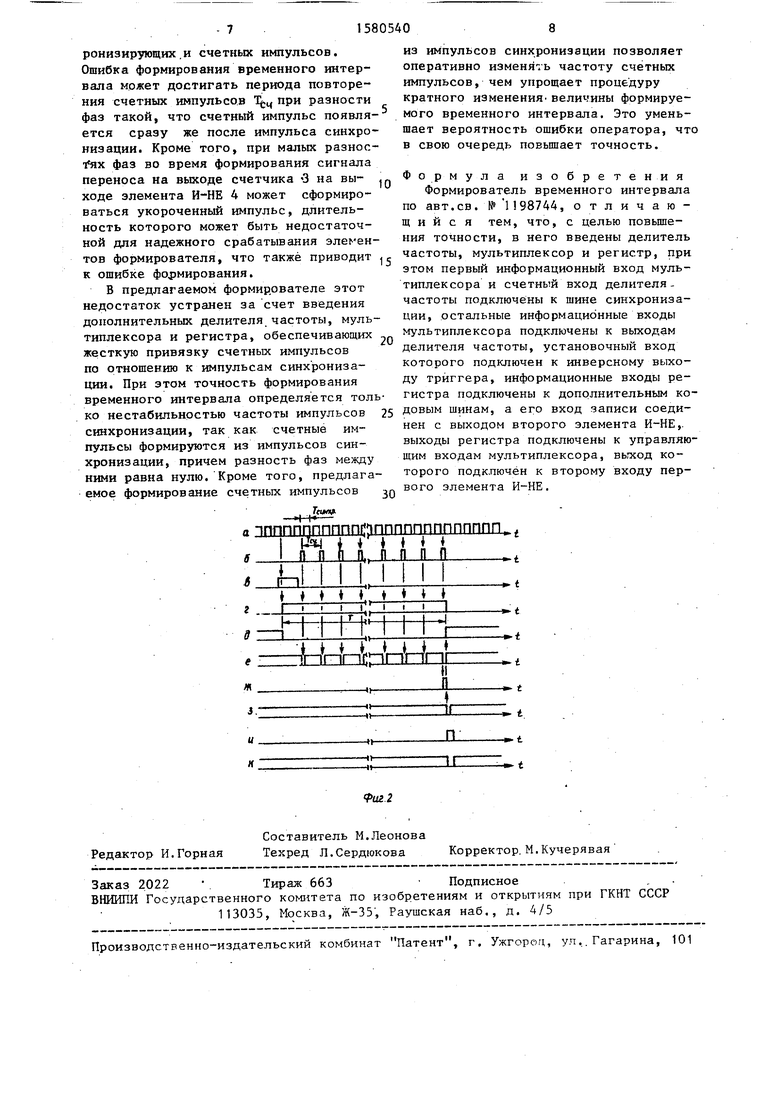

На фиг.1 приведена структурная схема предлагаемого формирователя; на фиг.2 - временные диаграммы работы формирователя.

синхронизации. Прямой и инверсный выходы формирователя 5 подключены к выходным шинам 6.

Формирователь работает следующим образом.

В исходном состоянии триггер 1 находится в нулевом положении (фиг.2.г, д). Б счетчик 3 записан двоичный код, соответствующий формируемому временному интервалу. На выходе переноса счетчика 3 присутствует логический О (фиг.2,ж).Б регистр 14 записан двоичный код, определяющий частоту счет

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство коррекции шкалы времени | 1988 |

|

SU1525932A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Преобразователь двоичного кода во временной интервал | 1987 |

|

SU1453597A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Формирователь длительности импульсов | 1984 |

|

SU1213525A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

Изобретение может быть использовано в автоматических устройствах и устройствах синтеза сигналов дискретизации. Цель - повышение точности формирования временного интервала. Цель достигается введением в формирователь делителя 12 частоты, мультиплексора 13 и регистра 14. Формирователь содержит также IK-триггер 1 с установочным входом R, элементы И - НЕ 2 и 4, счетчик 3, формирователь 5 импульсов, выходные шины 6 и 7, шину 8 синхронизации, шину 9 управления, шину 10 счетных импульсов и основные кодовые шины 11. 2 ил.

Формирователь временного интервала ., ных импульсов. Пусть, например, в ре(фиг.1) содержит 1К триггер 1 с установочным входом R, первый элемент И-НЕ 2, счетчик 3, второй элемент И-НЕ 4, формирователь 5 импульсов,первые 6 и вторые 7 выходные шины, шины синхронизации 8, управления 9, счетных импульсов 10 и основные кодовые II, делитель 12 частоты, мультиплексор 13} регистр 14, дополнительные кодовые

20

гистр 14 записан двоичный код числа 1. Этот код с выходов регистра 14 поступает на управляющие входы А1-АМ мультиплексора 13. При этом последний пропускает на выход сигнал, поступающий на его второй информационный вход Х2, т.е. сигнал с первого выхода делителя 12.

В исходном состоянии логическая 1

шины 15, подключенные к блоку 16 фор- 25 c инверсного выхода триггера 1

мирования кода. Вход I 1К-триггера 1 подключен к шине 9 управления. Счетный вход С триггера 1, соединенный с. первым информационным входом мультиплексора 13 и со счетным входом делителя 12, подключен к шине 8 синхронизации. Прямой и инверсный выходы триггера 1 подключены к выходным шинам 7, при этом прямой выход соединен с первым входом элемента И-НЕ 2,. а

30

(фиг.2,д) поступает на установочный вход R делителя 12, который при этом находится в нулевом состоянии. На прямом и инверсном выходах формирователя 5 присутствуют соответственно логический О и логическая 1 (фиг. 2,и,к

На шину 9 управления соединенную с I-входом триггера 1, подается импульс, длительность которого больше периода

f повторения (ТсиНхр) импульсов синхроинверсный выход подключен к установоч- низации на шине 8. На К-вход тригге- ному входу R делителя 12. Второй ра 1 подан логический О. На шину 8

вход элемента И-НЕ 2 подключен к выходу мультиплексора 13, образующему шину 10 счетных импульсов. Информационные входы X2-XL мультиплексора 13 соединены с соответствующими выходами делителя 12, Управляющие входы Al-AM мультиплексора подключены к выходам

регистра 14, информационные входы ко- , ность которого определяет длительторого подключены к дополнительным кодовым шинам 15, соединенным, например, с выходами блока 16 формирования кода. Выход элемента И-НЕ 2 подключен к счетному входу -} счетчика 3, инность формируемого временного интервала. Логический О с инверсного выхода триггера 1 поступает на R-вход делителя 12, разрешая изменение его состояния. Срабатывание делителя 12

формационные входы предварительной за- происходит по фронту импульсов синхписи которого подключены к основным кодовым шинам 11. Выход переноса счетчика 3 через элемент И-НЕ 4 подключен к входу формирователя 5, входу предварительной записи С счетчика Зэ 55 установочному входу R триггера 1 и входу записи регистра 14. Второй вход элемента И-НЕ 4 подключен к шине 8

гистр 14 записан двоичный код числа 1. Этот код с выходов регистра 14 поступает на управляющие входы А1-АМ мультиплексора 13. При этом последний пропускает на выход сигнал, поступающий на его второй информационный вход Х2, т.е. сигнал с первого выхода делителя 12.

В исходном состоянии логическая 1

c инверсного выхода триггера 1

(фиг.2,д) поступает на установочный вход R делителя 12, который при этом находится в нулевом состоянии. На прямом и инверсном выходах формирователя 5 присутствуют соответственно логический О и логическая 1 (фиг. 2,и,к),

поступают импульсы синхронизации (фиг.2,а). По фронту первого же импульса синхронизации, поступающего после подачи импульса на шину 9 управления, триггер 1 переходит в единичное состояние (фиг.2,г,д), и на шинах 7 начинается - формирование сигнала, длительность формируемого временного интервала. Логический О с инверсного выхода триггера 1 поступает на R-вход делителя 12, разрешая изменение его состояния. Срабатывание делителя 12

происходит по фронту импульсов синхронизации, что обеспечивает синхронность импульсов на выходе делителя 12 с импульсами синхронизации. На первом выходе делителя 12 формируются импульсы с частотой в два раза ниже частоты импульсов синхронизации, на втором - в четыре раза ниже, на третьем - в восемь раз ниже, и т,д. В рассматриваемом случае импульсы с первого выхода делителя 12 с периодом повторения Тсч 2Тсии р через мультиплексор 13 поступают на шину 10 счетных импульсов, т.е. на второй вход элемента И-НЕ 2 (фиг.2,б).

Логическая 1 с прямого выхода триггера 1 подается на первый вход элемента И-НЕ 2. При этом импульсы с шины 10 проходят через элемент И-НЕ 2 на счетный вход вычитания -J счетчика 3 (фиг.2,е). При воздействии импульсов на счетном входе код, записанный в счетчик 3, начинает считы- ,5 ности, задержанные относительно фрон- ваться. Как только счетчик 3 обнуляет- та импульсов на шинах 7 на величину Т.

ся, на его выходе переноса

0 появляется логическая 1 (фиг.2,ж),которая поступает на первый вход элемента И-НЕ 4. На второй вход элемента И-НЕ 4 поступают инверсные импульсы синхронизации (фиг.2,а)у, По окончании импульса синхронизации, приведшего к обнулению счетчика 3, на выходе элемента И-НЕ 4 появляется логический О (фиг.2,э), который запускает формирователь 5. На выходах последнего подключенных к выходным шинам 6, формируются прямой и инверсный импульсы фиксированной длительности, задержанные относительно фронта импульсов на выходных шинах 7 на величину, определяемую частотой импульсов на шине IО и кодом, первоначально записанным в счетчик 3.

Логический О с выхода элемента И-НЕ 4 (фиг.,2,з) поступает на R-вход триггера 11 и сбрасывает последний (фиг.2,г,д). При этом на выходных шинах 7 заканчивается формирование временного интервала. Логический О с прямого выхода триггера 1 (фиг.2,г) запрещает прохождение сигналов через элемент И-НЕ 2, а логическая 1 с инверсного выхода (фиг.2,д) сбрасывает делитель 12 и блокирует его работу.

Логический О с выхода элемента И-НЕ 4 поступает также на вход С счетчика 3 и на вход записи регистра 14. При этом в счетчик 3 и регистр 5 происходит запись нового значения кодов с шин 11 и 15 соответственно. При записи в счетчик 3 числа, отличного от нуля, на его выходе переноса появляется логический О (фиг.2,ж),что приводит к появлению логической 1 на выходе элемента И-НЕ 4 (фиг.2,з). После этого формирователь оказывается в исходном состоянии и готов к форми20

25

30

40

45

50

55

Длительность сформированного временного интервала равна

Т N.TC4 N-К ,.„„„ ,

Т сч

где N - число, соответствующее двоичному коду, устанавливаемому на шинах 11 и записываемому в счетчик 3; период повторения счетных импульсов (дискрет формирования) на шине 10, т.е. на выходе мультиплексора 13; Т - период повторения импульсов

синхронизации на шине 8; К - коэффициент, определяемый

кодом N .j на шинах 15 и равный К 2 л .

При необходимости изменения длительности Т формируемого временного 35 интервала в формирователе изменяется число N, записываемое в счетчик 3 по шинам 11. Кроме того, частота счетных импульсов может оперативно меняться путем задания нового значения кода на шинах 15. Если код на шинах 15 равен О, то мультиплексор 13 пропускает на выход импульсы синхронизации

с шины 8 и Тсц Тсинг . Если код на шинах 15 установлен от 1 до L-1, то мультиплексор 13 пропускает на выход сигнал с соответствующего выхода делителя 12 и

Т сч 1 i

где К,- - коэффициент деления делителя 12 от входа до 1-го выхода, ,...,L-l; Kj 2 ;

Т - период повторения импульсов

синхронизации на шине 8.

Известный формирователь имеет низкую точность формирования временного интервала, вызванную тем, что в нем возможны неблагоприятные произвольные соотношения временных положений синх

рованию cr-дукщет крещенного интервала.

Таким образом, на прямом и инверсном выходах триггера I, т.е. на выходных шинах 7, формируются соответственно прямой и инверсный импульсы, длительность которых (Т) определяется дискретом формирования, задаваемым кодом на шинах 15 и кодом, устанавливаемым на шипах 11, а на выходах формирователя 5, т.е. на выходных шинах 6, формируются соответственно прямой и инверсный импульсы фиксированной длитель0

5

0

0

Длительность сформированного временного интервала равна

Т N.TC4 N-К ,.„„„ ,

Т сч

где N - число, соответствующее двоичному коду, устанавливаемому на шинах 11 и записываемому в счетчик 3; период повторения счетных импульсов (дискрет формирования) на шине 10, т.е. на выходе мультиплексора 13; Т - период повторения импульсов

синхронизации на шине 8; К - коэффициент, определяемый

кодом N .j на шинах 15 и равный К 2 л .

При необходимости изменения длительности Т формируемого временного 5 интервала в формирователе изменяется число N, записываемое в счетчик 3 по шинам 11. Кроме того, частота счетных импульсов может оперативно меняться путем задания нового значения кода на шинах 15. Если код на шинах 15 равен О, то мультиплексор 13 пропускает на выход импульсы синхронизации

5

0

5

с шины 8 и Тсц Тсинг . Если код на шинах 15 установлен от 1 до L-1, то мультиплексор 13 пропускает на выход сигнал с соответствующего выхода делителя 12 и

Т сч 1 i

где К,- - коэффициент деления делителя 12 от входа до 1-го выхода, ,...,L-l; Kj 2 ;

Т - период повторения импульсов

синхронизации на шине 8.

Известный формирователь имеет низкую точность формирования временного интервала, вызванную тем, что в нем возможны неблагоприятные произвольные соотношения временных положений синхронизирующих,и счетных импульсов. Ошибка формирования временного интервала может достигать периода повторения счетных импульсов при разности

из импульсов синхронизации позволяет оперативно изменять частоту счетных импульсов, чем упрощает процедуру кратного изменения величины формируефаз такой, что счетный импульс появля- мого временного интервала. Это уменьется сразу же после импульса синхронизации. Кроме того, при малых разностях фаз во время формирования сигнала переноса на выходе счетчика -3 на вы- 1Q ходе элемента И-НЕ 4 может сформироваться укороченный импульс, длительность которого может быть недостаточной для надежного срабатывания элегентов формирователя, что также приводит 15 частоты, мультиплексор и регистр, при

20

к ошибке формирования.

В предлагаемом формирователе этот недостаток устранен за счет введения дополнительных делителя частоты, мультиплексора и регистра, обеспечивающих жесткую привязку счетных импульсов по отношению к импульсам синхронизации. При этом точность формирования временного интервала определяется только нестабильностью частоты импульсов 25 синхронизации, так как счетные импульсы формируются из импульсов синхронизации, причем разность фаз между ними равна нулю. Кроме того, предлагаемое формирование счетных импульсов -jo

. .

этом первый информационный вход мультиплексора и счетный вход делителя - частоты подключены к шине синхронизации, остальные информационные входы мультиплексора подключены к выходам делителя частоты, установочный вход которого подключен к инверсному выходу триггера, информационные входы регистра подключены к дополнительным кодовым шинам, а его вход записи соединен с выходом второго элемента И-НЕ, выходы регистра подключены к управляющим входам мультиплексора, выход которого подключен к второму входу первого элемента И-НЕ.

из импульсов синхронизации позволяет оперативно изменять частоту счетных импульсов, чем упрощает процедуру кратного изменения величины формируемого временного интервала. Это уменьшает вероятность ошибки оператора, что в свою очередь повышает точность.

Формула изобретения

Формирователь временного интервала по авт. св. № 1 198744, отличающийся тем, что, с целью повышения точности, в него введены делитель

частоты, мультиплексор и регистр, при

этом первый информационный вход мультиплексора и счетный вход делителя - частоты подключены к шине синхронизации, остальные информационные входы мультиплексора подключены к выходам делителя частоты, установочный вход которого подключен к инверсному выходу триггера, информационные входы регистра подключены к дополнительным кодовым шинам, а его вход записи соединен с выходом второго элемента И-НЕ, выходы регистра подключены к управляющим входам мультиплексора, выход которого подключен к второму входу первого элемента И-НЕ.

| Авторское свидетельство СССР № 1198744, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-09-30—Подача