Изобретение относится к вычислительной технике и может быть использовано для обнаружения и исправления ошибок при считывании микрокоманд из оперативной памяти в процессор.

Целью изобретения является повышение достоверности контроля путем исправления наиболее вероятных двойных ошибок.

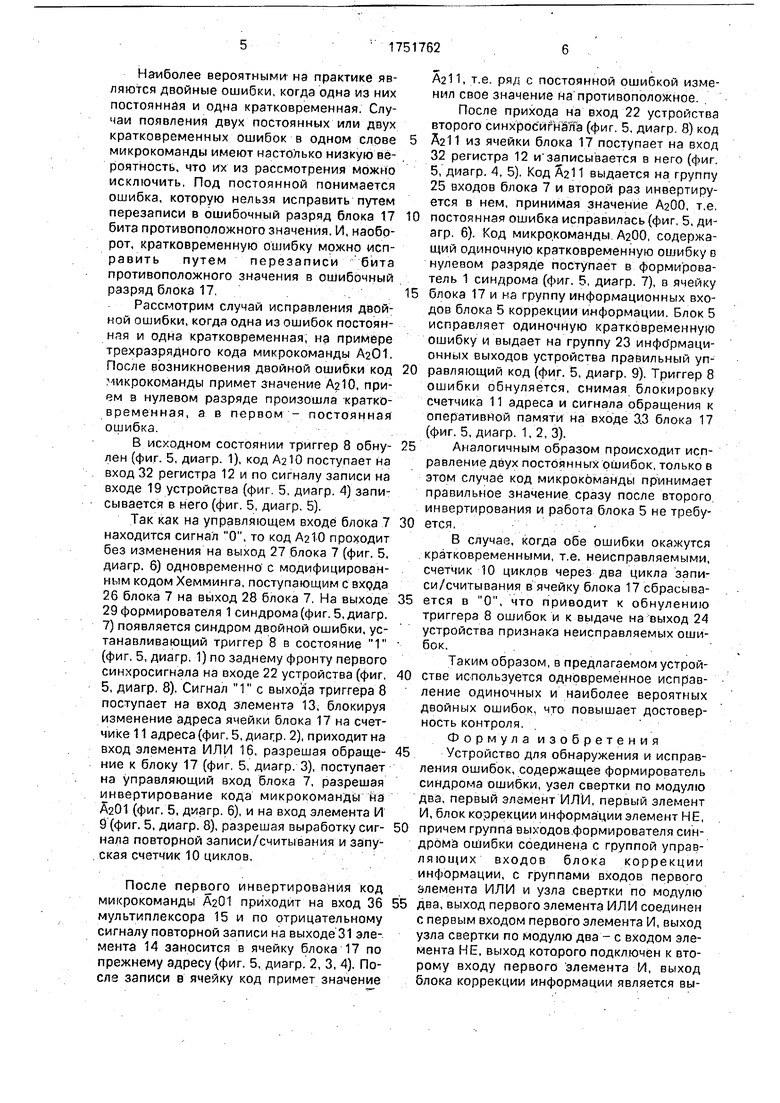

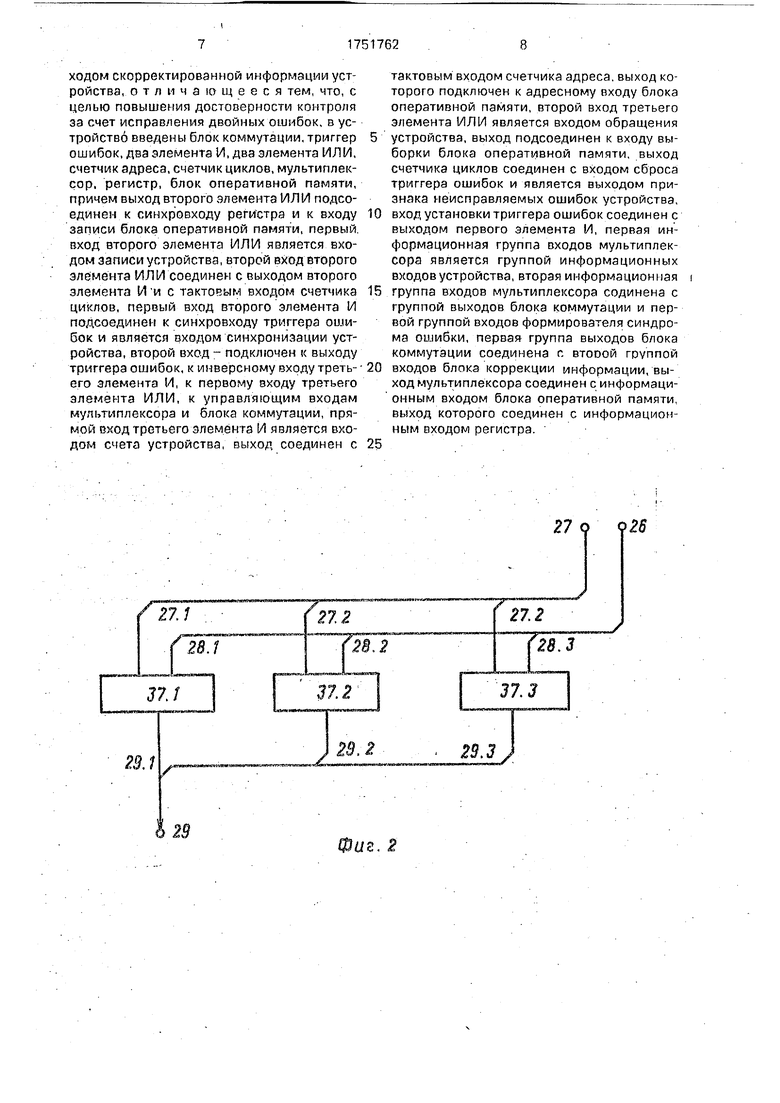

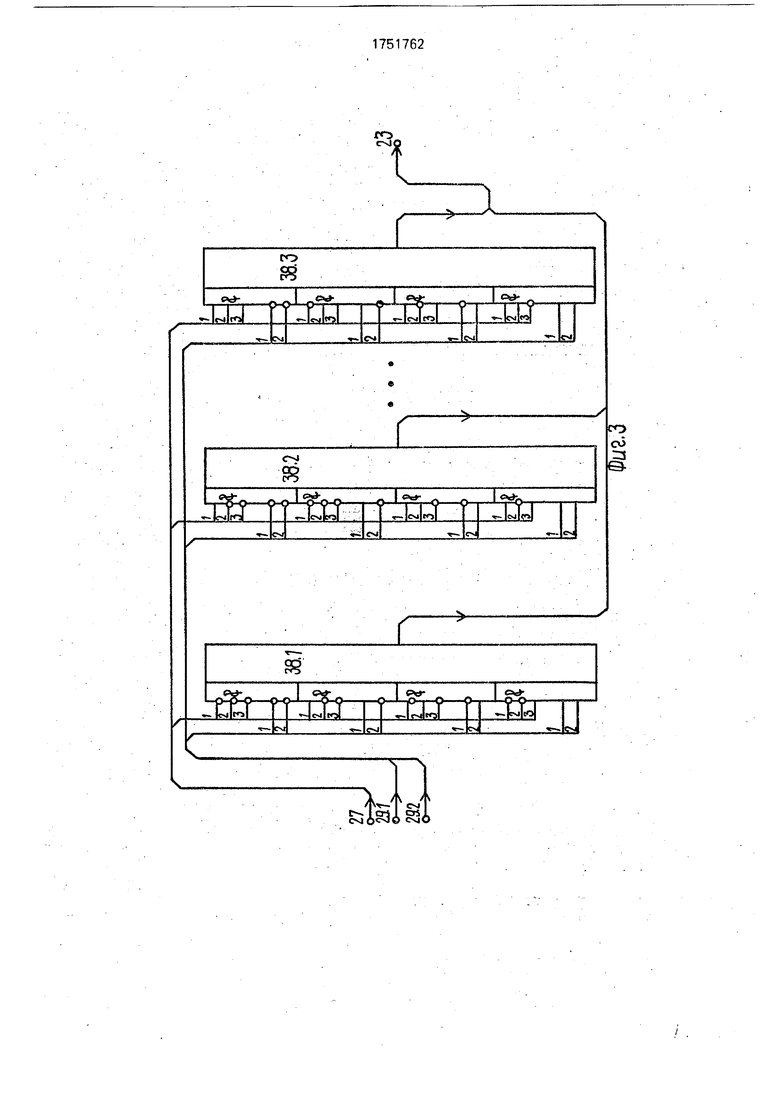

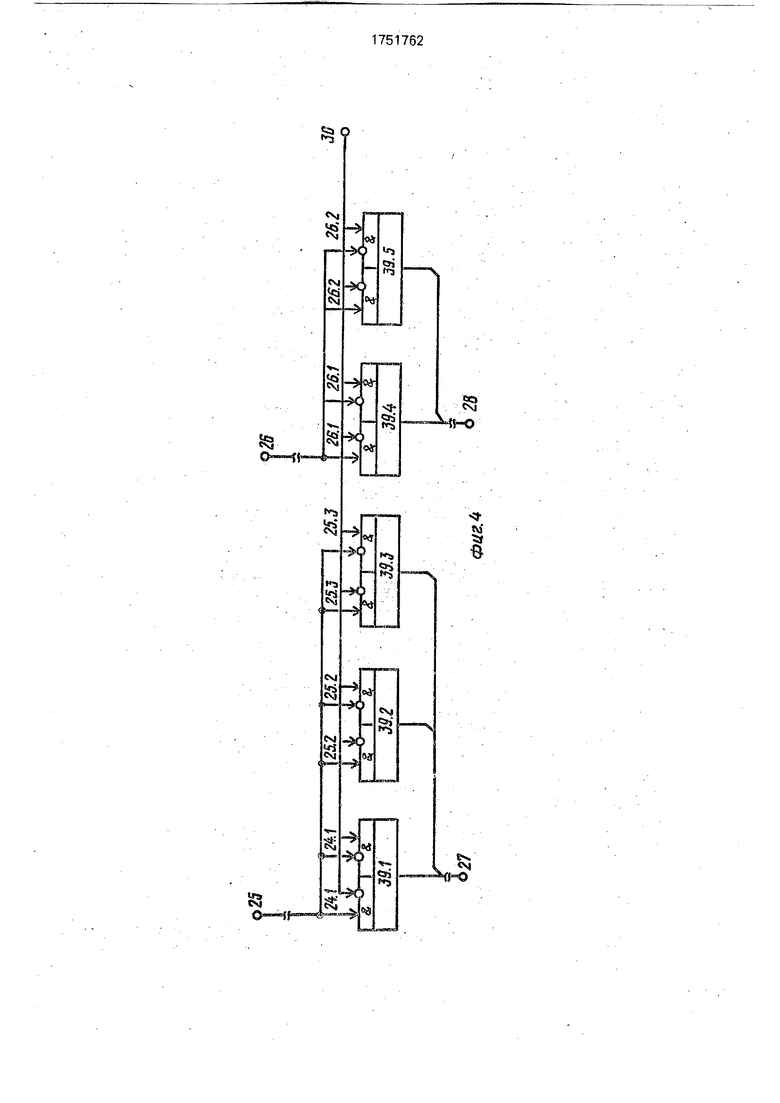

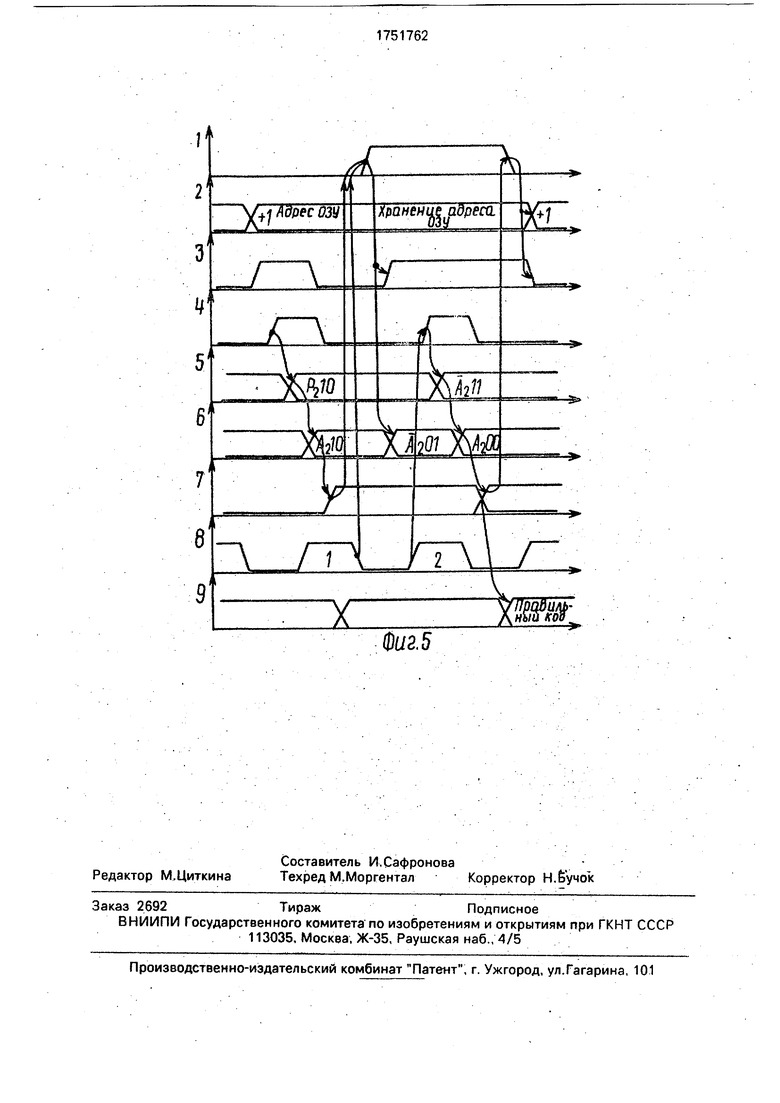

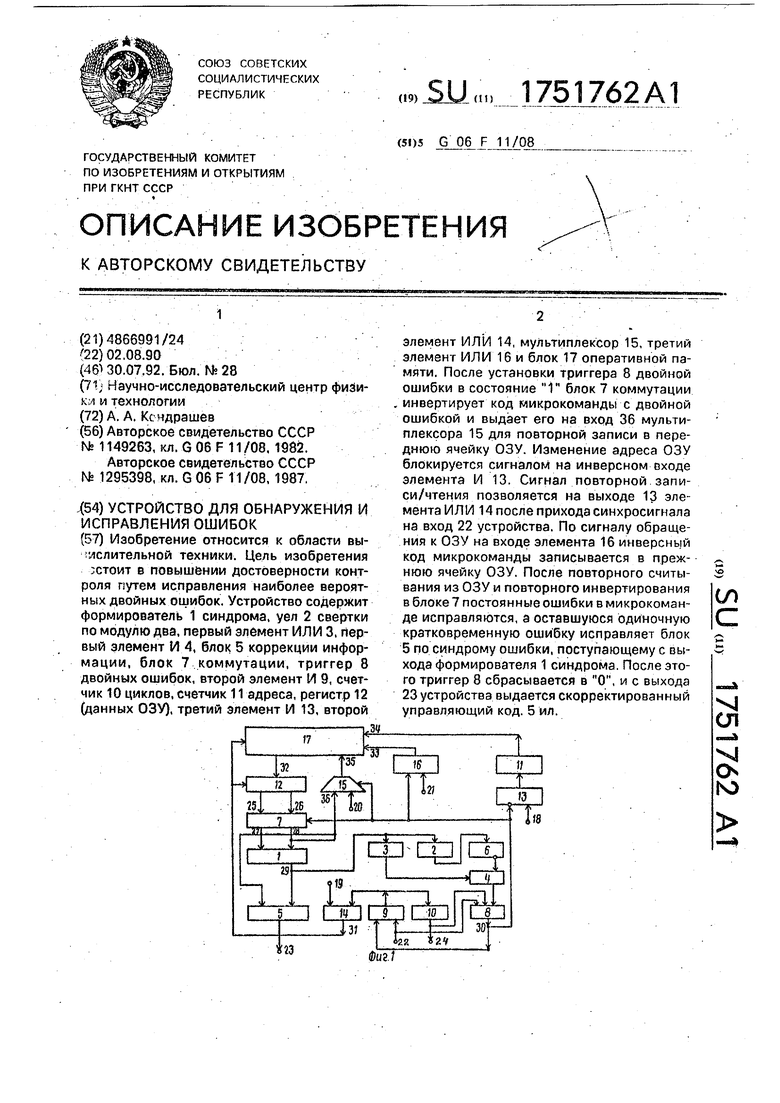

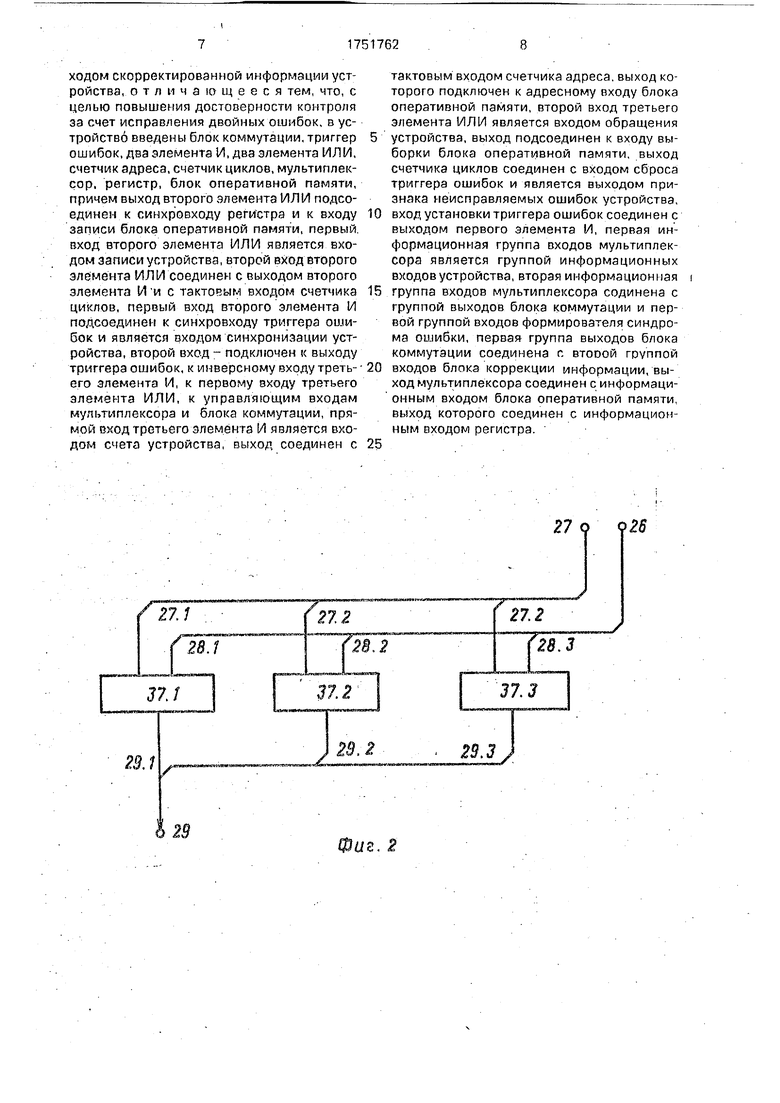

На фиг. 1 представлена структурная схема устройства для обнаружения и исправления ошибок; на фиг. 2 - схема формирователя синдрома ошибки для на фиг. 3 - функциональная схема блока коррекции информации для на фиг. 4 - схема блока коммутации для на фиг. 5 - временные диаграммы работы устройства.

Устройство для обнаружения и исправления ошибок (фиг. 1) содержит формирователь 1 синдрома ошибки, узел 2 свертки по модулю два, первый элемент ИЛИ 3, первый элемент И 4, блок 5 коррекции информации, элемент НЕ 6, блок 7 коммутации, триггер 8 ошибок, второй элемент И 9, счетчик 1, циклов, счетчик 11 адреса, регистр 12, третий элемент И 13, второй элемент ИЛИ 14, мультиплексор 15, третий элемент ИЛИ 16, блок 17 оперативной памяти, вход 18 счета устройства, вход 19 записи устройства, вход 20 информации устройства, вход 21 обращения устройства, вход 22 синхронизации устройства, группу 23 выходов скорректированной информации устройства, выход 24 признака неисправляемых ошибок устройства, первую группу 25 информационных входов блока 7, вторую группу 26 информационных входов блока 7, группу 27 информационных выходов блока 7, группу 28 выходов контрольных разрядов блока 7, группу 29 информационных выходов формирователя синдрома ошибки, выход 30 триггера ошибок, выход 31 элемента ИЛИ 14, информационный вход 32 регистра 12, вход 33 выборки блока 17 оперативной памяти, сход 34 адреса блока 17 оперативной памяти, информэционнпй вход 35 блока 17, первую информационную группу 36 входов мультиплексора.

Формирователь 1 синдрома ошибки (фиг. 2) содержит группу схем 37 сверток по модулю два.

Блок 5 коррекции информации (фиг. 3) содержит группу из 2т мультиплексоров 38, где - число информационных разрядов.

Блок 7 коммутации (фиг. 4) содержит группу 39 из m+Iogam-H элементов 2И- ИЛИ. Число элементов 2И-ИЛИ блока 7 равно числу разрядов ячейки блока оперативной памяти, которое равно сумме информационных и (Iog2m+1) контрольных разрядов

Формирователь 1 синдрома ошибки предназначен для выработки синдрома

ошибки, причем появление 1 в каком-либо оазряде означает ошибку в соответствующем входном информационном разряде. Синдром ошибки содержит позиционный номер искаженного разряда микроквманды. Узел 2 свертки по модулю два предназначен для свертки синдрома по модулю два и выработки сигнала двойной ошибки. Элемент ИЛИ 3 вырабатывает признак наличия хотя бы одной 1 в разрядах синдрома.

Элемент И 4 осуществляет выработку признака двойной ошибки. Блок 5 коррекции информации производит исправление одиночной ошибки в микрокоманде, поступающей на выход 27, по значению синдрома

ошибки, приходящего на выход 29. Блок 7 коммутации осуществляет исправление двойных ошибок путем инвертирования микрокоманды при наличии признака двойной ошибки на выходе 30 триггера 8 Триггер 8 ошибок предназначен для индикации признака двойной ошибки.

Элемент И 9 осуществляет блокировку подачи на счетный вход счетчика 10 циклов синхросигналов с входа 22 устройства. Счетчик 10 циклов предназначен для выдачи через два цикла записи/считывания сигнала о неисправлении ошибок на выход 24 устройства и на вход сбрбса триггера 8. Счетчик 11 адреса (оперативной памяти) предназначен

для адресации блока 17 оперативной памяти по сигналам счета, поступающим на вход 18 счета устройства Регистр 12 осуществляет хранение данных, считываемых из блока 17 Элемент И 13 предназначен для блокировки сигналов счета при единичном состоянии триггера 8.

Элемент ИЛИ 14 передает сигналы записи/считывания в блок 17 оперативной памяти и на тактовый вход регистра 12,

Мультиплексор 15 предназначен для передачи на информационный вход 35 блока 17 прямой информации с входами 20 устройства или инвертированной информации с групп выхс дов 27, 28 блока 7 в зависимости

от состояния триггера 8. Элемент ИЛИ 16 осуществляет передачу сигналов обращения к блоку 17 оперативной памяти.

Блок 17 оперативной памяти осуществляет хранение информации, ее перезапись

и выдачу по сигналу обращения из входе 33 блока 17 на вход 32 регистра 12.

Устройство работает следующим образом.

Исправление двойных ошибок

Наиболее вероятными на практике являются двойные ошибки, когда одна из них постоянная и одна кратковременная. Случаи появления двух постоянных или двух кратковременных ошибок в одном слове микрокоманды имеют настолько низкую вероятность, что их из рассмотрения можно исключить. Под постоянной понимается ошибка, которую нельзя исправить путем перезаписи в ошибочный разряд блока 17 бита противоположного значения. И, наоборот, кратковременную ошибку можно исправить путем перезаписи бита противоположного значения в ошибочный разряд блока 17.

Рассмотрим случай исправления двойной ошибки, когда одна из ошибок постоянная и одна кратковременная, на примере трехразрядного кода микрокоманды АаСИ. После возникновения двойной ошибки код микрокоманды примет значение А210, прием в нулевом разряде произошла кратковременная, а в первом - постоянная ошибка.

В исходном состоянии триггер 8 обнулен (фиг. 5, диагр. 1), код А2Ю поступает на вход 32 регистра 12 и по сигналу записи на входе 19 устройства (фиг 5, диагр. 4) записывается в него (фиг. 5, диагр. 5).

Так как на управляющем входе блока 7 находится сигнал О, то код А2Ю проходит без изменения на выход 27 блока 7 (фиг. 5, диагр. 6) одновременно с модифицированным кодом Хемминга, поступающим с входа 26 блока 7 на выход 28 блока 7, На выходе 29 формирователя 1 синдрома (фиг. 5, диагр. 7) появляется синдром двойной ошибки, устанавливающий триггер 8 в состояние 1 (фиг. 5, диагр. 1) по заднему фронту первого синхросигнала на входе 22 устройства (фиг. 5, диагр. 8). Сигнал 1 с выхода триггера 8 поступает на вход элемента 13, блокируя изменение адреса ячейки блока 17 на счетчике 11 адреса (фиг. 5, диагр. 2), приходит на вход элемента ИЛИ 16, разрешая обращение к блоку 17 (фиг. 5, диагр. 3), поступает на управляющий вход блока 7, разрешая инвертирование кода микрокоманды на А201 (фиг. 5, диагр. 6), и на вход элемента И 9 (фиг. 5, диагр. 8), разрешая выработку сигнала повторной записи/считывания и запуская счетчик 10 циклов.

После первого инвертирования код микрокоманды А201 приходит на вход 36 мультиплексора 15 и по отрицательному сигналу повторной записи на выходе 31 элемента 14 заносится в ячейку блока 17 по прежнему адресу (фиг. 5, диагр. 2, 3, 4). По- слэ записи в ячейку код примет значение

А211, т.е. ряд с постоянной ошибкой изменил свое значение на противоположное.

После прихода на вход 22 устройства второго синхросигнала (фиг. 5, диагр 8) код 5 А211 из ячейки блока 17 поступает на вход 32 регистра 12 и записывается в него (фиг. 5, диагр. 4, 5). Код 1 выдается на группу 25 входов блока 7 и второй раз инвертируется в нем, принимая значение А200, т.е.

0 постоянная ошибка исправилась (фиг, 5, диагр. б). Код микрокоманды А200, содержащий одиночную кратковременную ошибку в нулевом разряде поступает в формирователь 1 синдрома (фиг. 5, диагр. 7), в ячейку

5 блока 17 и на группу информационных входов блока 5 коррекции информации. Блок 5 исправляет одиночную кратковременную ошибку и выдает на группу 23 информационных выходов устройства правильный уп0 равляющий код (фиг. 5, диагр, 9). Триггер 8 ошибки обнуляется, снимая блокировку счетчика 11 адреса и сигнала обращения к оперативной памяти на входе 3.3 блока 17 (фиг. 5, диагр. 1, 2, 3).

5 Аналогичным образом происходит исправление двух постоянных ошибок, только в этом случае код микрокоманды принимает правильное значение сразу после второго инвертирования и работа блока 5 не требу0 ется,

В случае, когда обе ошибки окажутся кратковременными, т.е. неисправляемыми, счетчик 10 циклов через два цикла записи/считывания в ячейку блока 17 сбрасыва5 ется в О, что приводит к обнулению триггера 8 ошибок и к выдаче на выход 24 устройства признака неисправляемых ошибок.

Таким образом, в предлагаемом устрой0 стве используется одновременное исправление одиночных и наиболее вероятных двойных ошибок, что повышает достоверность контроля,

Формула изобретения

5 Устройство для обнаружения и исправления ошибок, содержащее формирователь синдрома ошибки, узел свертки по модулю два, первый элемент ИЛИ, первый элемент И, блок коррекции информации элемент НЕ,

0 причем группа выходов формирователя синдрома ошибки соединена с группой управляющих входов блока коррекции информации, с группами входов первого элемента ИЛИ и узла свертки по модулю

5 два, выход первого элемента ИЛИ соединен с первым входом первого элемента И, выход узла свертки по модулю два - с входом элемента НЕ, выход которого подключен к второму входу первого элемента И, выход блока коррекции информации является выходом скорректированной информации устройства, отличающееся тем, что, с целью повышения достоверности контроля зз счет исправления двойных ошибок, в устройство введены блок коммутации, триггер ошибок, два элемента И, два элемента ИЛИ, счетчик адреса, счетчик циклов, мультиплексор, регистр, блок оперативной памяти, причем выход второго элемента ИЛИ подсоединен к синхровходу регистра и к входу записи блока оперативной памяти, первый вход второго элемента ИЛИ является входом записи устройства, второй вход второго элемента ИЛИ соединен с выходом второго элемента И и с тактовым входом счетчика циклов, первый вход второго элемента И подсоединен к синхровходу триггера ошибок и является входом синхронизации устройства, второй вход - подключен к выходу триггера ошибок, к инверсному входу трет ь- его элемента И, к первому входу третьего элемента ИЛИ, к управляющим входам мультиплексора и блока коммутации, прямой вход третьего элемента И является входом счета устройства, выход соединен с

тактовым входом счетчика адреса, выход которого подключен к адресному входу блока оперативной памяти, второй вход третьего элемента ИЛИ является входом обращения

устройства, выход подсоединен к входу выборки блока оперативной памяти, выход счетчика циклов соединен с входом сброса триггера ошибок и является выходом признака неисправляемых ошибок устройства,

вход установки триггера ошибок соединен с выходом первого элемента И, первая информационная группа входов мультиплексора является группой информационных входов устройства, вторая информационная

группа входов мультиплексора содинена с группой выходов блока коммутации и первой группой входов формирователя синдрома ошибки, первая группа выходов блока коммутации соединена г. втооой группой

входов блока коррекции информации, выход мультиплексора соединен с информационным входом блока оперативной памяти, выход которого соединен с информационным входом регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1211725A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

Изобретение относится к области выделительной техники. Цель изобретения ;стоит в повышении достоверности контроля путем исправления наиболее вероятных двойных ошибок. Устройство содержит формирователь 1 синдрома, уел 2 свертки по модулю два, первый элемент ИЛИ 3, первый элемент И 4, блок 5 коррекции информации, блок 7 коммутации, триггер 8 двойных ошибок, второй элемент И 9, счетчик 10 циклов, счетчик 11 адреса, регистр 12 (данных ОЗУ), третий элемент И 13, второй Ш элемент ИЛИ 14, мультиплексор 15, третий элемент ИЛИ 16 и блок 17 оперативной памяти. После установки триггера 8 двойной ошибки в состояние 1 блок 7 коммутации . инвертирует код микрокоманды с двойной ошибкой и выдает его на вход 36 мультиплексора 15 для повторной записи в переднюю ячейку ОЗУ. Изменение адреса ОЗУ блокируется сигналом на инверсном входе элемента И 13. Сигнал повторной записи/чтения позволяется на выходе 13 элемента ИЛИ 14 после прихода синхросигнала на вход 22 устройства. По сигналу обращения к ОЗУ на входе элемента 16 инверсный код микрокоманды записывается в прежнюю ячейку ОЗУ. После повторного считывания из ОЗУ и повторного инвертирования в блоке 7 постоянные ошибки в микрокоманде исправляются, а оставшуюся одиночную кратковременную ошибку исправляет блок 5 по синдрому ошибки, поступающему с выхода формирователя 1 синдрома. После этого триггер 8 сбрасывается в О, и с выхода 23 устройства выдается скорректированный управляющий код. 5 ил. (Л С а ч о ю Фиг

Г

29

27 о 926

г. 2

Ј32

I

1

СО

v

к

CviooJO cviO

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для исправления одиночных и обнаружения двойных ошибок | 1985 |

|

SU1295398A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ,(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК | |||

Авторы

Даты

1992-07-30—Публикация

1990-08-02—Подача