vi

СА2 ОЭ

Изобретение относится к вычисли- .тельной технике и может быть использовано при конвейерной поразрядной обработке операндов, представленных в избыточной знакоразрядной системе счисления (ИЗСС) с ОД.

Цель изобретения повьшение быстродействия.

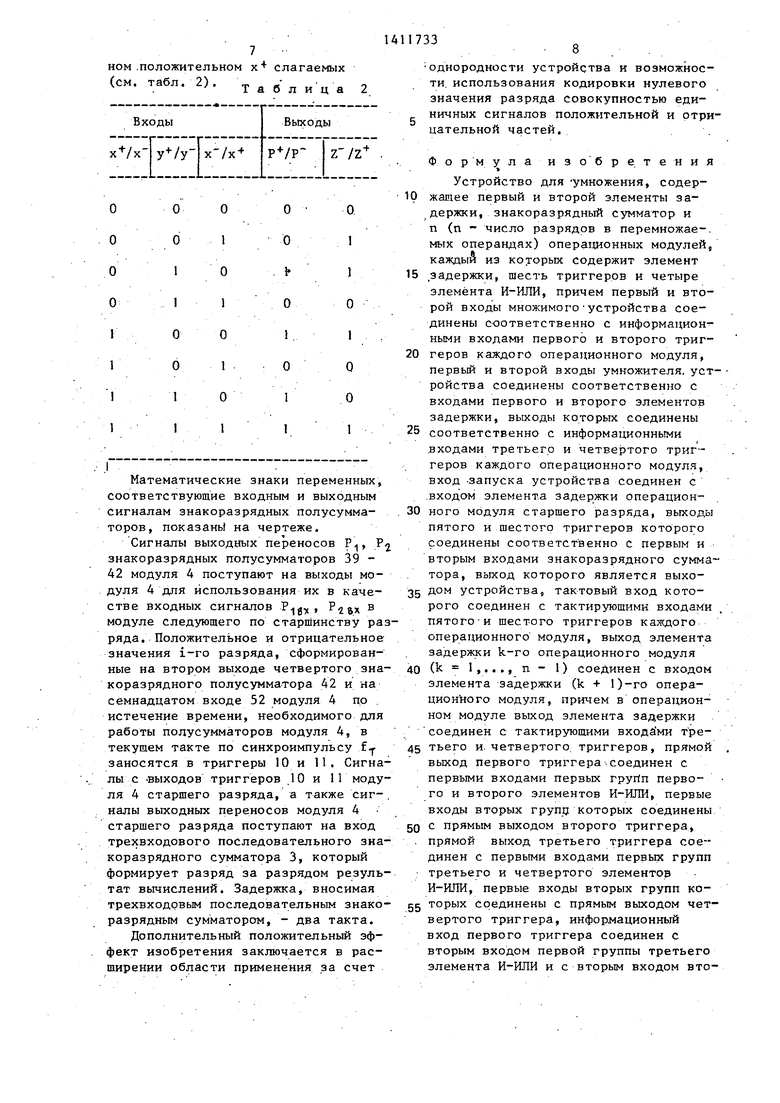

На чертеже представлена схема устройства для умножения.

Устройство содержит первый 1 и второй 2 элементы задержки, знако- разрядный сумматор 3, операционные модули 4, каждый из.которых содержит элемент 5 задержки, шесть триггеров. 6 - 11, .четыре элемента И-ИЛИ 12 - 15,- Причем первый 16 и второй 17 входы множимого устройства соеди- нены соответственно с первыми 18 и вторыми 19 входами модулей 4, первый 20 и второй. 21 входы -/множителя устройства соединены соответственно с третьими 22 и четвертыми 23.-входами модулей 4 и через элементы i и 2 за- дер;кки соответственно с пятым 2А и шестым 25 входами модулей 4, вход- .26-запуска устройства соединен.с седьмым ВХОДОМ 27 модуля 4 старшего разряда, .

. В каждом модуле 4 седьмой вход 27 соед1-1нен через элемент 5 задержки стактирующими входами третьего 8 и четвертого 9 триггеров модуля 4 и с первым выходом 28- модуля 4, Информационные входы первого 6 и второго 7 триггеров соединены соответственно с первым 18 и вторым 19 входами модуля 4. Прямой выход первого триггера 6 соединен с первьми входами первых групп первого 12 и второго 13 элементов И-ИЛИ, первые входы вторых групп которых соединены с прямым вы- ходом второго триггера 7. Прямой выход третьего триггера 8 соединен с первыми входами первых групп третьего 4-и четвертого 15 элементов И-ИЛИ, первые входы вторых групп которых соединен с прямым выходом - четвертого триггера 9.

Первьш вход 18 модуля соединен с вторым входом первой группы третьег.о элемента И-ИЛИ 14 и с вторым входом второй группы четвертого элемента И-ИЛИ 15. Второй вход 19 модуля соединен о вторым входом второй группы третьего элемента И-ИЛИ 14 и-с вторым входом первой группы четвертого элемента И-ИЛИ 15. Выходы пятого 10

и шестого 11 триггеров соединены соответственно с вторым 29 и третьим 30 выходами модуля 4. Первый выход 28 модуля 4 каждого разряда, начи- ная со старшего, соединен с седьмым, входом 27 модуля 4 разряда, младшего на единицу. Второй 29 и третий 30 выходы модуля 4 каждого разряда,

Q кроме старшего., соединены соответ- . ственно с восьмым 31 и девятым 32 входами модуля, 4 разряда, следующего по старшинству. . . Второй 29, третий 30, четвертый

5 33 и пятый 34 выходы модуля 4 стар- шег о разряда соединены соответственно с первым, вторым, третьим и чет-- вертым входами, знакоразрядного сумматора 3, выходы которого являются вы0 .ходами устройства. Восьмой 3 и девятый 32 входы модуля 4 старшего разряда сое.динены с входом нулевого потенциала устройства.

Кроме того, устройство содержит

5 ..четыре элемента НЕ 35. - 38, а в каждом модула 4 по четыре знако.разряд- ных полусумматора 39 - 42, причем входы первого 35, второго 36, третьего. 37 и четвертого ЗВ элементов tfe

0 соединены соответственно с первыми 18, вторыми 19, третьими 22 и четвертыми 23 входами модулей 4, а выходы - соответственно с десятыми 43, одиннадцатыми 44, двенадцатыми 45 и тринадцатыми 46 входами модулей 4. Шестой 4.7 и седьмой 48 выходы модуля.4 старшего разряда соединены соответственно с, пятым и шестым, вхо-. дами знакоразрядного сумматора 3.

д Четвертый 33, пятый 34, шестой 47 и седьмой 48 выходы модуля 4 каждого разряда соединены соответственно с - четырнадцатым, пятнадцатым, шестнадцатым и семнадцатым входами 49 - 52 модуля 4 следукзшего по старшинству -разряда. Четырнадцатый, пят , надцатый, шестнадцатьй и семнадца- - тый входы 49 - 52 соответственно мо дуля 4 младшего разряда соединены с входом нулевого потенциала устрой5

5

9

ства,

Причем в модуле 4-тактирующие вхс ды первого.6 и второго 7 триггеров соединены с седьмым входом 27 моду- ля 4. Инверсный выход перзого триггера 6 соединен с вторыми входами вторых групп первого 12 и второго 13 элементов. И-ИЯИ, инверсный выход второго триггера 7 - с вторыми вхо

, 5

ами первых групп первого 12 и втоого 13 элементов И-ИЛИ, инверсный ыход третьего триггера 8 - с третьии входами вторых групп третьего 14 четвертого 15 элементов И-ИЛИ, ин ерсный выход четвертого триггера - с третьими входами первых групп третьего 14 и четвертого 15 элементов И-ИЛИ. Третьи входы первой груп- ы первого элемента И-ИЛИ 12 и второй группы второго элемента И-ИЛИ 13 соединены с третьим входом 22 модуля 4, четвертый вход 23 которого соединен с третьими входами второй груп- пы первого элемента И-ИЯИ 12 и первой группы второго элемента И-ИЛИ 13. Четвертые входы второй группы первого элемента И-ИЛИ 12 и первой группы второго элемента И-ИЛИ 13 соединены „ с двенадцатым входом 45 модуля 4, тринадцатый вход 46 которого соединен с нетверть1ми входами первой группы первого элемента И-ИЛИ 12 и второй группы второго элемента И-ИЛИ 13. Де-25 сятый вход 43 модуля 4 соединен- с четвертыми входами второй группы третьего элемента И-ИЛИ 14 и первой, группы четвертого элемента И-ИЛИ 15, одиннадцатый вход 44 модуля 4 - с „ четвертыми входами первой группы третьего элемента И-ИЛИ 14 и второй группы четвертого элемента И-ИЛИ 15. Информационные входы третьего 8 и четвертого 9 триггеров модуля 4 соединены соответственно с пятым 24 и. шестым 25 входами модуля 4. Первый, второй и третий входы первого знако- разрядного полусуммато.ра 39 соединены с выходами соответственно первого, второго И-третьего элементов И-ИЛИ 12 - 14, а первый, второй и третий входы второго знакоразрядного полусумматора 40 - соответственно с

выходом четвертого элемента И-ИЛИ 15, восьмым 31 и девятым 32 входами модуля 4. Первые выходы первого 30 и второго 40 знакоразрядного полусумматоров соединены соответственно с четвертьш и пятым 34 выходами модуля 4. Первый, второй и третий входы третьего знакоразрядного полусумматора 41 соединены соответственно с вторыми выходами первого 39 и второго 40 знакоразрядных полусумматоров и четырнадцатым входом 49 модуля 4. 55 Первый выход третьего знакоразрядного полусумматора 41 соединен с шестым выходом 47 модуля 4, а первый.

40

45

5

й е-ой го „ пойе-25 , , „ . и -

, а

5540

45

второй и третий входы четвертого знакоразрядного полусумматора 42 - соответственно с вторым выходом третьего знакоразрядного полусумматора 41, пятнадцатым 50 и шестнадцатым 51 входами модуля 4. Первый выход четвертого знакоразрядного полусумматора 42 соединен с седьмым выходом 48 модуля, второй выход четвертого знакоразрядного полусумматора 42 - с информационным входом пятого триггера 10. Семнадцатый вход 52 модуля 4 соединен с информационным входом шестого триггера 11.

Элементы 1 , 2 и 5 задерж15И вьтол- няют задержку на один такт.

Устройство работает следующим образом.

По первым входам множимого 16 и множителя 20 поступают положительные коды-разрядов знакоразрядных операндов, по вторым входам 17 и 2 - отрицательные (коды множимого А и множителя В), последовательно разряд за разрядом, начиная со старшего. Результат на выходах устройства получается также последовательным знакоразрядным кодом, начиная со старшего разряда. Задержка, вносимая устройством - три такта. С входа 26 устройства на тактирующие входы триггеров 6 и 7 модуля 4 старшего (первого) разряда поступает импульс, определяющий занесение в первом такте старшего разряда множимого А, на информационные входы триггеров 6 и 7 всех модулей поступают текущие значения положительных и отрицательных разрядов множимого. Далее, проходя по цепи, состоящей из последовательно включенных элементов 5 потактной задержки всех модулей, единичный импульс разрешает поочередное занесение разрядов множимого в триггеры 6 и 7 модулей соответствующих разрядов.

На тактирующие входы триггеров 8 и 9 модулей 4 старшего разряда управляющий сигнал Лоступает во втором такте (с выхода элемента 5 задержки модуля). На информационные входы триггеров 8 и 9 модулей всех разрядов последовательный код множителя В поступает задержанным на один такт элементами 1 и 2 задержки. Таким образом, первый разряд множимого записывается в триггеры 6 и 7 модуля первого разряда на

первом такте работы устройства, а первый разряд множителя - в триггеры 8 и 9 модуля первого разряда на втором такте, тогда же, когда и второй разряд множимого в соответ- ствующие триггеры модуля второго разряда и т.д. Такая организация занесения позволяет, преобразовывая последовательный код операндов в параллельный и запоминая его в триггерах 5 - 8, формировать значения а и Ъ|, соотв(етствующие состояниям триггеров 6-9 модуля i-ro разряда, позволяющие процедуру умножения поразрядно поступающих операндов свести к поразрядному суммированию в соответствии с выражением:

(А-В)- где (А-В);

(А-В),-,, -н ,

(1)

значение 1-го разряда произведения в текущем такте Т|

(A-B)j, - значение (i + 1)-го (младшего) разряда в предшествующем такте Т - 1;

а, Ь - текущие значения разрядов множимого и множителя (в такте Т); а., Ь- - состояния триггеров . множимого и множителя в текущем такте Т. При знакоразрядном кодировании в двоичной системе счисления с цифрами 1, О, I каждый разряд числа представляется совокупностью положительной и отрицательной частей в соответствии с табл. 1.

Таблица 1

Число X

+ 1 -I

Знакоразрядное представление Х 0(1)

X 0(1)

I О О 1

При знакоразрядном кодировании выражение (I) принимает вид:

(A,B)t + (А-В)-. (A-B)t,

20

+ (A-B)f4 + (атЬ,.) + (ат-Ь, ) + + (а- Ь) + ().

(2)

Знакоразрядное представление чисел, характеризуемое ограниченной

глубиной переноса при суммировании, позволяет поразрядную обработку при умножении согласно выражению (2) выполнять на одинаковых модулях 4. При этом члены (A-B)t и (А-В)., поступают в качестве первого и второго слагаемого выражения (2) на входы 31 и 32 модуля i-ro разряда с выходов 29 и 30 модуля 4 (i + 1)-го (млад- щего на единицу) разряда. Слагаемые (а,Ь)% ()-, (атЬ,)- и ( ,) формируются на выходах соответственно первого, второго, третьего и четвертого злементов И-ИЛИ 12-15 модуля 4 согласно выражениям

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Устройство для умножения | 1987 |

|

SU1569823A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1987 |

|

SU1444755A1 |

| Устройство для умножения чисел с фиксированной запятой | 1989 |

|

SU1758644A1 |

Изобретение относится к вычислительной технике и может быть использовано при конвейерной обработке знакоразрядных чисел, позволяющей представлять операнды и получать результат их обработки последовательно старшими разрядами вперед. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство для умножения, содержащее два элемента 1,2 задержки, знакоразрядный сумматор 3, группу операционных модулей 4, содержащих каждый по шесть триггеров 6-11, четыре элемента И-ИЛИ 12-15 и элемент 5 задержки, дополнительно вводятся четыре элемента НЕ 35-38, а в каждый операционный модуль - по четыре знакоразрядных полусумматора 39-42 с соответствующими связями. I ил., 2-табл. а

(а-Ь) а| -Ь; .a- (abт-) а Ь - а

() а-

:

т г-ьГ(а - Ц )- а; . Ь- . а; -Ь| Va; bt - .

Чпены с черточкой наверху - инверс- ные значения соответствующих сигналов , получаемые для текущих значений а и be выходов элементов НЕ 35 - 38, для сигналов а и Ь , - с инверсных выходов соответствующих триггеров.

Суммирование трех знакоразряд- ных чисел согласно выражению (2) производится параллельно на первом 39 и втором 40 знакоразрядных полусумматорах модуля 4, а формирование разряда с учетом поступающих из моb;va- Ь V а:

а

ь;;

ЬТ -VarbT а

va, -к о- .

т г-ьГ; -Ь| Va; bt - .

(3) (4) (5) (6)

дуля 4 младщего разряда двух знакоразрядных .переносов Piex и Р2.бх третьем 41 и четвертом 42 знакоразрядных полусумматорах модуля 4.

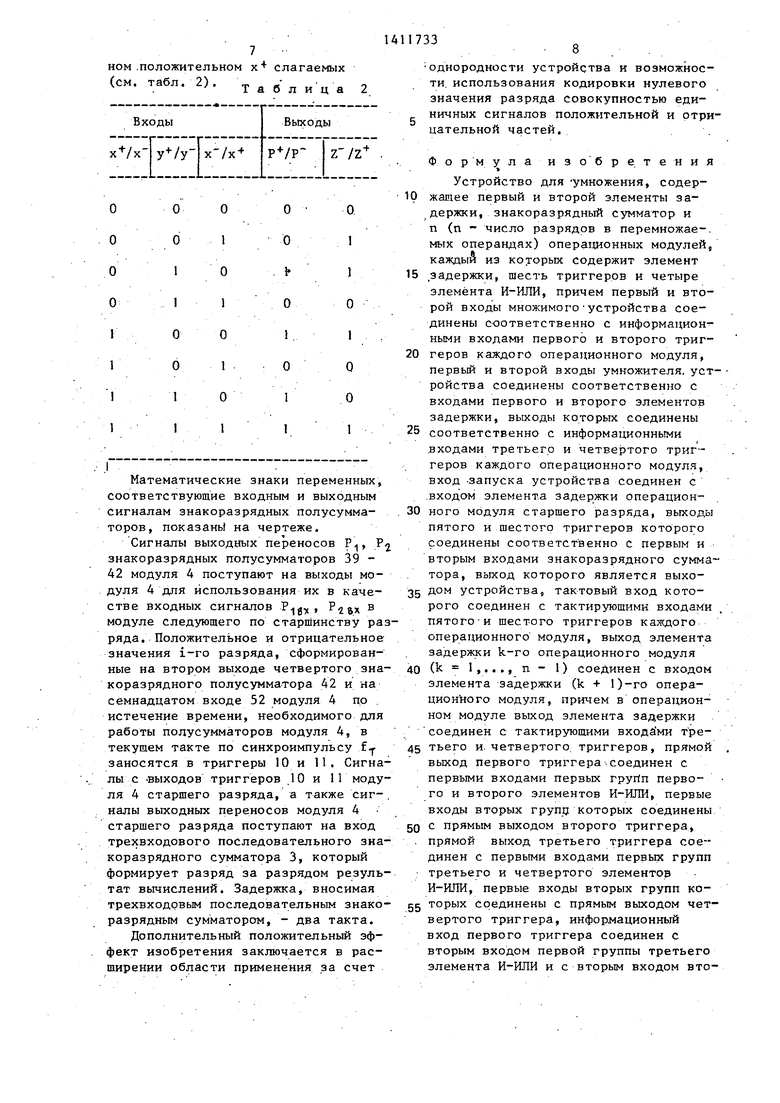

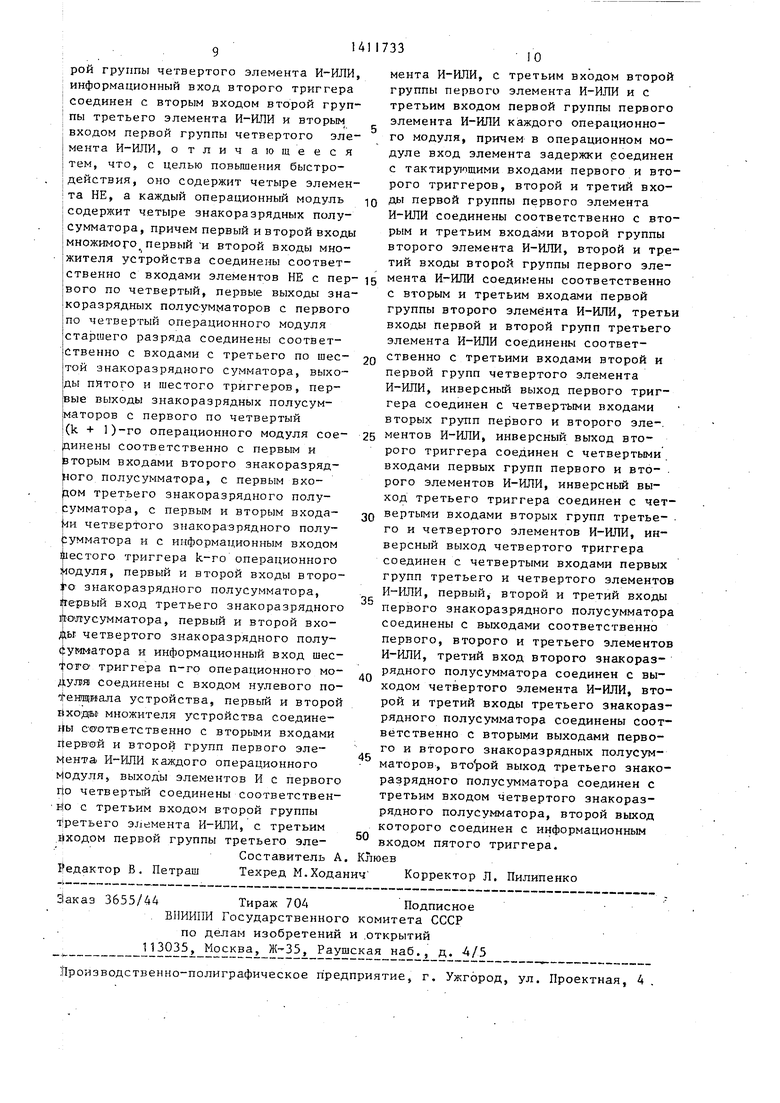

Полусумматоры 39 и 41 формируют значения положительного переноса Р и отрицательной суммы Z при ;Шух положительных х, и одном отрицательном х слагаемых, а знакоразряд- ные полусумматоры 40 и 42 производят формирование отрицательного переноса Р и положительной суммы Z При двух отрицательных х, у и одном .положительном х слагаемых (см. табл. 2). т б „ ц 2

Математические знаки переменных, соответствующие входным и выходным сигналам знакоразрядных полусумматоров, показань) на чертеже.

Сигналы выходных переносов Р, Р знакоразрядных полусумматоров 39 - 42 модуля 4 поступают на выходы модуля 4 для использования их в качестве входных сигналов Р. , модуле следующего по старшинству разряда. Положительное и отрицательное значения i-ro разряда, сформированные на втором выходе четвертого зна- коразрядного полусумматора 42 и на семнадцатом входе 52 модуля 4 по . истечение времени, необходимого для работы полусумматоров модуля 4, в текущем такте по синхроимпульсу f заносятся в триггеры 10 и П. Сигналы с -выходов триггеров .10 и 11 модуля 4 старшего разряда, а также сигналы выходных переносов модуля 4 старшего разряда поступают на вход трехвходового последовательного зна- коразрядного сумматора 3, который формирует разряд за разрядом результат вычислений. Задержка, вносимая трехвходрвым последовательным знако- разрядным сумматором, - два такта.

Дополнительный положительный зф- фект изобретения заключается в расширении области применения за счет

однородности устройства и возможности, использования кодировки нулевого значения разряда совокупностью единичных сигналов положительной и отрицательной частей.

е т е н и я

Фор м улаизобр

Устройство для умножения, содержащее первый и второй элементы задержки, знакоразрядный сумматор и п (п - число разрядов в перемножав-, мых операндах) операционных модулей, каждый из которых содержит элемент задержки, шесть триггеров и четыре элемента И-ИЛИ, причем первый и второй входы множимого устройства соединены с-оответственно с информацион ными входами первого и второго триггеров каждого операционного модуля, первый и второй входы умножителя, устройства соединены соответственно с входами первого и второго элементов задержки, выходы которых соединены соответственно с информационными .входами третьего и четве этого триггеров каждого операционного модуля, вход -запуска устройства соединен с .входом элемента задержки операционнего модуля старшего разряда, выходы пятого и шестого триггеров которого соединены соответственно с первым и вторым входами знакоразрядного сумматора, выход которого является выхоДО устройства, тактовый вход которого соединен с тактирующими входами пятого И шестого триггеров каждого операционного модуля, выход элемента задержки k-ro операционного модуля

(k 1 .. . п - 1) соединен с входом элемента задержки (k + 1)-го опера- модуля, причем в операционном модуле выход элемента задержки соединен с тактирующими входами т ретьего и четвертого, триггеров, прямой выход первого триггера соединен с первыми входами первых rpyrtn первого и второго элементов И-ИЛИ, первые входы вторых групр которых соединены

с прямым выходом второго триггера, прямой выход третьего триггера соединен с первыми входами первьк групп третьего и четвертого элементов И-ИЛИ, первые входы вторых групп которых соединены с прямым выходом четвертого триггера, инфор.мационный вход первого триггера соединен с вторым входом первой группы третьего элемента И-ИЛИ и с вторым входом второй группы четвертого элемента И-ИЛИ, информационный вход второго триггера соединен с вторым входом второй группы третьего элемента И-ИЛИ и вторым входом первой группы четвертого элемента И-ИЛИ, отлича ощееся тем, что, с целью повышения быстродействия, оно содержит четыре элемента НЕ, а каждый операционный модуль содержит четыре знакоразрядных полусумматора, причем первый и второй входы множимого первый и второй входы множителя устройства соединены соответственно с входами элементов НЕ с пер- 15 мента И-ИЛИ соединены соответственно

вого по четвертый, первые выходы знакоразрядных полус-ум 1аторов с первого по четвертый операционного модуля старшего разряда соединены соответственно с входами с третьего по шестой знакоразрядного сумматора, выходы пятого и шестого триггеров, первые выходы знакоразрядных полусум- |маторов с первого по четвертый |(k + 1)-го операционного модуля сое- цинены соответственно с первым и вторым входами второго знакоразряд- иого полусумматора, с первым входом третьего знакоразрядного полусумматора, с первым и вторым входами четвертого знакоразрядного полу- умматора и с информационным входом |iecToro триггера k-ro операционного 1одуля, первый и второй входы второ- 1РО знакоразрядного полусумматора, первый вход третьего знакоразрядного п-оотусумматора, первый и второй входы четвертого знакоразрядного полу- (|:умматора н информационный вход шес- триггера п-го операционного мо- ДУЛ1Я соединены с входом нулевого по- 4енэдиала устройства, первый и второй множителя устройства соедине- соответственно с вторьми входами г1ерв ой и второй групп первого элемента И-РШИ каждого операционного Иодуля, выходы элементов И с первого г(о четвертьй соединены соответствен- к|о с третьим входом второй группы т ретьего элемента И-ИЛИ, с третьим 1 ходом первой группы третьего элеСоставитель А

редактор В, Петраш

Техред М.Ходанич

3655/44

Тираж 704Подписное

. ВИИИПИ Государственного комитета СССР

по делам изобретений и .открытий 113035, Москва, «{-35, Раушская наб., д. 4/5

мента И-ИЛИ, с третьим входом второй группы первого элемента И-ИЛИ и с третьим входом первой группы первого элемента И-ИЛИ каждого операционного модуля, причем в операционном модуле вход элемента задержки соединен с тактирующими входами первого и второго триггеров, второй и третий входы первой группы первого элемента И-ИЛИ соединены соответственно с вторым и третьим входами второй группы второго элемента И-ИЛИ, второй и третий входы второй группы первого эле0

0

С вторым и третьим входами первой группы второго элемента И-ИЛИ, третьи входы первой и второй групп третьего элемента И-ИЛИ соединены соответственно с третьими входами второй и первой групп четвертого элемента И-ИЛИ, инверсный выход первого триггера соединен с четвертыми входами вторых групп первого и второго эле-.

5 ментов И-ИЛИ, инверсный выход второго триггера соединен с четвертыми входами первых групп первого и вто- . рого элементов И-ИЛИ, инверсньй выход третьего триггера соединен с четвертыми входами вторых групп третье- . го и четвертого элементов И-ИЛИ, инверсный выход четвертого триггера соединен с четвертыми входами первых групп третьего и четвертого элементов И-ИПИ, первый, второй и третий входы первого знакоразрядного полусумматора соединены с выходами соответственно первого, второго и третьего элементов И-ИЛИ, третий вход второго знакоразрядного полусумматора соединен с выходом четвертого элемента И-ИЛИ, второй и третий входы третьего знакоразрядного полусумматора соединены соответственно с вторыми выходами первого и второго знакоразрядных полусумматоров, вто рой выход третьего знакоразрядного полусумматора соединен с третьим входом четвертого знакоразрядного полусумматора, второй выход которого соединен с информационным входом пятого триггера.

люев

5

0

0

Корректор Л. Пилипенко

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-12—Подача