&Г1

СХ)

(U9 ю

S9

Изобретение относится к вычислитель- Ной технике и может быть применено в 1 ифровых вычислительных машинах, спе- Циализированньк вычислительных устрой-j ствах, устройствах цифровой обработки сигналов и вычислительных средах, построенньрс на болыпих интегральных схемах.

Цель изобретения - повышение точ- Ю Ности вычислений.:

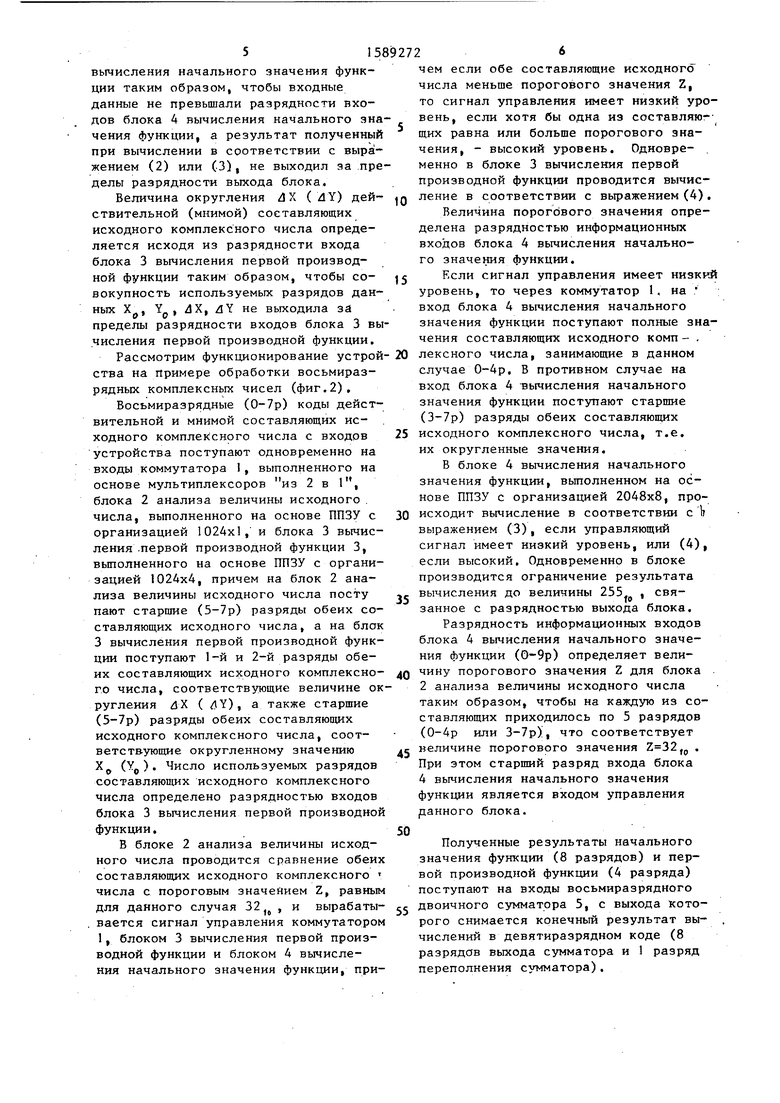

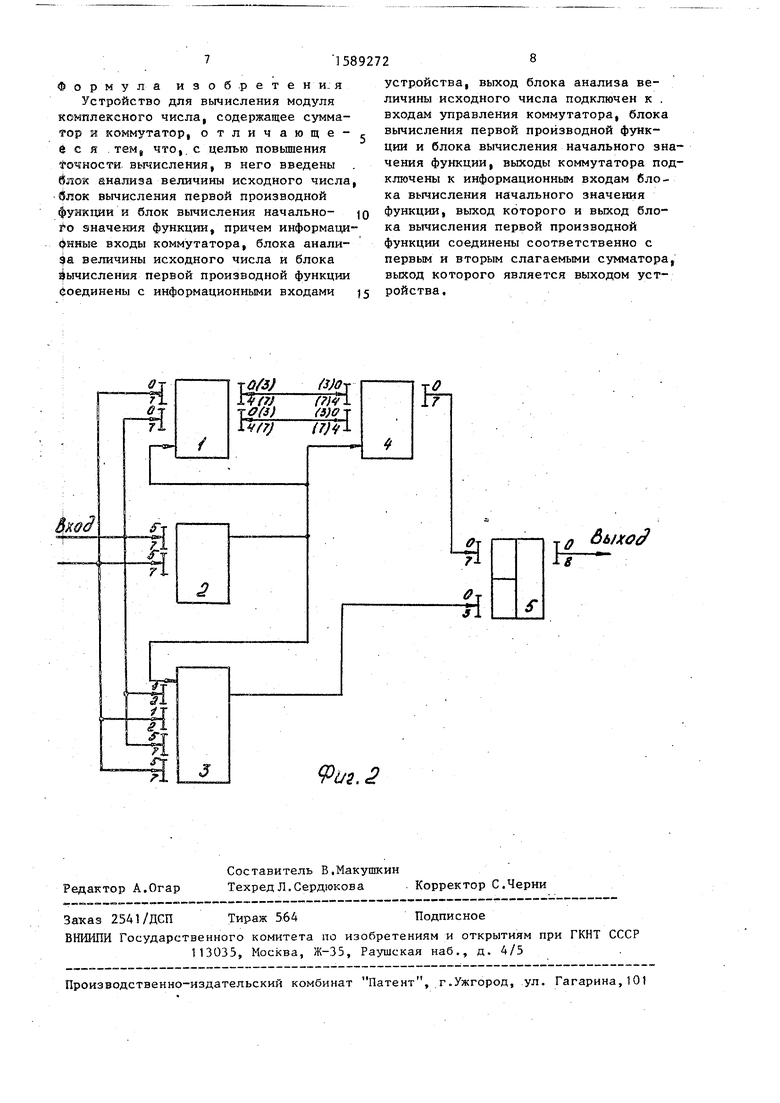

На фиг.1 представлена структурная охема устройства; на фиг.2 - пример Конкретного исполнения.

Устройство содержит коммутатор 1„ 15 0ЛОК 2 анализа величины исходного чис- jja, блок 3 вычисления первой производ- Йой функции, блок 4 вычисления началь- значения функции и сумматор 5.

В основу работы устройства положе- 20 йо разложение функции в ряд Тейлора

f(X,Y)f(X.,(X-Xj +

зх

J. lSoilol. CY-Y ) ay 0

(1)

где f(X ,Y..) - начальное значение функции;

f(bM,(.4f(Yoi,

зх

ат

первая производная функции«

Устройство работает следующим образом,

Коды действительной и 1 нимой составляющих исходного комплексного числа поступают одновременно на информационные входы коммутатора 1, блока 2 анализа величины исходного числа и блока 3 вычисления первой производной функции 3, При этом на выходе блока анализа величины исходного числа 2 формируется сигнал управления коммутатором 1 , блоком 3 вычисления пер- вой производной функции и блоком 4 вычисление начального значения .функции, причем уровень сигнала зависит от величины обеих .составляющих исходного комплексного числа.

Если обе составляющие исходного комплексного числа меньше определенного порогового значения Z , то через коммутатор 1 на вход блока 4 вычисления начального значения функции- поступают полные значения обеих состав- ляющих исходного комплексного числа„ В блоке 4 вычисления начального значе ния функции проводится обработка входных данных в соответствии с выражением

А Х + Y

(2)

где X,Y - полные значения составляющих исходного комплексного числа.

В связи с тем, что вычисление проводится с полными значениями составляющих исходного комплексного числа по оптимальному для цифровой техники алгоритму, то первая производная функция не вычисляется и имеет нулевое значение,

ЕСЛИ хотя бы одна из составляющих исходного комплексного числа больше определенного порогового значения Z, то через коммутатор 1 на вход блока 4 вычисления начального значения функции поступают округленные до величины idX, 4Y соответственно значения составляющих исходного комплексного числа. В блоке 4 вычисления начального значения функции проводится обработка входных данных в соответствии с выражением

А : Vv 2 + Y

о - о

(3)

0

-зс

Q

где Xp,Y - округленные до величин ЗХ и aJ. значения составляющих исходного комплексного числа.

В блоке 3 вычисления первой производной функции проводится при этом обработка входных данных в соответствии с выражетем

Хо/ЗХ

Vxl

(4)

Полученные величины начального значения функции и первой производной функции поступают на входы операндов . сумматора 5, с выхода которого снимается конечный результат вычисления модуля комплексного числа, полу- ченньй в соответствии с выражением

M fxbYb-faf- -.

(5)

Величина порогового значения Z составляющих исходного комплексного числа для блока 2 анализа величины исходного числа определяется исходя из разрядности входов и выхода блока 4

вычисления начального значения функции таким образом, чтобы входные данные не превышали разрядности входов блока 4 вычисления начального значения функции, а результат полученный при вычислении в соответствии с выражением (2) или (.3), не выходил за пределы разрядности выхода блока.

Величина округления ЛУ. ( ЛY) действительной (мнимой) составляющих исходного комплексного числа определяется исходя из разрядности входа блока 3 вычисления первой производной функции таким образом, чтобы совокупность используемых разрядов данных Х, YP , 4Х, 4Y не выходила за пределы разрядности входов блока 3 вычисления первой производной функции.

Рассмотрим функционирование устройства на примере обработки восьмираз- рядньк комплексньгх чисел (фиг.2),

Восьмиразрядные (0-7р) коды действительной и мнимой составляющих исходного комплексного числа с входов устройства поступают одновременно на входы коммутатора 1, выполненного на основе мультиплексоров из 2 в 1, блока 2 анализа величины исходного . числа, выполненного на основе ППЗУ с организацией 1024x1, и блока 3 ления .первой производной функции 3, вьшолненного на основе ППЗУ с организацией 1024x4, причем на блок 2 анализа величины исходного числа посту пают старшие (5-7р) разряды обеих составляющих исходного числа, а на блок 3 вычисления первой производной функции поступают 1-й и 2-й разряды обеих составляющих исходного комплексного числа, соответствующие величине ок- руглеиия dX ( Y), а также старшие (5-7р) разряды обеих составляющих исходного комплексного числа, соответствующие округленному значению Х (YP). Число используемых разрядов составляющих исходного комплексного числа определено разрядностью входов блока 3 вычисления первой производной функции.

В блоке 2 анализа величины исходного числа проводится сравнение обеих составляющих исходного комплексного числа с пороговым значением Z, равным для данного случая 32, и вырабатывается сигнал управления коммутатором 1, блоком 3 вычисления первой производной функции и блоком 4 вычисления начального значения функции, причем если обе составляющие исходного числа меньше порогового значения Z, то сигнал управления имеет низкий уровень, если хотя бы одна из составляю- щих равна или больше порогового значения, - высокий уровень. Одновре- . менно в блоке 3 вычисления первой производной функции проводится вычисление в соответствии с вьфажением (4) . Величина порогового значения определена разрядностью информационных входов блока 4 вычисления начального значения функции.

5 Если сигнал управления имеет низкий уровень, то через коммутатор 1. на вход блока 4 вычисления начального значения функции поступают полные значения составляющих исходного комп - .

лексного числа, занимающие в данном случае 0-4р, В противном случае на вход блока 4 вычисления начального значения функции поступают старшие (3-7р) разряды обеих составляющих

5 исходного комплексного числа, т.е. их округленные значения.

В блоке 4 вьтисления начального значения функции, выполненном на основе ППЗУ с организацией 2048x8, про0 исходит вычисление в соответствии с 1 выражением (3), если управляющий сигнал имеет низкий уровень, или (4), если высокий. Одновременно в блоке производится ограничение результата

вычисления до величины 255 , связанное с разрядностью выхода блока.

Разрядность информационных входов блока 4 вычисления начального значения функции (0-9р) определяет велиQ чину порогового значения Z для блока 2 анализа величины исходного числа таким образом, чтобы на каждую из составляющих приходилось по 5 разрядов (0-4р или 3-7р), что соответствует

с величине порогового значения . При этом старщий разряд входа блока 4 вычисления начального значения функции является входом управления ранного блока.

0

Полученные результаты начального

значения функции (8 разрядов) и первой производной функции (4 разряда) поступают на входы восьмиразрядного е двоичного с умматрра 5, с выхода которого снимается конечный результат вычислений в девятиразрядном коде (8 разрядов выхода сумматора и 1 разряд переполнения сумматора).

Формула изоб.ретени:я

Устройство для вычисления модуля комплексного числа, содержащее сумматор и коммутатор, отличающе-с е с я тем, что, с целью повьшения tO4HOCTH. вычисления, в него введены блок анализа величины исходного числа, блок вычисления первой производной функции и блок вычисления начально- Q значения функции, причем информа1ди- фнные входы коммутатора, блока анали- 9а величины исходного числа и блока $ьгчисления первой производной функщ ш (Соединены с информационными входами 15

устройства, выход блока анализа величины исходного числа подключен к . входам управления коммутатора, блока вычисления первой производной функции и блока вычисления начального значения функции, вьпсоды коммутатора подключены к информационным входам блока вычисления начального значения функции, выход которого и выход блока вычисления первой производной функции соединены соответственно с первым и вторым слагаемыми сумматора, выход которого является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования дуг и окружностей на экране телевизионного индикатора | 1990 |

|

SU1800476A1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для деления | 1986 |

|

SU1390608A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

Изобретение относится к вычислительной технике и может быть применено в цифровых вычислительных машинах, специализированных вычислительных устройствах, устройствах цифровой обработки сигналов и вычислительных средах, построенных на больших интегральных схемах. Цель изобретения - повышение точности вычисления модуля комплексного числа. Устройство для вычисления модуля комплексного числа содержит коммутатор 1, блок анализа 2 величины исходного числа, блок вычисления 3 первой производной функции, блок вычисления 4 начального значения функции, сумматор 5 с соответствующими связями. 2 ил.

1

гг

быхо

Авторы

Даты

1990-08-30—Публикация

1988-08-29—Подача