Изобретение относится к области вычислительной техники, в частности к устройствам сопряжения, и может быть использовано для программно-аппаратного вычисления булевых функций, зависящих от со- стояния большого количества дискретных датчиков.

Известно устройство, содержащее дешифратор адреса, два элемента И, элемент ИЛИ, шинный формирователь, регистр, группу элементов И, группу элементов И- НЕ.

Недостатком такого устройства является низкая производительность.

Наиболее близким по технической сущ- ности к предлагаемому является устройство, содержащее дешифратор адреса, шинный формирователь, пять элементов И, два элемента ИЛИ, два триггера, оперативную память, генератор, счетчик, группу эле- ментов-И с тремя состояниями на выходе, группу элементов И-НЕ с тремя состояниями на выходе, причем вход дешифратора адреса подключен к входу устройства для подключения шины адреса микроЭВМ, первый выход дешифратора адреса соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с входом выборки шинного формирователя, вход задания направления передачи которого и первый вход элемента ИЛИ соединены с входом устройства для подключения выхода команды ввода микро- ЭВМ, выход элемента ИЛИ соединен с вторым входом второго элемента И, второй вход элемента ИЛИ и второй вход третьего элемента И соединен с входом устройства для подключения команды вывода микро- ЭВМ, вход-выход шинного формирователя соединен с входом-выходом устройства для подключения входа-выхода данных микро- ЭВМ, вторые входы К-го (К 1,В, где В разрядность информационных входов устройства) элемента И с тремя состояниями на выходе группы и К-го элемента И-НЕ с тремя состояниями на выходе группы соединены с К-м разрядом входов для подключения дискретных сигналов, выходы К-го элемента И с тремя состояниями на выходе группы и К-го элемента И-НЕ с тремя состояниями на выходе группы соединены с К-м входом первого элемента И, нечетный выход оперативной памяти соединен с первым входом К-го элемента И с тремя состояниями на выходе группы, четный выход оперативной памяти соединен с первым входом К-го элемента И-НЕ с тремя состояниями на выходе группы, информационные входы оперативной памяти соединены с выходами шинного формирователя, вход управления записью оперативной памяти подключен к выходу третьего элемента И, подключенному также к первому входу второго элемента ИЛИ, вход выборки оперативной памяти подключен к отрицательной шине источника питания и постоянно активирован, адресные входы оперативной памяти подключены к информационным выходам счетчика, выход переполнения счетчика подключен к входу сброса первого триггера, второй выход дешифратора адреса подключен к первым входам четвертого и пятого элементов И, второй вход четвертого элемента И подключен к второму входу третьего элемента И, второй вход пятого элемента И подключен к первому входу первого элемента ИЛИ, а выход пятого элемента И подключен к входу установки первого триггера, выход которого подключен к входу управления генератора и к (В+1)-му входу первого элемента И, выход генератора подключен к второму входу второго элемента ИЛИ, выход которого подключен к счетному входу счетчика, выход первого элемента И подключей к входу установки второго триггера, выход четвертого элемента И подключен к входу сброса второго триггера, выход которого подключен к входу шинного формирователя.

Недостатком известного устройства является невозможность построения раз- рядонаращиваемых структур, низкое быстродействие и узкая область применения. Эти недостатки обусловлены следую- щими обстоятельствами. В прототипе отсутствуют технические средства, позволяющие получать разрядонаращиваемые устройства ввода (по аналогии с разрядонара- щиваемыми процессорами, контроллерами прерываний и пр.), что в условиях ограничений на количество выводов БИС таких устройств приводит к ограничению и на число информационных входов. В широком классе задач, требующем обработку большого количества дискретных сигналов (десятки, сотни), применение известного устройства для вычисления многоразрядных булевых функций заключается в поочередном вычислении подконьюнкций (необходимо не- сколько известных устройств, каждое из которых обрабатывает часть входного слова) с дальнейшим программным вычислением всей конъюнкции, а вычисление сразу всей многоразрядной функции невозмож- но. Такой характер вычислений значительно снижает быстродействие и сужает область применения известного устройства. Кроме того, в нем отсутствует возможность непосредственного (без предварительной обработки) ввода части разрядов с информационных входов в микроЭВМ.

Цель изобретения - повышение быстродействия и расширение области применения за счет возможности вычисления и ввода многоразрядных булевых функций.

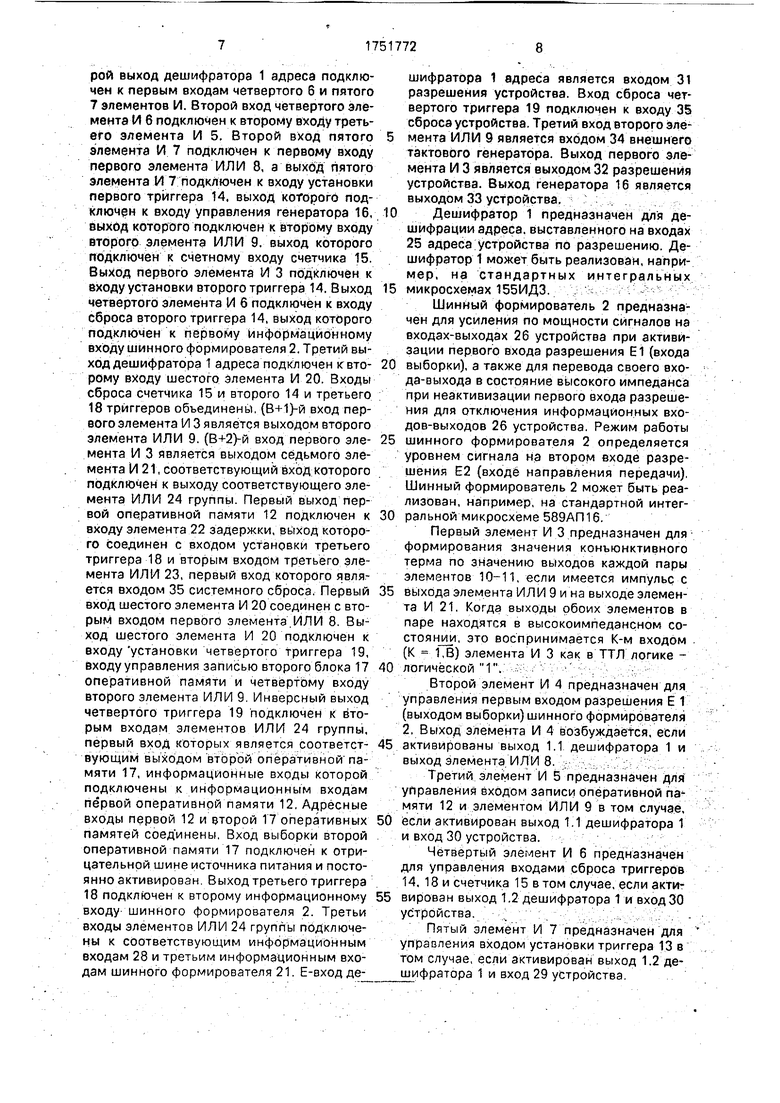

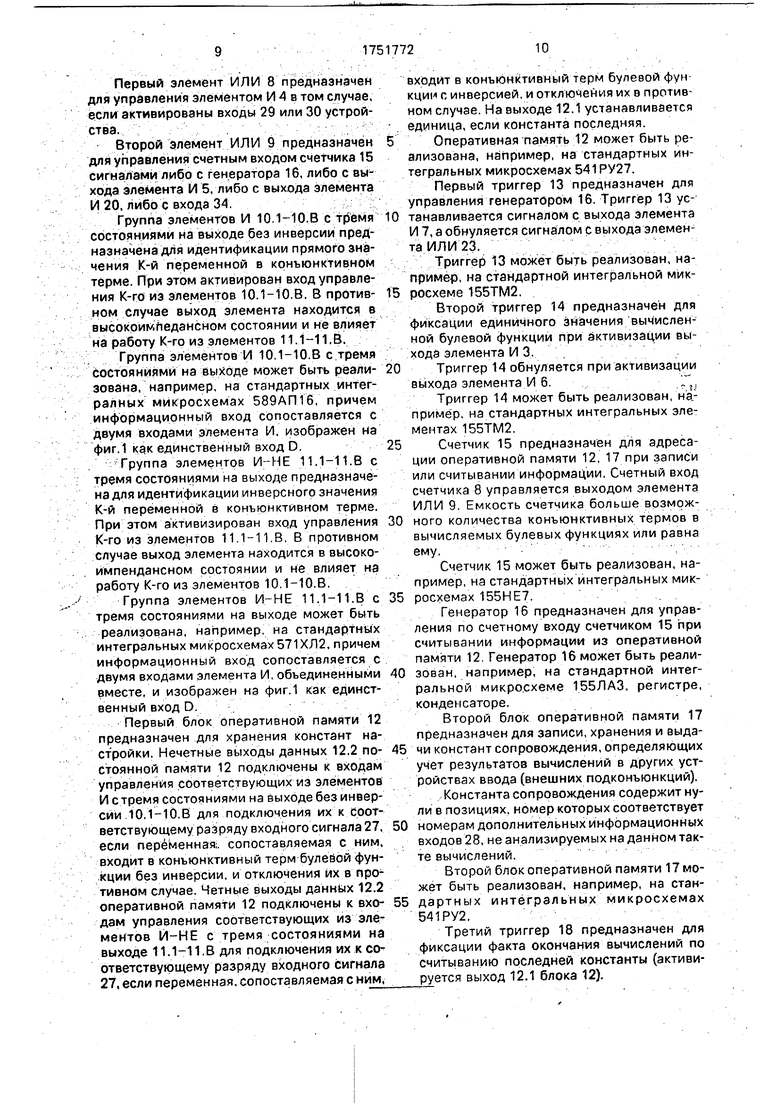

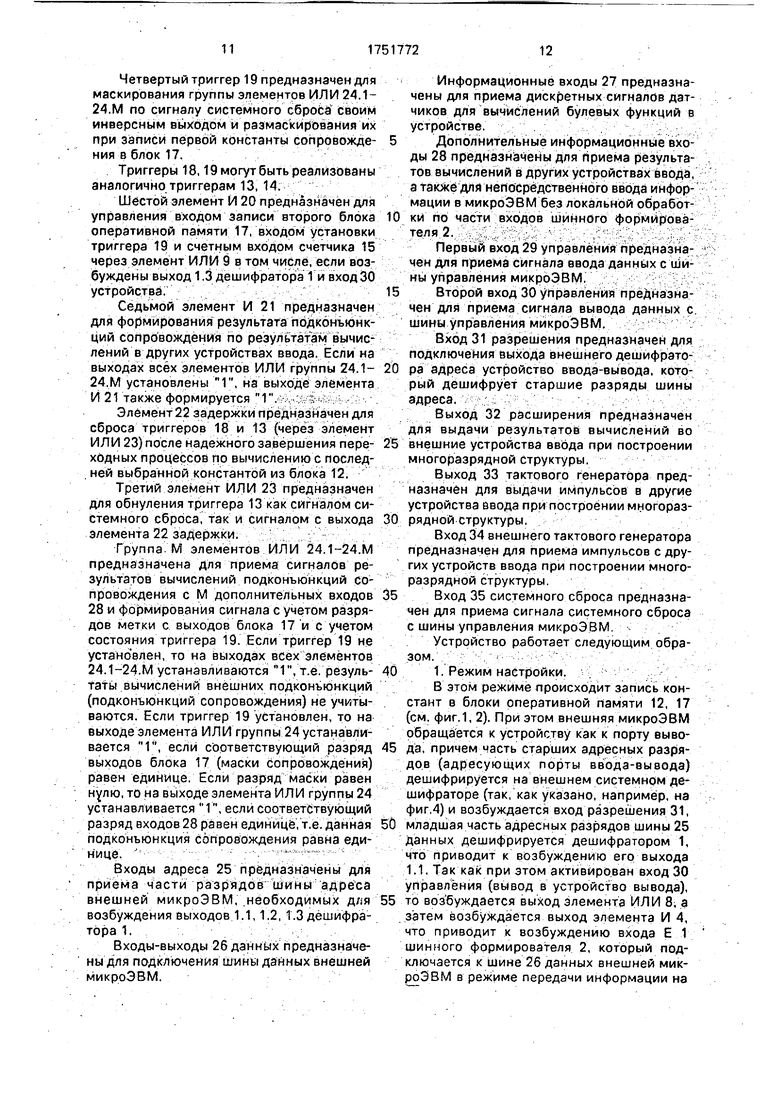

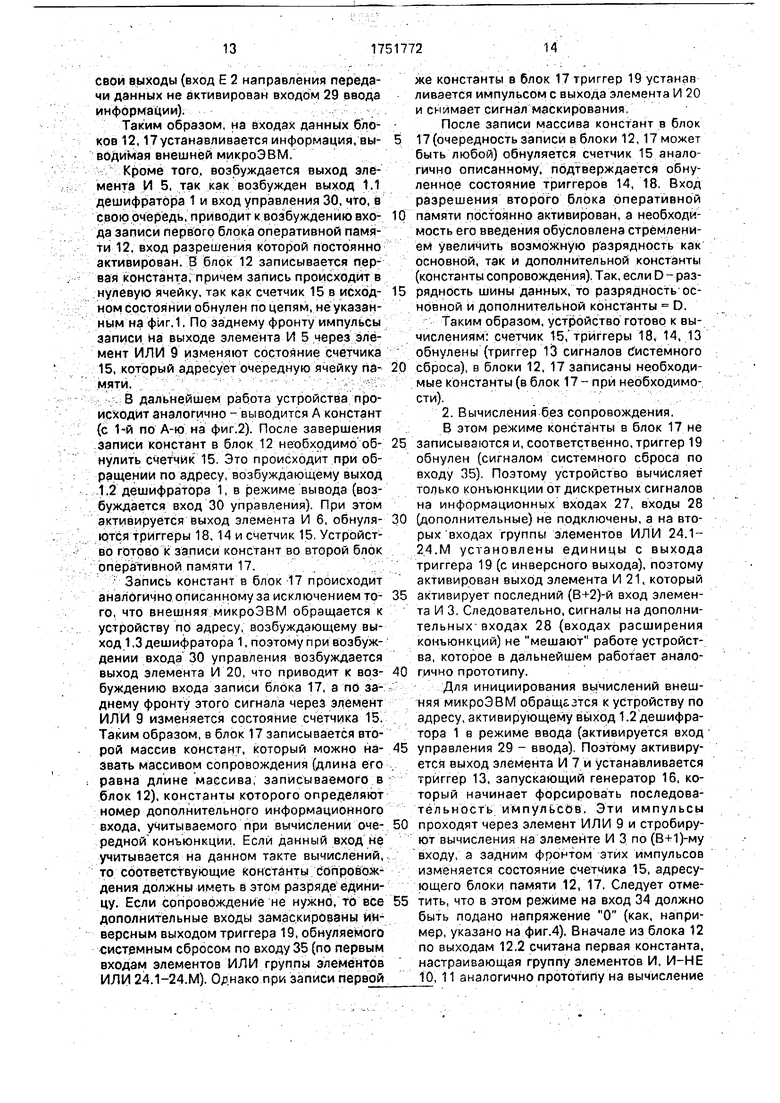

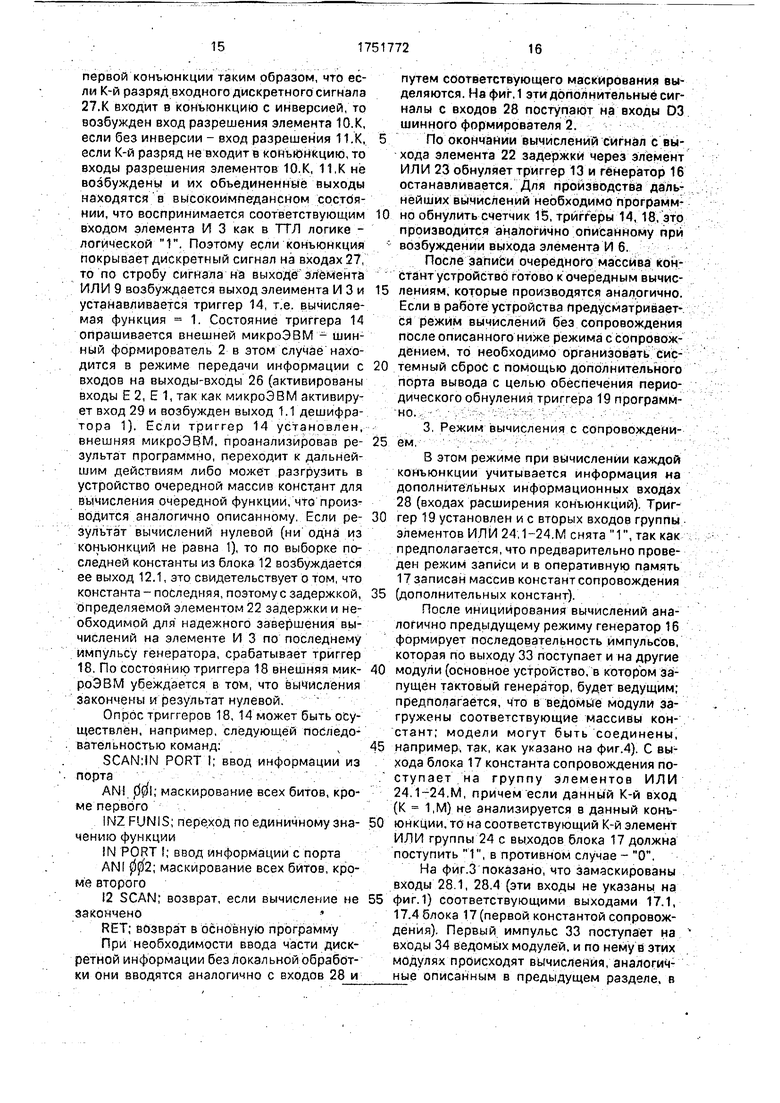

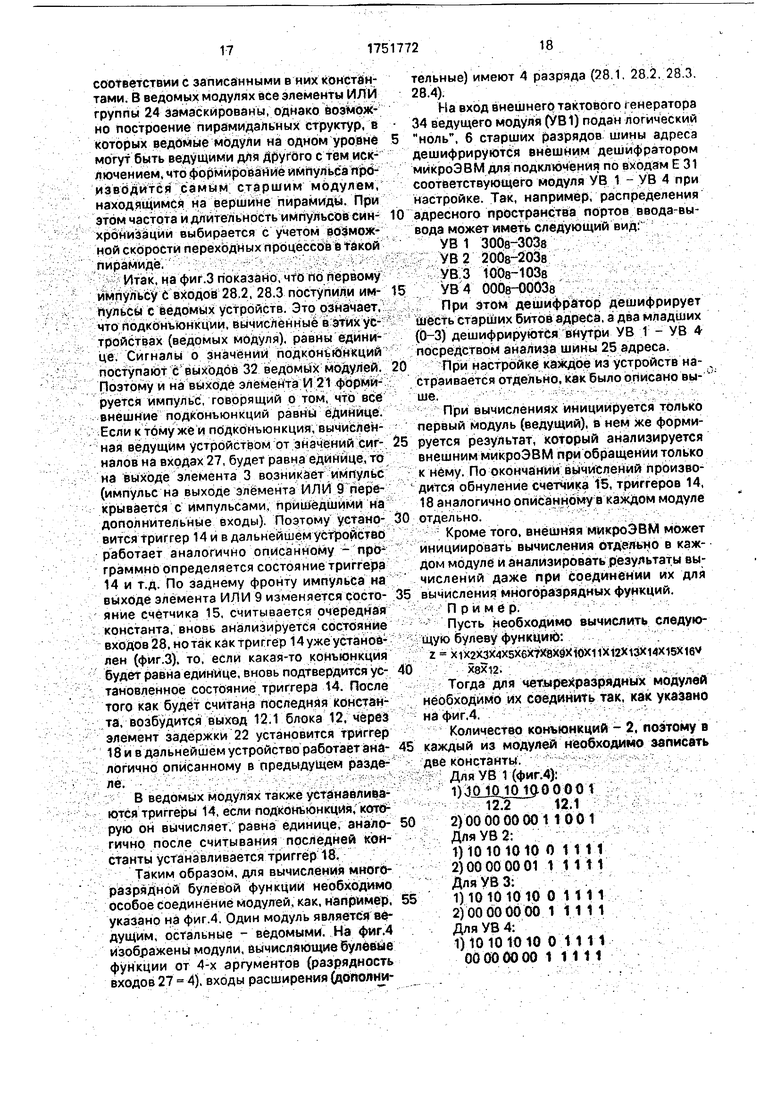

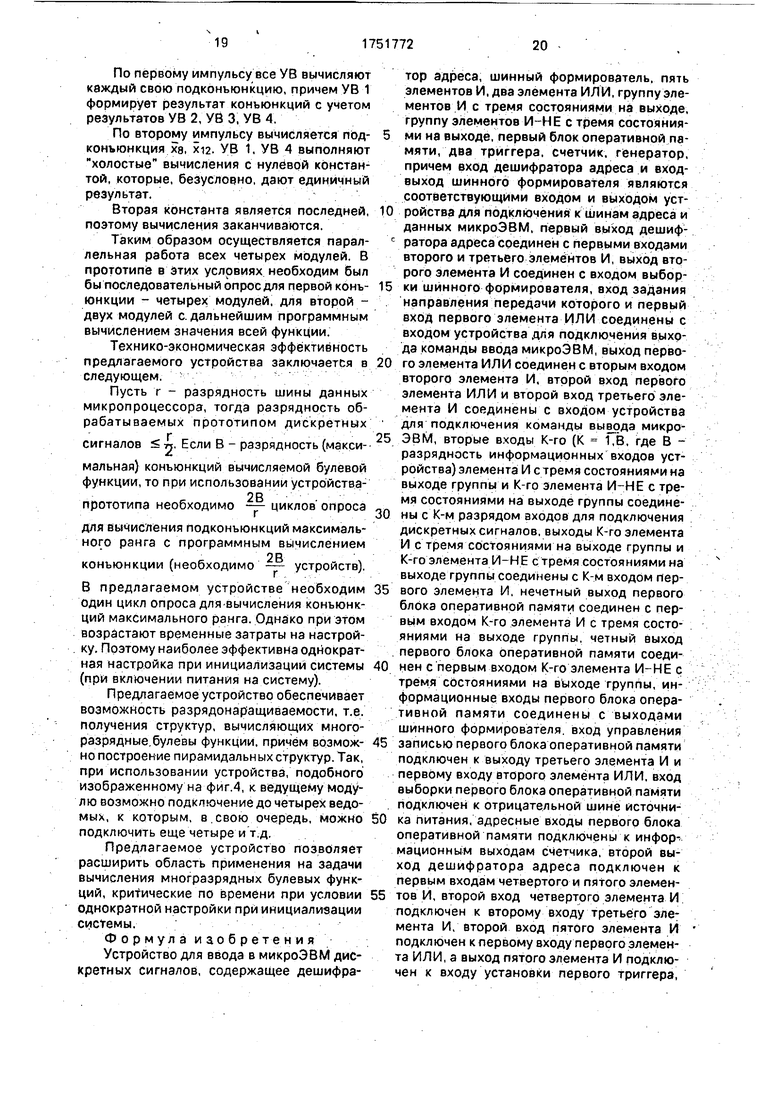

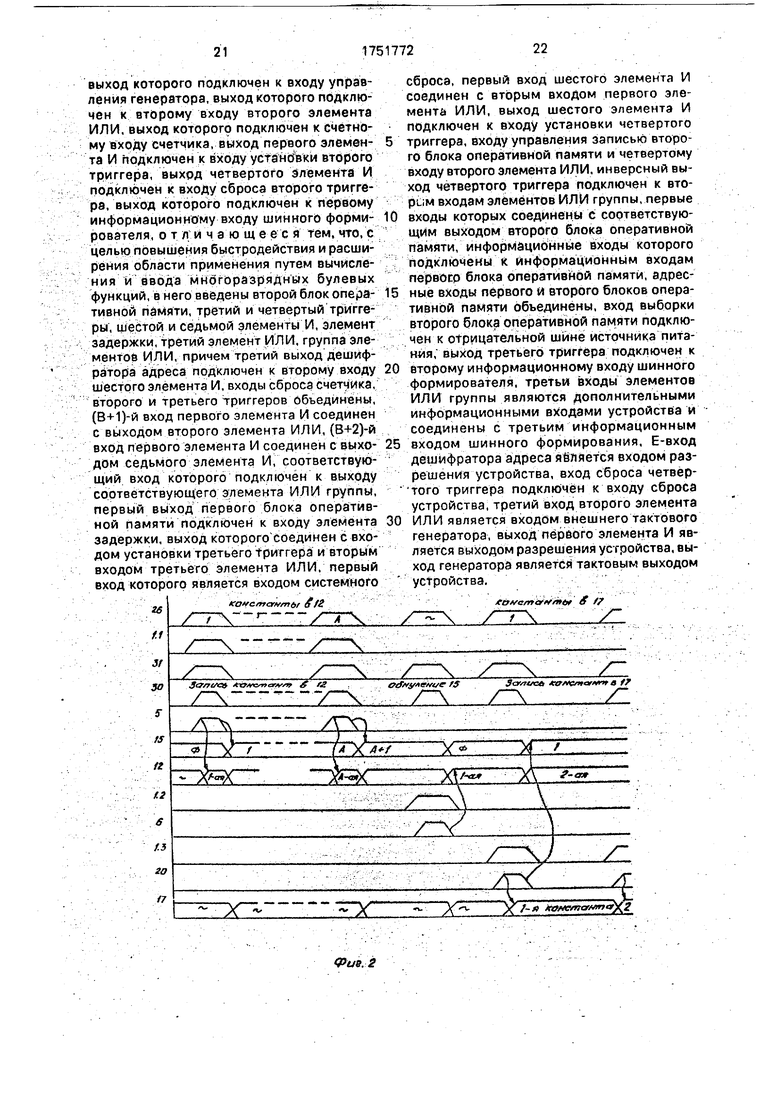

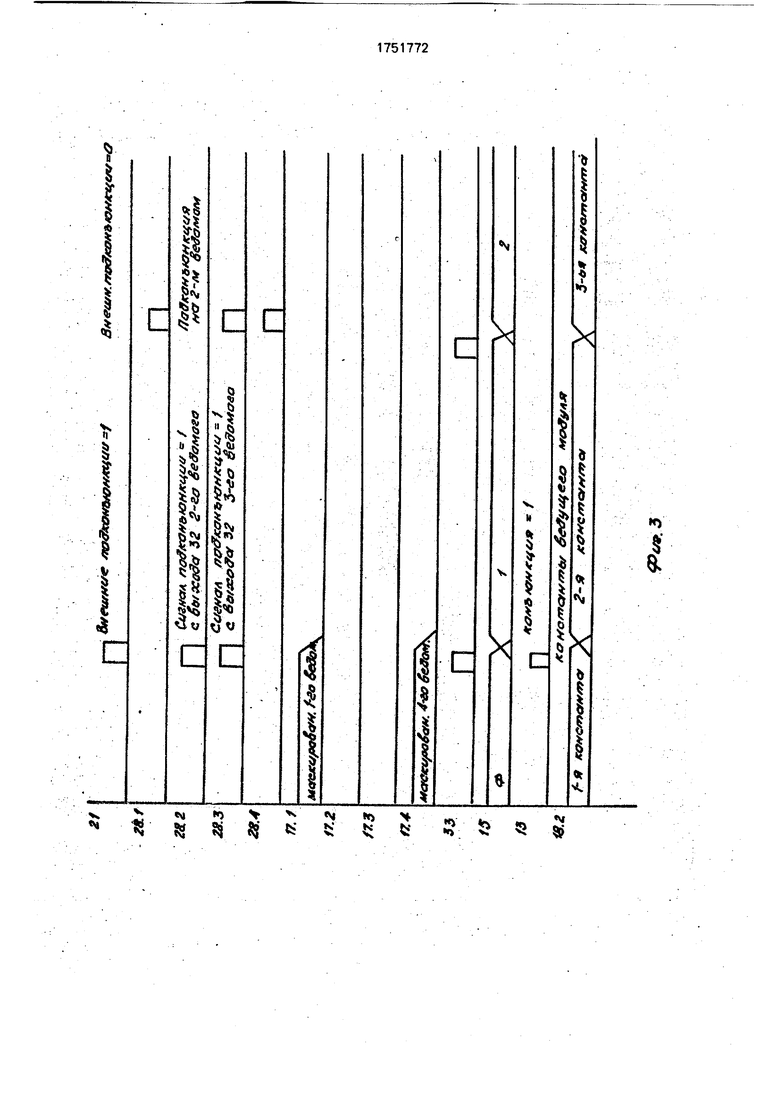

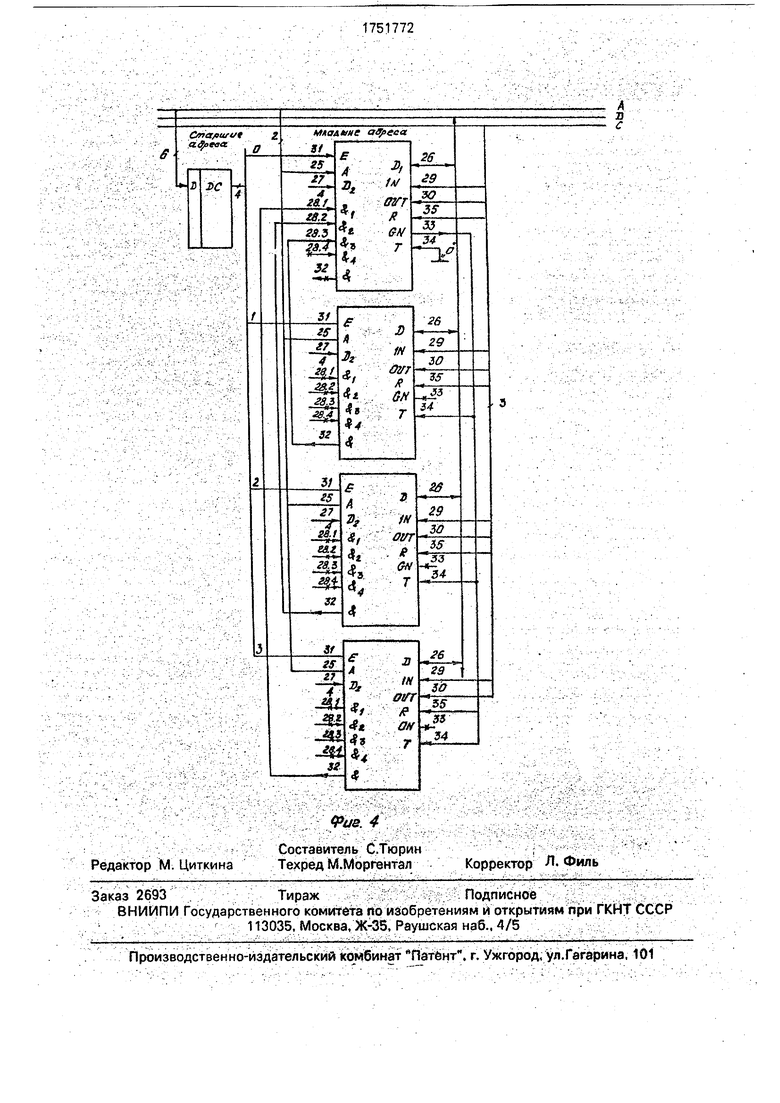

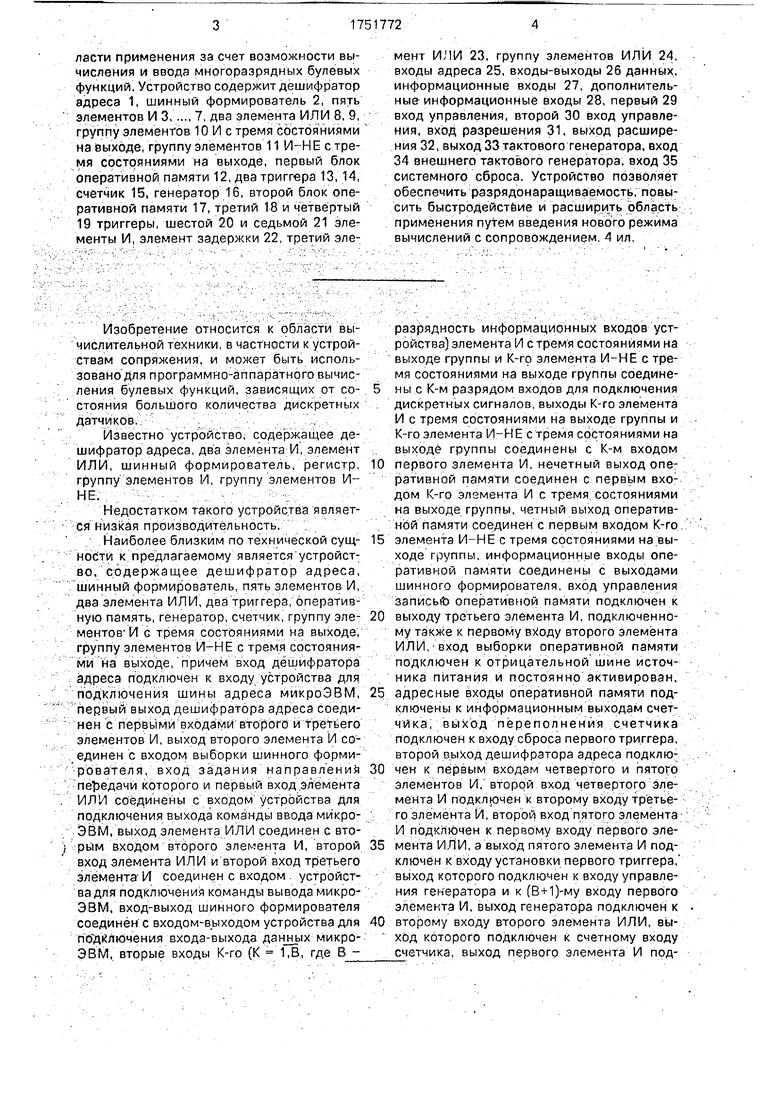

На фиг.1 изображена функциональная электрическая схема устройства для ввода в микроЭВМ дискретной информации; на фиг.2 - временная диаграмма работы уст- ройства в режиме настройки; на фиг.З - временная диаграмма работы устройства 6 режиме вычисления с сопротивлением; на фиг.4 - пример построения многоразрядной структуры с использованием в качестве мо- дуля данного устройства.

Устройство для ввода в микроЭВМ дискретных сигналов содержит дешифратор 1 адреса, шинный формирователь 2, пять элементов И 3-7, два элемента ИЛИ 8,9, группу элементов И 10.1-10.В с тремя состояниями на выходе, группу элементов И-НЕ 11.1- 11.В.с тремя состояниями на выходе, первый блок 12 оперативной памяти, два триггера 13, 14, счетчик 15, генератор 16,

второй блок 17 оперативной памяти, третий и четвертый триггеры 18, 19, шестой и седьмой элементы И 20, 21, элемент 22 задержки, третий элемент ИЛИ 23, группу элементов ИЛИ 24.1-24.И, входы адреса 25, входы-выходы данных 26, информационные входы 27, дополнительные информационные входы 28, первый вход 29 управления, второй вход 30 управления, вход 31 разрешения, выход 32 расширения, выход 33 тактового генератора, вход 34 внешнего тактового генератора, вход 35 системного сброса.

Вход 25 дешифратора 1 адреса и вход- выход 26 шинного формирователя 2 являются соответствующими входом и выходом устройства для подключения к шинам адреса и данных микроЭВМ. Первый выход дешифратора 1 адреса соединен с первыми входами второго 4 и третьего 5 элементов И Выход второго элемента И 4 соединен с входом выборки шинного формирователя 2, вход задания направления передачи которого и первый вход элемента ИЛИ 8 соединены с входом 29 устройства для подключения выхода команды ввода микро- ЭВМ. Выход элемента ИЛИ 8 соединен с вторым входом второго элемента И 4. Второй вход элемента ИЛИ 8 и второй вход третьего элемента И 5 соединены с входом 30 устройства для подключения команды вывода микроЭВМ. Вторые входы К-ro (К 1.В, где В - разрядность информационных входов устройства) элемента И 10 с тремя состояниями на выходе группы и К-го элемента И-НЕ 11с тремя состояниями на выходе группы соединены с К-м разрядом входов 27 для подключений дискретных сигналов. Выходы К-ro элемента И 10 с тремя состояниями на выходе группы и К-ro элемента И-НЕ 11с тремя состояниями на выходе группы соединены с К-м входом первого элемента И 3. Нечетный выход 12 оперативной памяти соединен с первым входом К-ro элемента И 10 с тремя состояниями на выходе группы, четный выход оперативной памяти 12 соединен с первым входом К-го элемента И-НЕ с тремя состояниями на выходе группы, Информационные входы оперативной памяти 12 соединены с выходами шинного формирователя 2. Вход управления записью оперативной памяти 12 подключен к выходу третьего элемента И 5, подключенного также к первому входу второго элемента ИЛИ 9. Вход выборки оперативной памяти 12 подключен к отрицательной шине источника питания и постоянно активирован. Адресные входы оперативной памяти 12 подключены к информационным выходам счетчика 15. Второй выход дешифратора 1 адреса подключен к первым входам четвертого б и пятого 7 элементов И. Второй вход четвертого элемента И б подключен к второму входу третьего элемента И 5. Второй вход пятого элемента И 7 подключен к первому входу первого элемента ИЛИ 8, а выход пятого элемента И 7 подключен к входу установки первого триггера 14. выход которого подключен к входу управления генератора 16, выход которого подключен к второму входу второго элемента ИЛИ 9. выход которого подключен к счетному входу счетчика 15. Выход первого элемента И 3 подключен к входу установки второго триггера 14. Выход четвертого элемента И 6 подключен к входу сброса второго триггера 14, выход которого подключен к первому Информационному входу шинного формирователя 2. Третий выход дешифратора 1 адреса подключен к второму входу шестого элемента И 20. Входы сброса счетчика 15 и второго 14 и третьего 18 триггеров объединены, (В+1)-й вход первого элемента И 3 является выходом второго элемента ИЛИ 9. (В+2)-й вход первого элемента И 3 является выходом седьмого элемента И 21, соответствующий вход которого подключен к выходу соответствующего элемента ИЛИ 24 группы. Первый выход первой оперативной памяти 12 подключен к входу элемента 22 задержки, выход которого соединен с входом установки третьего триггера 18 и вторым входом третьего элемента ИЛИ 23, первый вход которого является входом 35 системного сброса. Первый вход шестого элемента И 20 соединен с вторым входом первого элемента ИЛИ 8. Выход шестого элемента И 20 подключен к входу установки четвертого триггера 19, входу управления записью второго блока 17 оперативной памяти и четвертому входу второго элемента ИЛИ 9 Инверсный выход четвертого триггера 19 подключен к вторым входам элементов ИЛИ 24 группы, первый вход которых является соответствующим выходом второй оперативной памяти 17, информационные входы которой подключены к информационным входам первой оперативной памяти 12. Адресные входы первой 12 и второй 17 оперативных памятей соединены, Вход выборки второй оперативной памяти 17 подключен к отрицательной шине источника питания и постоянно активирован Выход третьего триггера 18 подключен к второму информационному входу шинного формирователя 2. Третьи входы элементов ИЛИ 24 группы подключены к соответствующим информационным входам 28 и третьим информационным входам шинного формирователя 21. Е-вход дешифратора 1 адреса является входом 31 разрешения устройства. Вход сброса четвертого триггера 19 подключен к входу 35 сброса устройства. Третий вход второго элемента ИЛИ 9 является входом 34 внешнего тактового генератора. Выход первого элемента И 3 является выходом 32 разрешения устройства. Выход генератора 16 является выходом 33 устройства,

0 Дешифратор 1 предназначен для дешифрации адреса, выставленного на входах 25 адреса устройства по разрешению. Дешифратор 1 может быть реализован, например, на стандартных интегральных

5 микросхемах 155ИДЗ.

Шинный формирователь 2 предназначен для усиления по мощности сигналов на входах-выходах 26 устройства при активизации первого входа разрешения Е1 (входа

0 выборки), а также для перевода своего входа-выхода в состояние высокого импеданса при неактивизации первого входа разрешения для отключения информационных входов-выходов 26 устройства. Режим работы

5 шинного формирователя 2 определяется уровнем сигнала на втором входе разрешения Е2 (входе направления передачи), Шинный формирователь 2 может быть реализован, например, на стандартной интег0 ральной микросхеме 589АП16.

Первый элемент И 3 предназначен для формирования значения конъюнктивного терма по значению выходов каждой пары элементов 10-11, если имеется импульс с

5 выхода элемента ИЛИ 9 и на выходе элемента И 21. Когда выходы обоих элементов в паре находятся в высокоимпедансном состоянии, это воспринимается К-м входом (К 1,В) элемента И 3 как в ТТЛ логике 0 логической 1.

Второй элемент И 4 предназначен для управления первым входом разрешения Е 1 (выходом выборки) шинного формирователя 2, Выход элемента И 4 возбуждается, если

5 активированы выход 1.1 дешифратора 1 и выход элемента ИЛИ 8.

Третий элемент И 5 предназначен для управления входом записи оперативной памяти 12 и элементом ИЛИ 9 в том случае.

0 если активирован выход 1.1 дешифратора 1 и вход 30 устройства.

Четвертый элемент И б предназначен для управления входами сброса триггеров 14. 18 и счетчика 15 в том случае, если акти5 вирован выход 1.2 дешифратора 1 и вход 30 устройства.

Пятый элемент И 7 предназначен для управления входом установки триггера 13 в том случае, если активирован выход 1.2 дешифратора 1 и вход 29 устройства

Первый элемент ИЛИ 8 предназначен для управления элементом И 4 в том случае, если активированы входы 29 или 30 устройства.

Второй элемент ИЛИ 9 предназначен для управления счетным входом счетчика 15 сигналами либо с генератора 16, либо с выхода элемента И 5, либо с выхода элемента И 20, либо с входа 34.

Группа элементов И 10.1-10.В с тремя состояниями на выходе без инверсии предназначена для идентификации прямого значения К-й переменной в конъюнктивном терме. При этом активирован вход управления К-ro из элементов 10.1-10.В. В против- ном случае выход элемента находится в высокоикпедансном состоянии и не влияет на работу К-го из элементов 11.1-11.В.

Группа элементов И 10.1-10.В с тремя состояниями на выходе может быть реали- зованэ, например, на стандартных интег- ралных микросхемах 589АП16, причем информационный вход сопоставляется с двумя входами элемента И. изображен на фиг.1 как единственный входО.

Группа элементов И--НЕ 11.1-11.В с тремя состояниями на выходе предназначена для идентификации инверсного значения К-й переменной в конъюнктивном терме. При этом активизирован вход управления К-го из элементов 11.1-11.В. В противном случае выход элемента находится в высоко- импендансном состоянии и не влияет на работу К-го из элементов 10.1-10.В,

Группа элементов И-НЕ 11.1-11.В с тремя состояниями на выходе может быть реализована, например, на стандартных интегральных микросхемах 571ХЛ2, причем информационный вход сопоставляется с двумя входами элемента И. объединенными вместе, и изображен на фиг.1 как единственный вход D.

Первый блок оперативной памяти 12 предназначен для хранения констант настройки. Нечетные выходы данных 12.2 по- стоянной памяти 12 подключены к входам управления соответствующих из элементов И стремя состояниями на выходе без инверсии 10.1-10.В для подключения их к соответствующему разряду входного сигнала 27, если переменная,, сопоставляемая с ним, входит в конъюнктивный терм булевой функции без инверсии, и отключения их в противном случае. Четные выходы данных 12.2 оперативной памяти 12 подключены к вхо- дам управления соответствующих из элементов И-НЕ с тремя состояниями на выходе 11.1-11.В для подключения их к соответствующему разряду входного сигнала 27, если переменная, сопоставляемая с ним.

входит в конъюнктивный терм булевой фун кцим с инверсией, и отключения их в противном случае. На выходе 12.1 устанавливается единица, если константа последняя.

Оперативная память 12 может быть реализована, например, на стандартных интегральных микросхемах 541РУ27.

Первый триггер 13 предназначен для управления генератором 16. Триггер 13 устанавливается сигналом с выхода элемента И 7, а обнуляется сигналом с выхода элемента ИЛИ 23.

Триггер 13 может быть реализован, например, на стандартной интегральной микросхеме 155ТМ2.

Второй триггер 14 предназначен для фиксации единичного значения вычисленной булевой функции при активизации выхода элемента И 3.

Триггер 14 обнуляется при активизации выхода элемента И б.

Триггер 14 может быть реализован, например, на стандартных интегральных элементах 155ТМ2.

Счетчик 15 предназначен для адресации оперативной памяти 12, 17 при записи или считывании информации. Счетный вход счетчика 8 управляется выходом элемента ИЛИ 9. Емкость счетчика больше возможного количества конъюнктивных термов в вычисляемых булевых функциях или равна ему.

Счетчик 15 может быть реализован, например, на стандартных интегральных микросхемах 155НЕ7.

Генератор 16 предназначен для управления по счетному входу счетчиком 15 при считывании информации из оперативной памяти 12 Генератор 16 может быть реализован, например, на стандартной интегральной микросхеме 155ЛАЗ, регистре, конденсаторе.

Второй блок оперативной памяти 17 предназначен для записи, хранения и выдачи констант сопровождения, определяющих учет результатов вычислений в других устройствах ввода (внешних подконъюнкций).

Константа сопровождения содержит нули в позициях, номер которых соответствует номерам дополнительных информационных входов 28, не анализируемых на данном такте вычислений.

Второй блок оперативной памяти Сможет быть реализован, например, на стандартных интегральных микросхемах 541РУ2.

Третий триггер 18 предназначен для фиксации факта окончания вычислений по считыванию последней константы (активируется выход 12.1 блока 12).

Четвертый триггер 19 предназначен для маскирования группы элементов ИЛИ 24.1- 24.М по сигналу системного сброса своим инверсным выходом и размаскирования их при записи первой константы сопровождения в блок 17.

Триггеры 18,19 могут быть реализованы аналогично триггерам 13,14.

Шестой элемент И 20 предназначен для управления входом записи второго блока оперативной памяти 17, входом установки триггера 19 и счетным входом счетчика 15 через элемент ИЛИ 9 в том числе, если возбуждены выход 1.3 дешифратора 1 и вход 30 устройства.

Седьмой элемент И 21 предназначен для формирования результата подконъюнк- ций сопровождения по результатам вычислений в других устройствах ввода. Если на выходах всех элементов ИЛИ группы 24.1- 24.М установлены 1, на выходе элемента И 21 также формируется 1.

Элемент 22 задержки предназначен для сброса триггеров 18 и 13 (через элемент ИЛИ 23) после надежного завершения переходных процессов по вычислению с последней выбранной константой из блока 12.

Третий элемент ИЛИ 23 предназначен для обнуления триггера 13 как сигналом системного сброса, так и сигналом с выхода элемента 22 задержки.

Группа М элементов ИЛИ 24.1-24.М предназначена для приема сигналов результатов вычислений подконъюнкций сопровождения с М дополнительных входов 28 и формирования сигнала с учетом разрядов метки с выходов блока 17 и с учетом состояния триггера 19. Если триггер 19 не установлен, то на выходах всех элементов 24.1-24.М устанавливаются 1, т.е. результаты вычислений внешних подконъюнкций (подконъюнкций сопровождения) не учитываются. Если триггер 19 установлен, то на выходе элемента ИЛИ группы 24 устанавливается 1, если соответствующий разряд выходов блока 17 (маски сопровождения) равен единице. Если разряд маски равен нулю, то на выходе элемента ИЛИ группы 24 устанавливается 1, если соответствующий разряд входов 28 равен единице, т.е. данная подконъюнкция сопровождения равна единице. J

Входы адреса 25 предназначены для приема части разрядов шины адреса внешней микроЭВМ, необходимых для возбуждения выходов 1.1,1.2, 1.3 дешифратора 1,

Входы-выходы 26 данных предназначены для подключения шины данных внешней микроЭВМ.

Информационные входы 27 предназначены для приема дискретных сигналов датчиков для вычислений булевых функций в устройстве.

Дополнительные информационные входы 28 предназначены для приема результатов вычислений в других устройствах ввода, а также для непосредственного ввода информации в микроЭВМ без локальной обработ0 ки по части входов шинного формирователя 2.

Первый вход 29 управления предназначен для приема сигнала ввода данных с шины управления микроЭВМ,

5 Второй вход 30 управления предназначен для приема сигнала вывода данных с шины управления микроЭВМ.

Вход 31 разрешения предназначен для подключения выхода внешнего дешифрато0 ра адреса устройство ввода-вывода, который дешифрует старшие разряды шины адреса.

Выход 32 расширения предназначен для выдачи результатов вычислений во

5 внешние устройства ввода при построении многоразрядной структуры.

Выход 33 тактового генератора предназначен для выдачи импульсов в другие устройства ввода при построении многораз0 рядной структуры.

Вход 34 внешнего тактового генератора предназначен для приема импульсов с других устройств ввода при построении многоразрядной структуры

5 Вход 35 системного сброса предназначен для приема сигнала системного сброса с шины управления микроЭВМ

Устройство работает следующим образом.

0 1. Режим настройки.

В этом режиме происходит запись констант в блоки оперативной памяти 12, 17 (см. фиг.1, 2). При этом внешняя микроЭВМ обращается к устройству как к порту выво5 да, причем асть старших адресных разрядов (адресующих порты ввода-вывода) дешифрируется на внешнем системном дешифраторе (так, как указано, например, на фиг.4) и возбуждается вход разрешения 31,

0 младшая часть адресных разрядов шины 25 данных дешифрируется дешифратором 1, что приводит к возбуждению его выхода 1.1, Так как при этом активирован вход 30 управления (вывод в устройство вывода),

5 то возбуждается выход элемента ИЛИ 8, а затем возбуждается выход элемента И 4, что приводит к возбуждению входа Е 1 шинного формирователя 2, который подключается к шине 26 данных внешней микроЭВМ в режиме передачи информации на

свои выходы (вход Е 2 направления передачи данных не активирован входом 29 ввода информации).

Таким образом, на входах данных блоков 12,17 устанавливается информация, выводимая внешней микроэвм.

Кроме того, возбуждается выход элемента И 5, так как возбужден выход 1.1 дешифратора 1 и вход управления 30, что, в свою очередь, приводит к возбуждению входа записи первого блока оперативной памяти 12, вход разрешения которой постоянно активирован. В блок 12 записывается первая константа, причем запись происходит в нулевую ячейку, так как счетчик 15 в исходном состоянии обнулен по цепям, не указанным на фиг.1. По заднему фронту импульсы записи на выходе элемента И 5 через элемент ИЛИ 9 изменяют состояние счетчика 15, который адресует очередную ячейку памяти.

В дальнейшем работа устройства происходит аналогично - выводится А констант (с 1-й по А-ю на фиг.2). После завершения Записи констант в блок 12 необходимо обнулить счетчик 15 Это происходит при обращении по адресу, возбуждающему выход 1.2 дешифратора 1, в режиме вывода (возбуждается вход 30 управления). При этом активируется выход элемента И б, обнуляются триггеры 18, 14 и счетчик 15 Устройство готово к записи констант во второй блок оперативной памяти 17.

Запись констант в блок 17 происходит аналогично описанному за исключением того, что внешняя микроЭВМ обращается к устройству по адресу, возбуждающему выход 1.3 дешифратора 1, поэтому при возбуждении входа 30 управления возбуждается выход элемента И 20, что приводит к возбуждению входа записи блока 17, а по заднему фронту этого сигнала через элемент ИЛИ 9 изменяется состояние счетчика 15. Таким образом, в блок 17 записывается второй массив констант, который можно назвать массивом сопровождения (длина его равна длине массива, записываемого в блок 12), константы которого определяют номер дополнительного информационного входа, учитываемого при вычислении очередной конъюнкции. Если данный вход не учитывается на данном такте вычислений, то соответствующие константы Сопровождения должны иметь в этом разряде единицу. Если сопровождение не нужно, то все дополнительные входы замаскированы инверсным выходом триггера 19, обнуляемого системным сбросом по входу 35 (по первым входам элементов ИЛИ группы элементов ИЛИ 24.1-24.М). Однако при записи первой

же константы в блок 17 триггер 19 устанав ливается импульсом с выхода элемента И 20 и снимает сигнал маскирования

После записи массива констант в блок

17 (очередность записи в блоки 12,17 может быть любой) обнуляется счетчик 15 аналогично описанному, подтверждается обнуленное состояние триггеров 14, 18. Вход разрешения второго блока оперативной

0 памяти постоянно активирован, а необходимость его введения обусловлена стремлением увеличить возможную разрядность как основной, так и дополнительной константы (константы сопровождения) Так, если D - раз5 рядность шины данных, то разрядность основной и дополнительной константы D.

Таким образом, устройство готово к вычислениям: счетчик 15, триггеры 18, 14, 13 обнулены (триггер 13 сигналов Системного

0 сброса), в блоки 12.17 записаны необходимые константы (в блок 17 - при необходимости)

2. Вычисления без сопровождения. В этом режиме константы в блок 17 не

5 записываются и, соответственно, триггер 19 обнулен (сигналом системного сброса по входу 35) Поэтому устройство вычисляет только конъюнкции от дискретных сигналов на информационных входах 27, входы 28

0 (дополнительные) не подключены, а на вторых входах группы элементов ИЛИ 24.1- 24.М установлены единицы с выхода триггера 19 (с инверсного выхода), поэтому активирован выход элемента И 21, который

5 активирует последний (В+2)-й вход элемента И 3 Следовательно, сигналы на дополнительных входах 28 (входах расширения конъюнкций) не мешают работе устройства, которое в дальнейшем работает анало0 гично прототипу.

Для инициирования вычислений внешняя микроЭВМ обращгзтся к устройству по адресу, активирующему выход 1.2 дешифратора 1 в режиме ввода (активируется вход

5 управления 29 - ввода) Поэтому активируется выход элемента И 7 и устанавливается триггер 13, запускающий генератор 16, который начинает форсировать последовательность импульсов. Эти импульсы

0 проходят через элемент ИЛИ 9 и стробиру- ют вычисления на элементе И 3 по (В+1)-му входу, а задним фронтом этих импульсов изменяется состояние счетчика 15, адресующего блоки памяти 12, 17. Следует отме5 тить, что в этом режиме на вход 34 должно быть подано напряжение О (как, например, указано на фиг.4). Вначале из блока 12 по выходам 12.2 считана первая константа, настраивающая группу элементов И, И-НЕ 10, 11 аналогично прототипу на вычисление

первой конъюнкции таким образом, что если К-й разряд входного дискретного сигнала 27.К входит в конъюнкцию с инверсией, то возбужден вход разрешения элемента 10.К, если без инверсии - вход разрешения 11.К, если К-й разряд не входит в конъюнкцию, то входы разрешения элементов 10. К, 11, К не возбуждены и их объединенные выходы находятся в высокоимпедансном состоянии, что воспринимается соответствующим входом элемента И 3 как в ТТЛ логике - логической 1. Поэтому если конъюнкция покрывает дискретный сигнал на входах 27, то по стробу сигнала на выходе элемента ИЛИ 9 возбуждается выход элеимента I/I 3 и устанавливается триггер 14, т.е. вычисляемая функция 1. Состояние триггера 14 опрашивается внешней микроЭВМ - шинный формирователь 2 в этом случае находится в режиме передачи информации с входов на выходы-входы 26 (активированы входы Е 2, Е 1, так как микроЭВМ активирует вход 29 и возбужден выход 1.1 дешифратора 1). Если триггер 14 установлен, внешняя микроЭВМ, проанализировав результат программно, переходит к дальнейшим действиям либо может разгрузить в устройство очередной массив констант для вычисления очередной функции, что производится аналогично описанному. Если результат вычислений нулевой (ни одна из конъюнкций не равна 1), то по выборке последней константы из блока 12 возбуждается ее выход 12.1, это свидетельствует о том, что константа - последняя, поэтому с задержкой, определяемой элементом 22 задержки и необходимой для надежного завершения вычислений на элементе И 3 по последнему импульсу генератора, срабатывает триггер 18. По состоянию триггера 18 внешняя микроЭВМ убеждается в том, что вычисления закончены и результат нулевой.

Опрос триггеров 18, 14 может быть осуществлен, например, следующей последовательностью команд:

SCANilN PORT I; ввод информации из порта

AN 0$l; маскирование всех битов, кроме первого

INZ FUNIS; переход по единичному значению функции

IN PORT ; ввод информации с порта

ANI 002; маскирование всех битов, кроме второго

12 SCAN; возврат, если вычисление не закончено

RET; возврат в основную программу

При необходимости ввода части дискретной информации без локал ьной обработки они вводятся аналогично с входов 28 и

путем соответствующего маскирования выделяются. Нафиг,1 эти дополнительные сигналы с входов 28 поступают на входы D3 шинного формирователя 2.

По окончании вычислений сигнал с выхода элемента 22 задержки через элемент ИЛИ 23 обнуляет триггер 13 и генератор 16 останавливается. Для производства дальнейших вычислений необходимо программ0 но обнулить счетчик 15, триггеры 14, 18, это производится аналогично описанному при возбуждении выхода элемента И 6.

После записи очередного массива констант устройство готово к очередным вычис5 лениям, которые производятся аналогично. Если в работе устройства предусматривается режим вычислений без сопровождения после описанного ниже режима с сопровождением, то необходимо организовать сис0 темный сброс с помощью дополнительного порта вывода с целью обеспечения периодического обнуления триггера 19 программно.

3. Режим вычисления с сопровождени5 ем

В этом режиме при вычислении каждой конъюнкции учитывается информация на дополнительных информационных входах 28 (входах расширения конъюнкций). Триг0 гер 19 установлен и с вторых входов группы элементов ИЛИ 24,1-24.М снята 1, так как предполагается, что предварительно проведен режим записи и в оперативную память 17 записан массив констант сопровождения

5 (дополнительных констант).

После инициирования вычислений аналогично предыдущему режиму генератор 16 формирует последовательность импульсов, которая по выходу 33 поступает и на другие

0 модули (основное устройство, в котором запущен тактовый генератор, будет ведущим; предполагается, что в ведомые модули загружены соответствующие массивы констант; модели могут быть соединены,

5 например, так, как указано на фиг.4). С выхода блока 17 константа сопровождения поступает на группу элементов ИЛИ 24.1-24.М, причем если данный К-й вход (К 1,М) не анализируется в данный конъ0 юнкции, то на соответствующий К-й элемент ИЛИ группы 24 с выходов блока 17 должна поступить 1, в противном случае - О.

На фиг.З показано, что замаскированы входы 28 1, 28.4 (эти входы не указаны на

5 фиг. 1) соответствующими выходами 17.1, 17.4 блока 17 (первой константой сопровождения). Первый импульс 33 поступает на ч входы 34 ведомых модулей, и по нему в этих модулях происходят вычисления, аналогичные описанным в предыдущем разделе, в

соответствии с записанными в них константами. В ведомых модулях все элементы ИЛИ группы 24 замаскированы, однако возможно построение пирамидальных структур, е которых ведомые модули на одном уровне могут быть ведущими для другого с тем исключением, что формирование импульса производится самым старшим модулем, находящимся на вершине пирамиды. При этом частота и длительность импульсов синхронизации выбирается с учетом возможной скорости переходных процессов в такой пирамиде.

Итак, на фиг.З показано, что по первому импульсу с входов 28.2, 28.3 поступили импульсы с ведомых устройств. Это означает, что подконъюнкции, вычисленные в этих устройствах (ведомых модуля), равны единице. Сигналы о значении подконъюнкций поступают с выходов 32 ведомых модулей. Поэтому и на выходе элемента И 21 формируется импульс, говорящий о том, что все внешние подконъюнкции равны единице. Если к тому же и подконъюнкция, вычисленная ведущим устройством от значений сигналов на входах 27, будет равна единице, то на выходе элемента 3 возникает импульс (импульс на выходе элемента ИЛИ 9 перекрывается с импульсами, пришедшими на дополнительные входы). Поэтому установится триггер 14 и в дальнейшем устройство работает аналогично описанному - программно определяется состояние триггера 14 и т.д. По заднему фронту импульса на выходе элемента ИЛИ 9 изменяется состояние счетчика 15, считывается очередная константа, вновь анализируется состояние входов 28, нотак как триггер 14 уже установлен (фиг.З), то, если какая-то конъюнкция будет равна единице, вновь подтвердится установленное состояние триггера t4. После того как будет считана последняя константа, возбудится выход 12.1 блока 12. через элемент задержки 22 установится триггер 18 и в дальнейшем устройство работает аналогично описанному в предыдущем разделе.

В ведомых модулях также устанавливаются триггеры 14, если подконъюнкция, которую он вычисляет, равна единице, аналогично после считывания последней константы устанавливается триггер 18.

Таким образом, для вычисления многоразрядной булевой функции необходимо особое соединение модуяей, как, например, указано на фиг.4. Один модуль является ведущим, остальные - ведомыми. На фиг.4 изображены модули, вычисляющие булевые функции от 4-х аргументов (разрядность входов 27 4), входы расширения (дополнительные) имеют 4 разряда (28 1. 28 2. 28 3. 28.4).

На вход внешнего тактового генератора 34 ведущего модуля (УВ1) подан логический ноль, 6 старших разрядов шины адреса дешифрируются внешним дешифратором микроЭВМ для подключения по входам Е 31 соответствующего модуля УВ1-УВ4при настройке. Так, например, распределения адресного пространства портов ввода-вывода может иметь следующий вид: УВ 1 ЗООв-ЗОЗв УВ2 2008-203в УВЗ ЮОе-ЮЗв УВ4 ОООв-ОООЗв

При этом дешифратор дешифрирует шесть старших битов адреса, а два младших (0-3) дешифрируются внутри УВ 1 - УВ 4 посредством анализа шины 25 адреса. При настройке каждое из устройств настраивается отдельно, как было описано выше.

При вычислениях инициируется только первый модуль (ведущий), в нем же форми- руется результат, который анализируется внешним микроЭВМ при обращении только к нему. По окончании вычислений производится обнуление счетчика 15, триггеров 14, 18 аналогично описанному в каждом модуле отдельно.

Кроме того, внешняя микроЭВМ может инициировать вычисления отдельно в каждом модуле и анализировать результаты вычислений даже при соединении их для вычисления многоразрядных функций. Пример.

Пусть необходимо вычислить следующую булеву функцию:

Z X1X2X3X4X5X6X X8X9XtoX11X12Xt3Xl4X15X16V Х8Х}2.

Тогда для четырехразрядных модулей необходимо их соединить так, как указано на фиг,4.

Количество конъюнкций - 2, поэтому в каждый из модулей необходимо записать две константы.

Для УВ 1 (фиг.4): 1)JOJLOJ01ЈQ0001

12.212.1

2)0000000011001 Для УВ 2:

1)10101010 0 1111 2)00000001 11111 Для УВ 3:

1) 10 10 10 10 0 1111 2)00000000 11111 Для УВ 4:

1)10101010 0 1111 00 00 00 00 1 1111

По первому импульсу все УВ вычисляют каждый свою подконъюнкцию, причем УВ 1 формирует результат конъюнкций с учетом результатов УВ 2, УВ 3, УВ 4.

По второму импульсу вычисляется под- конъюнкция Х8, Х12. У В 1. УВ 4 ВЫПОЛНЯЮТ

холостые вычисления с нулевой константой, которые, безусловно, дают единичный результат.

Вторая константа является последней, поэтому вычисления заканчиваются.

Таким образом осуществляется параллельная работа всех четырех модулей. В прототипе в этих условиях необходим был бы последовательный опрос для первой конъюнкции - четырех модулей, для второй - двух модулей с. дальнейшим программным вычислением значения всей функции.

Технико-экономическая эффективность предлагаемого устройства заключается в следующем.

Пусть г - разрядность шины данных микропроцессора, тогда разрядность обрабатываемых прототипом дискретных

сигналов -п. Если В - разрядность (максимальная) конъюнкций вычисляемой булевой функции, то при использовании устройства2Впрототипа необходимо - циклов опроса

для вычисления подконъюнкций максимального ранга с программным вычислением

2§ г

В предлагаемом устройстве необходим один цикл опроса для-вычисления конъюнкций максимального ранга. Однако при этом возрастают временные затраты на настройку. Поэтому наиболее эффективна однократная настройка при инициализации системы (при включении питания на систему).

Предлагаемое устройство обеспечивает возможность разрядонаращиваемости, т.е. получения структур, вычисляющих много- рэзрядные.булевы функции, причем возможно построение пирамидальных структур. Так, при использовании устройства, подобного изображенному на фиг.4, к ведущему модулю возможно подключение до четырех ведомых, к которым, в свою очередь, можно подключить еще четыре и т.д.

Предлагаемое устройство позволяет расширить область применения на задачи вычисления многразрядных булевых функций, критические по времени при условии однократной настройки при инициализации системы.

Формула иаобретения

Устройство для ввода в микроЭВМ дискретных сигналов, содержащее дешифраконъюнкции (необходимо

устройств).

тор адреса, шинный формирователь, пять элементов И, два элемента ИЛИ, группу элементов И с тремя состояниями на выходе, группу элементов И-НЕ с тремя состояния- 5 ми на выходе, первый блок оперативной памяти, два триггера, счетчик, генератор, причем вход дешифратора адреса и вход- выход шинного формирователя являются соответствующими входом и выходом уст0 ройства для подключения к шинам адреса и данных микроЭВМ, первый выход дешиф- с ратора адреса соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с входом выбор5 ки шинного формирователя, вход задания направления передачи которого и первый вход первого элемента ИЛИ соединены с входом устройства для подключения выхода команды ввода микроЭВМ, выход перво0 го элемента ИЛИ соединен с вторым входом второго элемента И, второй вход первого элемента ИЛИ и второй вход третьего элемента И соединены с входом устройства для подключения команды вывода микро5 ЭВМ, вторые входы К-го (К 1,В, где В - разрядность информационных входов устройства) элемента И с тремя состояниями на выходе группы и К-ro элемента И-НЕ с тремя состояниями на выходе группы соедине0 ны с К-м разрядом входов для подключения дискретных сигналов, выходы К-ro элемента И с тремя состояниями на выходе группы и К-го элемента И-НЕ стремя состояниями на выходе группы соединены с К-м входом пер5 вого элемента И, нечетный выход первого блока оперативной памяти соединен с первым входом К-ro элемента И с тремя состояниями на выходе группы, четный выход первого блока оперативной памяти соеди0 нен с первым входом К-ro элемента И-НЕ с тремя состояниями на выходе группы, информационные входы первого блока оперативной памяти соединены с выходами шинного формирователя, вход управления

5 записью первого блока оперативной памяти подключен к выходу третьего элемента И и первому входу второго элемента ИЛИ, вход выборки первого блока оперативной памяти подключен к отрицательной шине источни0 ка питания, адресные входы первого блока оперативной памяти подключены к информационным выходам счетчика, второй выход дешифратора адреса подключен к первым входам четвертого и пятого элемен5 тов И, второй вход четвертого элемента И подключен к второму входу третьего элемента И, второй вход пятого элемента И подключен к первому входу первого элемента ИЛИ, а выход пятого элемента И подключен к входу установки первого триггера,

выход которого подключен к входу управления генератора, выход которого подключен к второму входу второго элемента ИЛИ, выход которого подключен к счетному входу счетчика, выход первого элемента И подключен к входу устанбвки второго триггера, выход четвертого элемента И подключен к входу сброса второго триггера, выход которого подключен к первому информационному входу шинного формирователя, отличающееся тем,что,с целью повышения быстродействия и расширения области применения путем вычисления и ввода многоразрядных булевых функций, в него введены второй блок оперативной памяти, третий и четвертый триггеры, шестой и седьмой элементы И, элемент задержки, третий элемент ИЛИ, группа элементов ИЛИ, причем третий выход дешифратора адреса подключен к второму входу шестого элемента И, входы сброса счетчика, второго и третьего триггеров объединены, (В+1)-й вход первого элемента И соединен с выходом второго элемента ИЛИ, (В+2)-й вход первого элемента И соединен с выходом седьмого элемента И, соответствующий вход которого подключен к выходу соответствующего элемента ИЛИ группы, первый выход первого блока оперативной памяти подключен к входу элемента задержки, выход которого соединен с входом установки третьего Триггера и вторым входом третьего элемента ИЛИ, первый вход которого является входом системного

KQtfcmcrtfmbt Ј/2

I J/Т

26

0

5

сброса, первый вход шестого элемента И соединен с вторым входом первого элемента ИЛИ, выход шестого элемента И подключен к входу установки четвертого триггера, входу управления записью второго блока оперативной памяти и четвертому входу второго элемента ИЛИ, инверсный выход четвертого триггера подключен к вто- рьм входам элементов ИЛИ группы, первые входы которых соединены с соответствующим выходом второго блока оперативной памяти, информационные входы которого подключены к информационным входам первого блока оперативной памяти, адресные входы первого и второго блоков оперативной памяти объединены, вход выборки второго блока оперативной памяти подключен к отрицательной шине источника питания, выход третьего триггера подключен к 0 второму информационному входу шинного формирователя, третьи входы элементов ИЛИ группы являются дополнительными информационными входами устройства и соединены с третьим информационным входом шинного формирования, Е-вход дешифратора адреса является входом разрешения устройства, вход сброса четвертого триггера подключен к входу сброса устройства, третий вход второго элемента ИЛИ является входом внешнего тактового генератора, выход первого элемента И является выходом разрешения устройства, выход генератора является тактовым выходом устройства.

5

0

fotfa/narrfatt в (7

jЈL

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1987 |

|

SU1503043A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для ввода-вывода дискретных сигналов микроЭВМ | 1989 |

|

SU1681306A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

зг

30

3erf7l/Ob nOffCfneKVfrr Ј fS

/

15

К

(.2

ю

/7

-HX

Фиа.2

efefffwatfi/e rfJcr/мязл Jorffeatarffnt a ff

/- s /

X

y X

eat

x/-A k0#cmcrt n

Cmaflufttt Z афеел g

ЪС

мка&ине айресл 3t

25

17; A

E A B,

Л м

ОУГ

4 4

5/

if

Ј7

J&L J§&

Ж

гг

3/

гу

г/

ЗИ

Ј12

«

газ

ЗД жг

л

/ 42

fc

Jf

Jtt

-ак ai

зг

А я

25

Ј9

SO

35

Д

34 J

nf

6

29

го

15

кзз

34

26

29

за

55

Ј3

34

л

IN 01ГТ

е

аи

т

26

23

SO

55

& 34

Авторы

Даты

1992-07-30—Публикация

1990-11-11—Подача