Изобретение относится к вычисли- тельной технике и может быть использовано в высокоскоростньпс локальных сетях связи.

Целью изобретения являемся повьше- иие точности декодирования и быстродействия устройства за счет сокращения времени регенерации и уменьше- кия флуктуации точки регенерации.

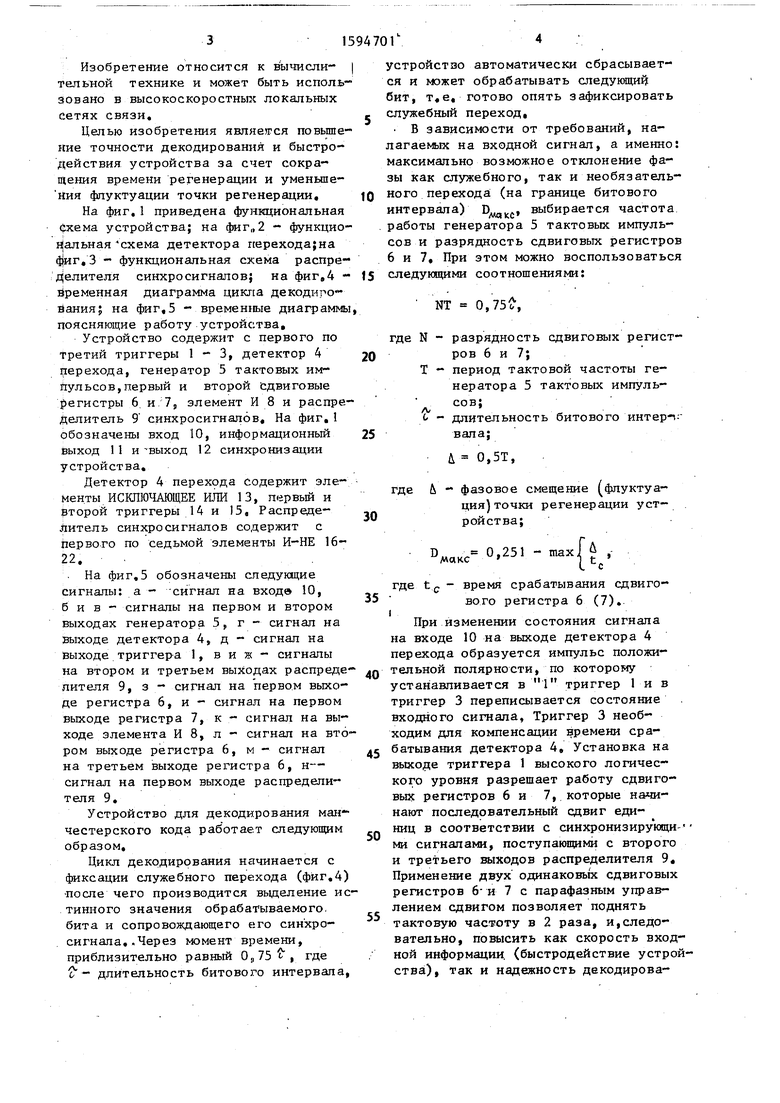

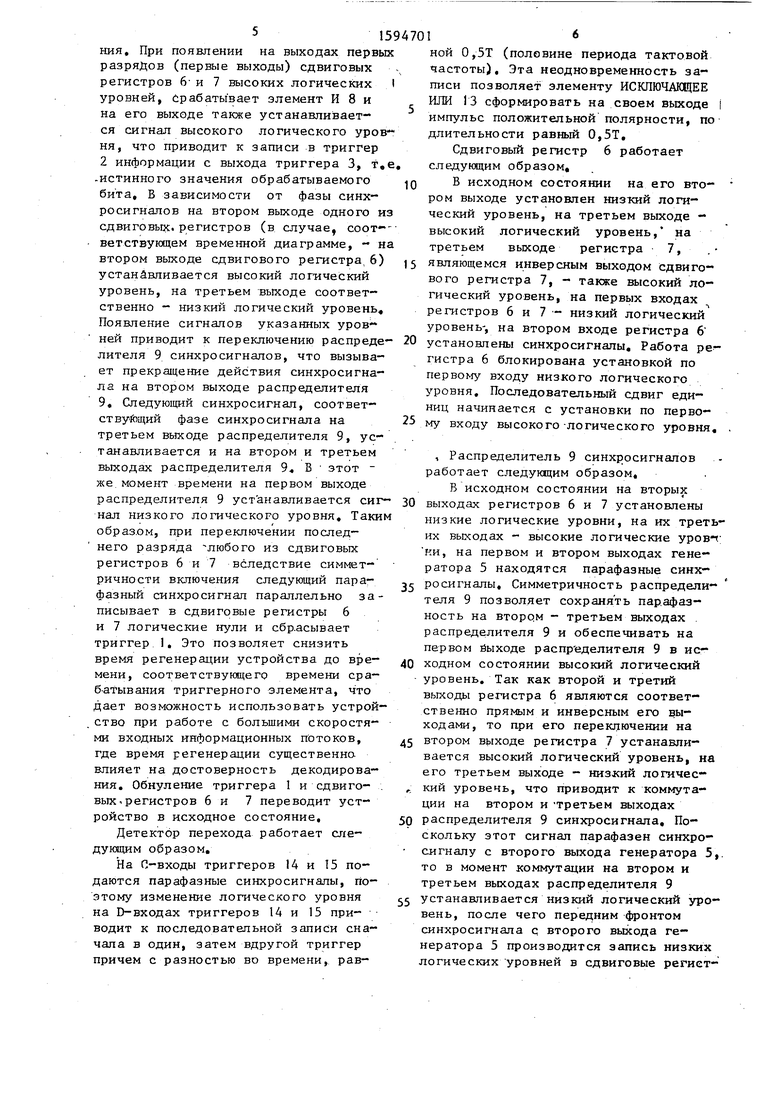

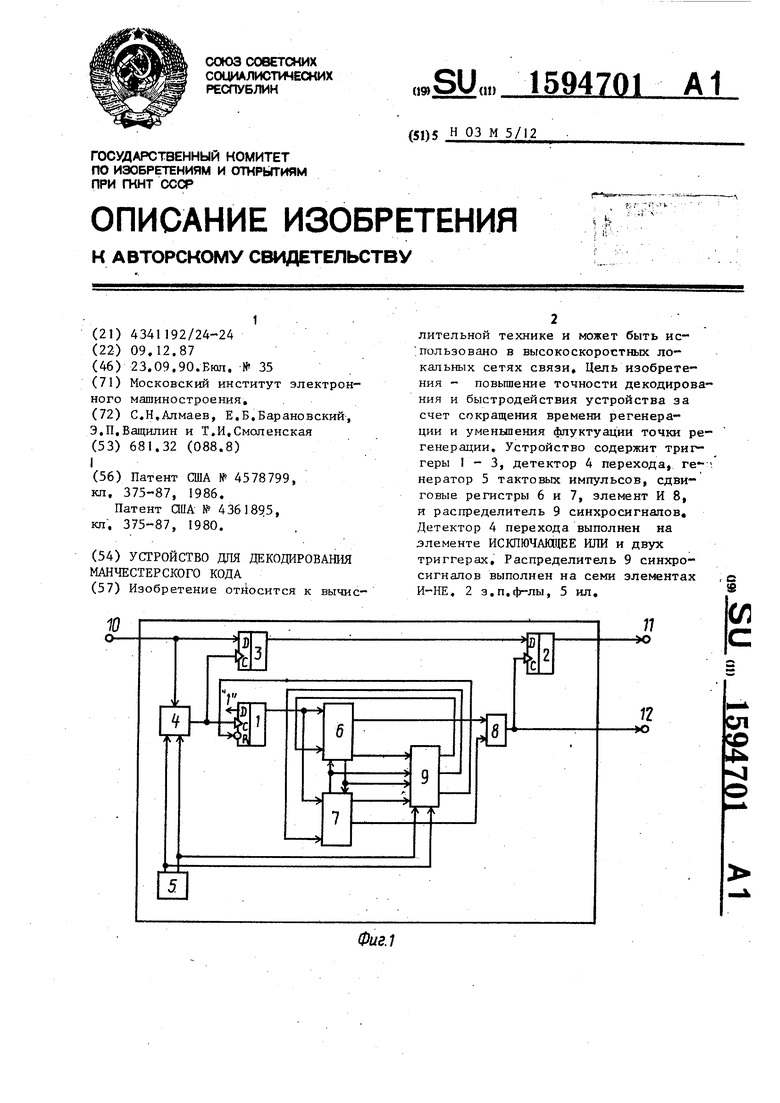

На фиг, приведена функциональная фхема устройства; на фиг,, 2 - функцио- И.альная схема детектора перехода;на фиг.З - функциональная схема распре- л|елителя синхросигналов; на фиг,4 - йременная диаграмма цикгса декодиро- йания; на фиг,5 - временшле диаграм1мы поясняющие работу устройства.

Устройство содержит с первого по третий триггеры 1-3, детектор 4 перехода, генератор 5 тактовых импульсов, первый и второй сдвиговые |)егистры 6, и 7, элемент И 8 и распределитель 9 синхросигналов. На фиг, 1 обозначены вход 10, информационный выход 11 невыход 12 синхронизации устройства.

Детектор 4 перехода содержит эле- менты ИСКЛЮЧАЮЩЕЕ ИЛИ 13, первый и второй триггеры 14 и 15, Распределитель синхросигналов содержит с hepвого по седьмой элементы И-НЕ 16- 22,..

. На фиг,5 обозначены следующие сигналы: а - -сигнал на входе 10, б и в - сигналы на первом и втором выходах генератора. 5, г - сигнал на выходе детектора 4, д - сигнал на выходе триггера 1, в и ж - сигналы на втором и третьем выходах распределителя 9, 3 - сигнал на первом выходе регистра 6, и - сигнал на первом выходе регистра 7, к - сигнал на выходе элемента И 8, л - сигнал на втором выходе регистра 6, м - сигнал на третьем выходе регистра 6, н- сигнал на первом выходе распределителя 9,

Устройство для декодирования манчестерского кода работает следующим образом.

Цикл декодирования начинается с фиксации служебного перехода (фиг,4) после чего производится выделение истинного значения обрабатываемого, бита и сопровождающего его синхросигнала, .Через момент времени, приблизительно равный t- , где c - длительность битового интервала,

устройство автоматически сбрасывается и может обрабатывать следующий бит, т,е, готово опять зафиксировать служебный переход,

. В зависимости от требований, налагаемых на входной сигнал, а именно: максимально возможное отклонение фазы как служебного, так и необязательного перехода; (на границе битового интервала) Одадкл1 выбирается частота работы генератора 5 тактовых импульсов и разрядность сдвиговых регистров 6 и 7, При этом можно воспользоваться следующими соотношениями:

NT

0,75

где N - разрядность сдвиговых регистров 6 и 7;

Т - период тактовой частоты генератора 5 тактовых импульсов;л/ / - длительность битового интер-п;вала;Л 0,5Т,

где

& - фазовое смещение (флуктуация) точки регенерации устройства;

макс 0251 -maxj

35

где tf - время срабатывания сдвигового регистра 6 (7),

0

0

5

При изменении состояния сигнала на входе 10 на выходе детектора 4 перехода образуется импульс положительной полярности, по которому устанавливается в 1 триггер 1 и в триггер 3 переписывается состояние входного сигнала. Триггер 3 необходим для компенсации времени сра- с батывания детектора 4, Установка на выходе триггера 1 высокого логического уровня разрешает работу сдвиговых регистров 6 и 7, которые начинают последовательный сдвиг единиц в соответствии с синхррнизирующи- ми сигналами, поступающими с второго и третьего выходов распределителя 9, Применение двух одинаковьпс сдвиговых регистров 6 и 7 с парафазным управлением сдвигом позволяет поднять тактовую частоту в 2 раза, и,следовательно, повысить как скорость входной информации, (быстродействие устройства), так и надежность декодирования. При появлении на выходах первых разрядов (первые выходы) сдвиговых регистров 6- и 7 высоких логических I уровней, Срабатывает элемент И 8 и на его выходе также устанавливается сигнал высокого логического уров ня, что приводит к записи в триггер 2 информации с выхода триггера 3, т,е -ИСТИННОГО значения обрабатываемого бита, В зависимости от фазы синхросигналов на втором выходе одного из сдвиговьрс. регистров (в случае, соот-- ветствующем временной диаграмме, - на втором выходе сдвигового регистра, 6) устанавливается высокий логический уровень, на третьем выходе соответственно - низкий логический уровень. Появление сигналов указанных уровней приводит к переключению распределителя 9 синхросигналов, что вызывает прекращение действия синхросигнала на втором выходе распределителя 9, Следующий синхросигнал, соответ- фазе синхросигнала на третьем выходе распределителя 9, устанавливается и на втором и третьем выходах распределителя 9« В этот - же момент времени на первом выходе распределителя 9 устанавливается сигнал низкого логического уровня. Таким образ.ом, при переключении последнего разряда любого из сдвиговых регистров 6 и 7 вследствие симмет- ричности включения следующий пара- фазный синхросигнал параллельно записывает в сдвиговые регистры 6 и 7 логические нули и сбрасывает триггер 1, Это позволяет снизить время регенерации устройства до времени, соответствующего времени ера- б-аТывания триггерного элемента, что ает возможность использовать устрой- ство при работе с большими скоростями входных информационных потоков, где время регенерации существенно влияет на достоверность декодирования. Обнуление триггера 1 и сдвиго- . вых регистров 6 и 7 переводит устройство в исходное состояние.

Детектор перехода работает слеующим образом.

На П-входы триггеров 14 и 15 поаются парафазные синхросигналы, потому изменение логического уровня а D-входах триггеров 14 и 15 приводит к последовательной записи сначала в один, затем вдругой триггер ричем с разностью во времени, рав-

0

ной 0,5Т (половине периода тактовой частоты). Эта неодновременность записи позволяет элементу ИСКЛЮЧАЮЩЕЕ ИЛИ 13 сформировать на своем выходе i импульс положительной полярности, по длительности равный 0,5Т,

Сдвиговый регистр 6 работает следуннцим образом,

В исходном состоянии на его втором выходе установлен низкий логический уровень, на третьем выходе - высокий логический уровень, на третьем выходе регистра 7, 5 являющемся инверсным выходом сдвигового регистра 7, - также высокий логический уровень, на первых входах регистров 6 и 7 - низкий логический уровень-, на втором входе регистра 6 установлены синхросигналы. Работа ре гистра 6 блокирована установкой по первому входу низкого логического уровня. Последовательный сдвиг единиц начинается с установки по перво0

5

му входу высокого-логического уровня.

, Распределитель 9 синхросигналов работает следующим образом,

В исходном состоянии на вторых

выходах регистров 6 и 7 установлены низкие логические уровни, на их третьих выходах - высокие логические ypOBf ки, на первом и втором выходах генератора 5 находятся парафазные синхросигналы. Симметричность распределителя 9 позволяет сохранять парафаз- ность на втором - третьем выходах распределителя 9 и обеспечивать на первом йыходе распр еделителя 9 в ис-

ходном состоянии высокий логический уровень. Так как второй и третий выходы регистра 6 являются соответственно прямым и инверсным его выходами, то при его переключении на

втором выходе регистра 7 устанавливается высокий логический уровень, на его третьем выходе - низкий логичес- кий уровень, что приводит к коммутации на втором и Третьем выходах

распределителя 9 синхросигнала. Поскольку этот сигнал парафазен синхросигналу с второго выхода генератора 5,. то в момент коммутации на втором и третьем выходах распределителя 9 устанавливается низкий логический уровень, после чего передним фронтом синхросигнала с второго выхода генератора 5 производится запись низких огических уровней в сдвиговые регистры 6 -и 7, одновременно с этим на первом выходе распределителя 9 вырабатывается сигнал низкого логического уровня. Запись в регистры 6 и 7 низких логических уровней переводит распределитель 9 в исходное состояние. Симметричность построения распределителя 9 синхросигналов позволяет аН:апогично срабатывать и при смене управления на втором и третьем выходах регистра 7, производя коммутацию синхросигналов с первого выхода генератора 5 на вход распределителя 9.

Формула изобре т -е н и я

1. Устройство для декодирования манчестерского кода, содержащее генератор тактовых импульсов, первый выход которого соединен с первым входом детектора перехода, выход которого соединен с С-входом первого триггера, второй вход детектора перехода является входом устройства, выход второго триггера является информационным выходом устройства, о т л и - чающе еся тем, что, с целью п вьшения точности декодирования и быстродействия устройства за счет сокращения времени регенерации и уменьшения флуктуации точки регенерации, в устройство введены сдвиговые регистры, элемент И и распределитель синхросигналов, первый выход которого соединен с R-входом первого регистра, выход которого соединен с первыми входами первого и второго сдвиговых регистров, первые вьгходы которых соединены соответственно с первым и вторым входами элемента И, второй и третий выходы распределителя синхросигналов соединены с вторыми входами соответственно первого и второго сдвиговых регистров, вторые выходы которых соединены соответственно с первым и вторым входами распределителя синхросигналов, третий выход первого сдвигового регистра соединен с третьими входами второго сдвигового регистра и распределителя синхросигнала,-. третий выход второго сдвигового регистра соединен с третьим входом первого сдвигового регистра и с четвертым входом распределителя синхросигналов, пятый вход распределителя синхросигналов под-

5

0

5

ключен к первому выходу генератора тактовых импульсов, второй выход которого соединен с шестым входом распределителя синхроимпульсов и с третьим входом детектора переноса, первый вход которого объединен .с D-входом третьего триггера, выход которого соединен с D-входом второго триггера, С-вход третьего триггера подключен к выходу детектора перехода, выход элемента И соединен с С-входом второго триггера и является выходом синхронизации устройства.

2, Устройство по п,1, о т л и- чающееся тем, что детектор перехода выполнен на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ и триггерах, выходы первого и второго триггеров соединены соответственно с первым и вторым входами элемента ИСКПЮЧАЮидаЕ ИЛИ, выход которого является выходом детектора, D-входы первого и второго триггеров объединены и являются первым входом детектора. С-входы первого и второго триггеров являются соответственно вторым и третьим входами детектора. 1

3, Устройство по п.1, о т л и- чающееся тем, что распределитель синхронизации выполнен на элементах И-НЕ, выходы первого и второго элементов И-НЕ соединены соответственно с первым и вторым входами третьего элемента И-НЕ, выход которого соединен с первым входом- четвертого элемента И-НЕ, выход которого яв- является первым выходом распределите-

,Q ля, выход третьего элемента является вторым выходом распределителя, выходы пятого и шестого элементов И-НЕ соединены соответственно с первым и вторым входами седьмого эле4г мента И-НЕ, выход которого является третьим входом распределителя, первые входы второго и пятого элементов И-НЕ являются соответственно первым и вторым входами распределителя, первые входы первого и шестого элементов И-НЕ являются соответственно третьим и четвертым входами распределителя, вторые входы первого и пятого элементов И-НЕ объединены и являются пятым входом распределителя, вторые входы второго и шестого элементов И-НЕ объединены и являются шестым входом распределителя.

0

5

50

55

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2000 |

|

RU2192711C2 |

| Устройство приема двоичной информации в последовательном коде | 1991 |

|

SU1771075A1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| СПОСОБ СДВИГА ФАЗЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2141165C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2218669C1 |

| Устройство для декодирования манчестерского кода | 1987 |

|

SU1495999A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокоскоростных локальных сетях связи. Цель изобретения - повышение точности декодирования и быстродействия устройства за счет сокращения времени регенерации и уменьшения флуктуации точки регенерации. Устройство содержит триггеры 1-3, детектор 4 перехода, генератор 5 тактовых импульсов, сдвиговые регистры 6 и 7, элемент 8 И и распределитель 9 синхросигналов. Детектор 4 перехода выполнен на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ и двух триггерах. Распределитель 9 синхросигналов выполнен на семи элементах И-НЕ. 2 з.п.ф-лы, 5 ил.

Фйг.З

I ктоция mo tHi/

I I и регенерации

ФиеЛ

Фиг. 5

| Патент США № 4578799, кп | |||

| Ручной дровокольный станок | 1921 |

|

SU375A1 |

| Патент QUA № 4361895, кп | |||

| Ручной дровокольный станок | 1921 |

|

SU375A1 |

Авторы

Даты

1990-09-23—Публикация

1987-12-09—Подача