9

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования манчестерского кода | 1988 |

|

SU1524181A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство коррекции двойных ошибок с использованием кода Рида-Соломона | 1988 |

|

SU1662010A1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

Изобретение относится к электросвязи, может использоваться для построения локальных сетей связи и обеспечивает контроль сбоев и обнаружение информации на входе, осуществляя слежение за несущей, что расширяет функциональные возможности устройства. Устройство содержит линейный блок 1, формирователь 2 импульсов, генератор 3 тактовых импульсов, элементы И 4, 5, счетчик 6 импульсов, распределитель 7 импульсов, триггер 8 и блок 9 обнаружения сбоев. 1 з.п. ф-лы, 6 ил.

4

СО ел

со со со

ф1/е.1

Изобретение относш ся к электросвязи и может быть использовано для построения локальных сетей связи.

Целью изобретения является распм рение функциональных возможностей устройства за счет обеспечения контроля сбоев.

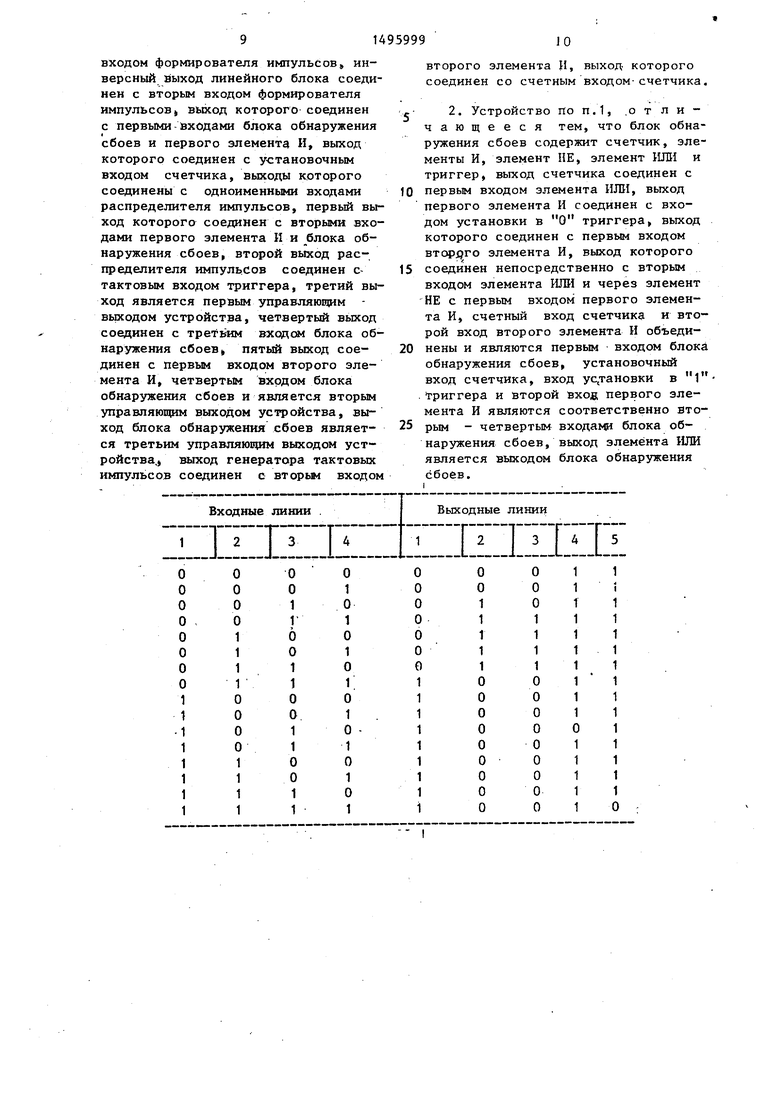

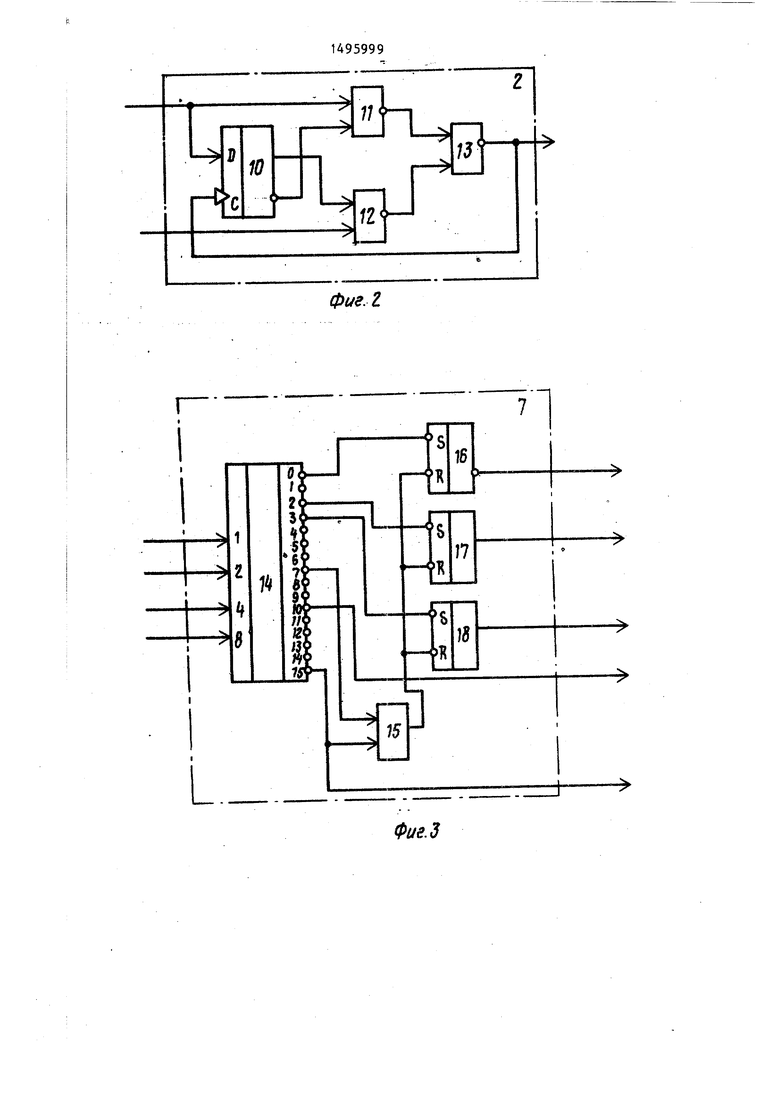

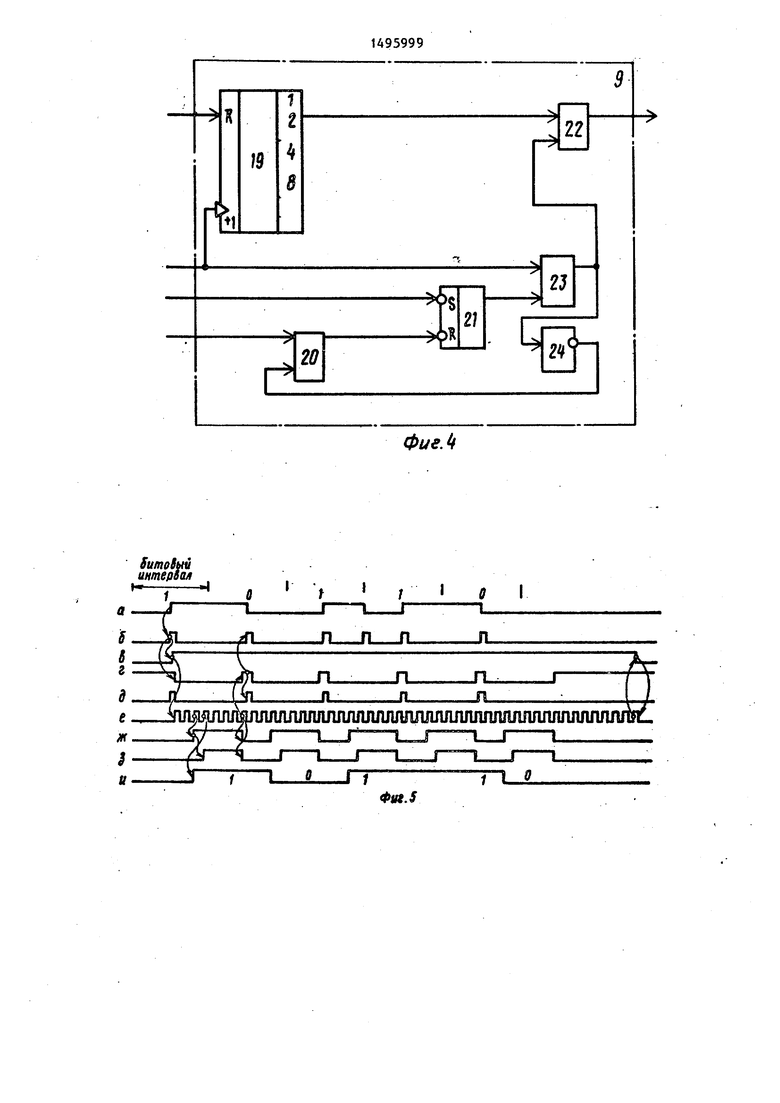

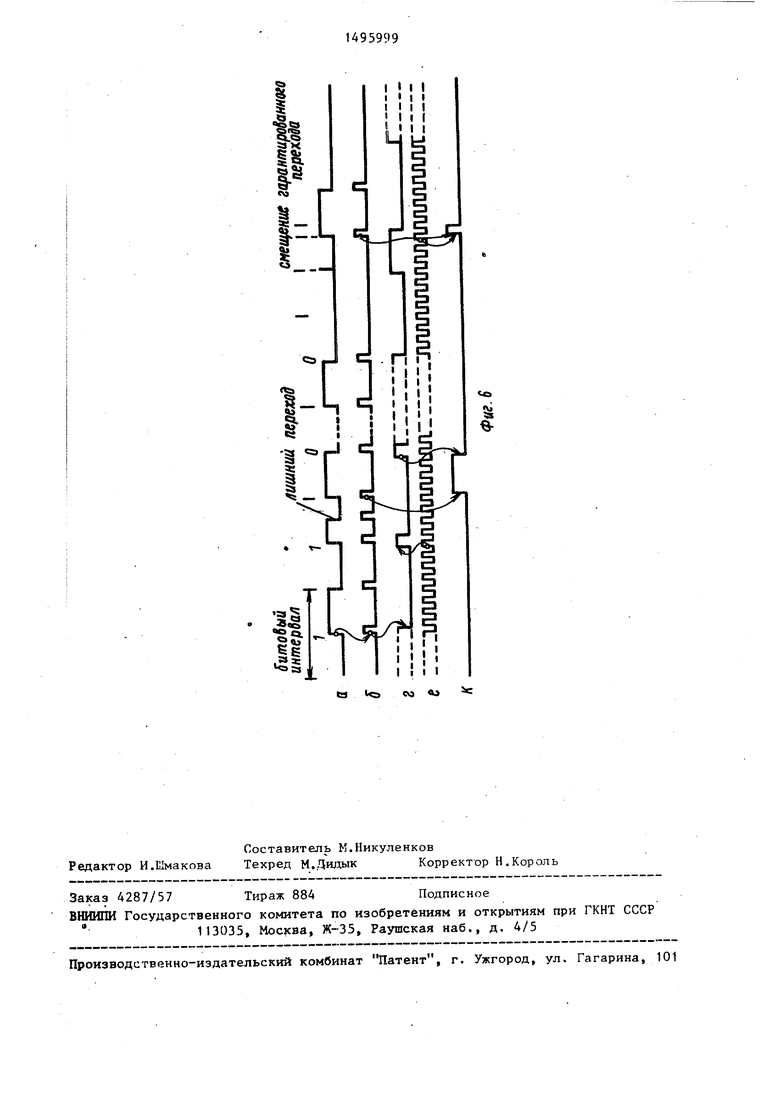

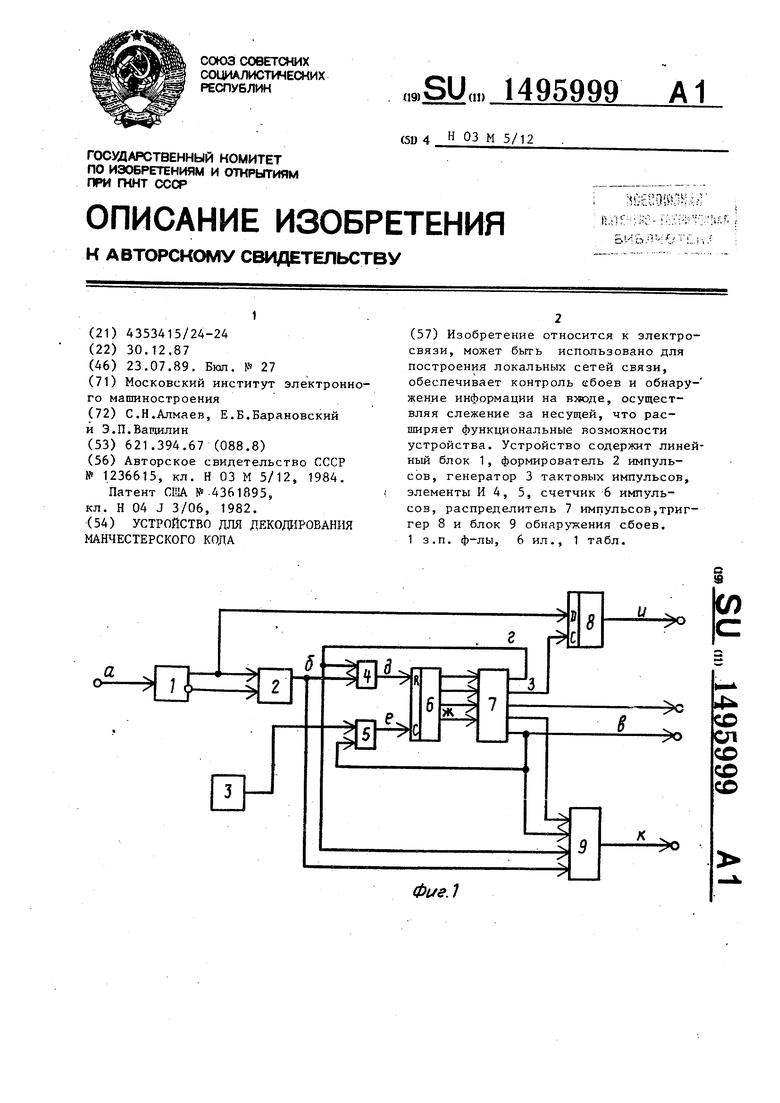

На фиг. 1 представлена структурная схема устройства; на фиг, 2 - функциональная схема формирователя импульсов; на фиг. 3 - функциональная схема распределителя импульсов; на фиг. 4 - функциональная схема блока обнаружения сбоев; на фиг. 5 и 6 - временные диаграммы, поясняющие работу устройства при декодировании соответственно корректной и некорректной входных кодовьр; комбина- дай.

Устройство для декодирования манчестерского кода содержит (фиг,1) линейный блок (входной усилитель)1, формирователь 2 импульсов, генератор 3 тактовых импульсов, первый 4 и второй 5 элементы И,счетчик 6 импульсов, распределитель 7 импульсов, триггер 8 и блок 9 обнаружения сбоев

Формирователь 2 импульсов содержит (фиг.2) триггер 10 и элементы И-НЕ 11-13.

Распределитель 7 импульсов содержит (фиг.З) дешифратор 14, элемент И 15 и триггеры 16-18,

Блок 9 обнаружения сбоев содержит (фиг.4) счетчик 19 импульсов, первый элемент И 20, триггер 21, элемент ИЛИ 22, второй элемент К 22 и элемент НЕ 24,

Устройство работает следующим образом.

В исходном состоянии на входе и прямом выходе блока 1, на выходах формирователя 2 и элементов И 4 и 5, вторсм, третьем и пятом выходах распределителя 7 установлены уровни логического О, на инверсноУ1 выходе блока 1, выходах счетчика 6, первом и четвертом выходах распределителя 7 установлены уровни логической

44(1

I .

При поступлении на вход устройства информации, представленной манчестерским кодом, устройство обрабатывает количество циклов, соответствующее числу кодированных бит, и выделяет из входной информации данные и синхросигналы. Кроме того, устройство контролирует корректность

входной информации по отклонению длительности битового интервала и, в соответствии с этим отклонением,

фиксирует сбойные ситуации. Устройство вырабатывает также сигнал-.; Несущая, инициируюгщй наличие на входе кодированной информации. Поэтому работу устройства целесообразно

рассмотреть отдельно: в случае декодирования корректной входной информации и в случае декодирования некорректной входной информации, т.е. при фиксации сбойных ситуаций.

В случае декодирования корректной входной информации устройство работает следующим образом.

Входная информа1у1я (фиг.З) поступает на вход линейного блока 1 , с

прямого выхода которого информация поступает на первый вход формирователя 2 импульсов и D-вход триггера 8, а с инверсного выхода - на второй вход формирователя 2. Изменение состояния сигналов на выходах блока 1 вызывает срабатывание формирователя 2 на выходе которого (фиг. 5б) вырабатывается импульс уровня логической 1, поступаю1Г1 1й на первые

входы элемента И 4 и блока 9 обнаружения сбоев. В этот момент на втором входе элемента И 4 (фиг.Зг) установлен уровень логической 1, что приводит к передаче на вход

счетчика 6 (фиг.Зд) импульса уровня логической 1 с выхода формирователя 2„ Это приводит к обнулению счетчика 6 и, как следствие, установке на пятом выходе распределителя 7

(фиг. 5в) сигнала уровня логической 1 (Несущая), поступающего на первый вход элемента И 5 и на четвертый вход блока 9 обнаружения сбоев. В этот момент времени на первом

выходе распределителя 7 (фиг.Зг) устанавливается сигнал уровня логического О, который блокирует элемент И 4, для устранения ложных запусков устройства в случае декодирования

некорректной входной информации. Установка уровня логической 1 на пятом выходе распределителя 7 разрешает прохокцение тактовых сигналов с выхода генератора 3 через элемент

И 5 на счетный вход счетчика 6 , (фиг,5е). При поступлении тактовых импульсов начинает изменяться состояние выходов счетчика 5 (фиг.Зж), Рас1тределитет ь 7 анализирует состояние уровней сигналов на выходах счетчика 6 и вырабатывает на втором и третьем выходах (фнг.Зз) сигналы уровня логической 1, а на

четвертом выходе - сигнал уровня логического О.

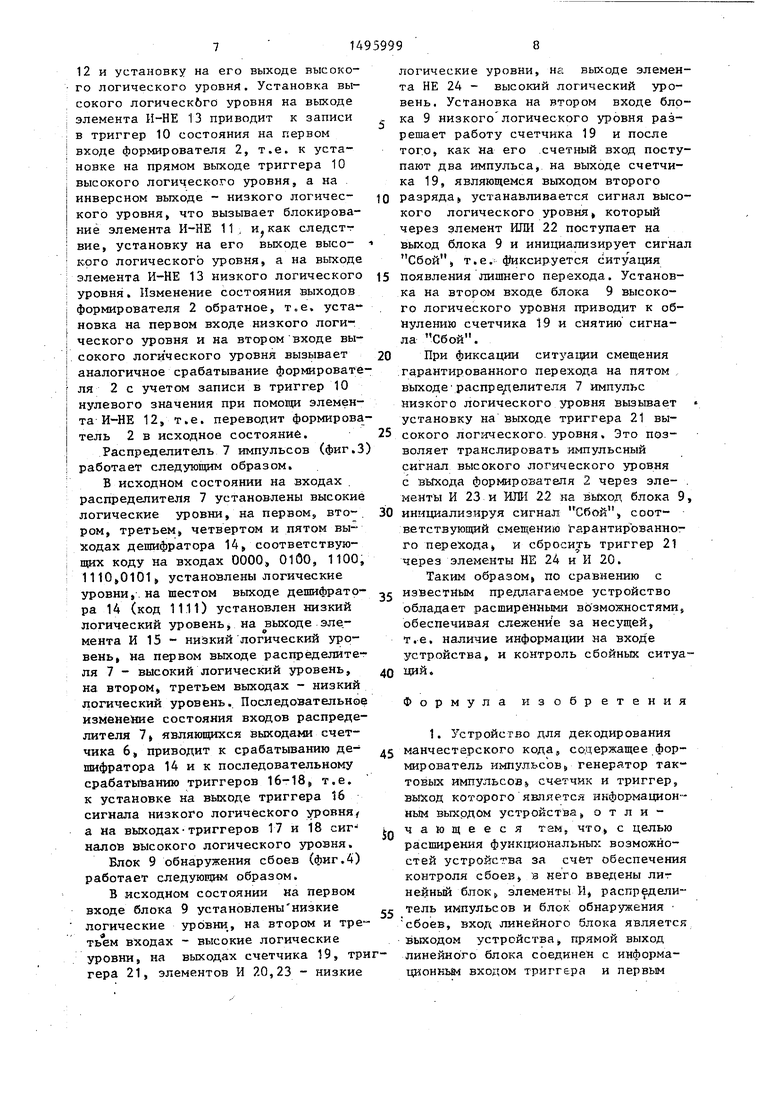

В таблице приведена зависимость состояний выходов распределителя 7 импульсов от состояний его входов.

Таким образом, в зависимости от количества тактовьк импульсов, поступающих на счетный вход счетчика 6, вырабатываются импульсы, обеспечивающие запись истинного значения декодируемого двоичного сигнала в триггер 8 (фиг. 5з), и синхросигнал, сопровождающий декодирование двоичного сигнала на третьем выходе распределителя 7, после чего устройст- во готово декодировать следующий бит входной информации (установка на первом выходе распределителя 7 уровня логической 1). Поступление на вход устройства нового бита вызывает срабатывание формирователя 2, что опять приводит к сбросу счетчика 6 и повторению цикла декодирования. В случае, если декодируемый бит является последним (счетчик 6 досчитает до единичного состояния (на его выходах устанавливаются уровни логической 1), что приводит к установке устройс.тва в исходное состояние. При этом на пятом выходе распределителя 7 (фиг. 5в) установлен уровень логического О и поступление тактовых импульсов с выхода генератора 3 заблокировано, счетчик 6 остается в единичном состоянии.

Таким образом, при декодировании входной информации на пятом выходе распределителя 7 устанавливается уровень логической 1, инициализирующий сигнал Несущая и снимаемый при окончании декодирования при отсутствии информации на входе устрой- с ява.

Случай декодирования некорректной входной информации можно разделить на две ситуации: появление лишнего перехода в декодируемом бите и смещение гарантированного перехода. В первом случае за появлением лишнего пере- хода производится во второй половине декодируемого битового интервала, иначе - в половине битового интервала, следующей за гарантированньм переходом и определяющей истинное

4959996

значение декодируемого бита. При этом лишний переход фиксируется блоком 9 обнаружения сбоев, который, с контролирует состояние выхода формирователя 2 и первого выхода распределителя 7. Переход, т.е. импульс, уровня логической 1 на выходе формирователя 2 воспринимается блоком

10 9 как лишний, если на первом выходе распределителя 7 в этот момент установлен уровень логического О и этот переход является вторым после гарантированного перехода. При этом

15 состояние первого выхода распределителя 7 (уровень логического О) после гарантированного перехода не изменялось. В этот момент блок 9 устанавливает на своем выходе

20 (фиг. 6к) сигнал уровня логической 1 (сбой), который снимается при условии установки на п ервом выходе

распределителя 7 уровуя логической I111I

I b

25 Во втором случае, т.е. при смещении гарантированного перехода, на четвертом выходе распределителя 7 формируется импульс логического О, который фиксируется блоком 9. Если

30 после этого состояние пятого выхода распределителя 7 (несущая) не изменяется, т.е. сохраняется состояние уровня логической 1 , и на выходе фор5

0

5

0

5

мирователя 2 выработан импульс уровня логической 1, то иг. выходе блока 9 (фиг.бк) формируется сигнал уровня логической 1 (сбой), инициирующий некорректность входной информации .

Формирователь 2 импульсов (фиг.2) работает следуюп5им образом.

В исходном состоянии на первом входе и выходе формирователя 2 установлены низкие логические уровни, на втором входе - высокий логический уровеньj на пятом выходе триггера 10 - низкий логический уровень, на инверсном выходе - высокий логический уровеньi на выходах элементов И-НЕ 11 и 12 установлены высокие логические уровни. Смена состояния на входах формирователя 2, т.е. установка на первом входе высокого лопг- ческого уровня, а на втором входе - низкого логического уровня, приводит к срабатыванию элемента И-НЕ 11, на . выходе которого устанавливается логический уровень, что, в свою очередь, вызывает срабатывание элемента И-НЕ

12 и установку на его выходе высокого логического уровни. Установка высокого логическбго уровня на выходе элемента Н-НЕ 13 приводит к записи в триггер 10 состояния на первом входе формирователя 2, т.е. к установке на прямом выходе триггера 10 высокого логического уровня, а на инверсном выходе - низкого логичес- кого уровня, что вызывает блокирование элемента И-НЕ 11, и как следст-г вие, установку на его выходе высо- кого логического уровня, а на выходе элемента И-НЕ 13 низкого логического уровня. Изменение состояния выходов формирователя 2 обратное, т.е. установка на первом входе низкого логического уровня и на втором входе высокого логического уровня вызывает аналогичное срабатывание формирователя 2с учетом записи в триггер 10 нулевого значения при помощи элемента 12, т.е. переводит формирователь 2 в исходное состояние.

Распределитель 7 импульсов (фиг.З работает следующим образом.

В исходном состоянии на входах распределителя 7 установлены высокие логические уровни, на первом, вто ром, третьем, четвертом и пятом выходах дешифратора 14, соответствующих коду на входах 0000, 01бО, 1100, 1110,0101, установлены логические уровни,.на тестом выходе дешифратр- ра 14 (код 1111) установлен низкий логический уровень, на выходе эле,- мента И 15 низкий логический уровень, на первом выходе распрёделите-г ля 7 - высокий логический уровень, на втором, третьем выходах - низкий логический уровень. Последовательное изменеМие состояния входов распределителя 7, являющихся выходаю счетчика 6, приводит к срабатыванию де- шифратора 14 и к последовательному срабатыванию триггеров 16-18, т.е. к установке на выходе триггера 16 сигнала низкого логического уровня/ а на выходах-триггеров 17 и 18 сиг- налов высокого логического уровня.

Блок 9 обнаружения сбоев (фиг,4) работает следующим образом.

В исходном состоянии на первом входе блока 9 установлены низкие логические уровни,, на втором и тре- входах - высокие логические уровни, на выходах счетчика 19, тригера 21, элементов И 20,23 - низкие

логические уровни, на выходе элемента НЕ 24 - высокий логический уровень. Установка на втором входе блока 9 низкого логического уровня разрешает работу счетчика 19 и после того, как на его .счетный вход поступают два импульса, на выходе счетчика 19, являющемся выходом второго разряда, устанавливается сигнал высокого логического уровня, который через элемент ИЛИ 22 поступает на выход блока 9 и инициализирует сигна Сбой, т.е.- фиксируется ситу ация появления лишнего перехода. Установка на втором входе блока 9 высокого логического уровня приводит к обнулению счетчика 19 и снятию сигнала Сбой.

При фиксации ситуации смещения гарантированного перехода на пятом выходе распре/белителя 7 импульс Низкого логического уровня вызывает установку на выходе триггера 21 высокого логического, уровня. Это позволяет транслировать импульсный сигнал высокого логического уровня с выхода формирователя 2 через эле- меНтЫ И 23 И ИЛИ 22 на вь1ход блока 9 инициализируя сигнал С6ой соответствующий смещению арантированно- го перехода, и сбросить триггер 21 через элементы НЕ 24 и И 20.

Таким образом, по сравнению с известным предлагаемое устройство обладает расширенными во зможностями, обеспечивая слежение за несущей, т.е. наличие информации на вход е устройства, и контроль сбойных ситуаций.

Формула изобретения

входом формирователя импульсов, инверсный выход линейного блока соединен с вторым входом формирователя импульсов выход которого соединен с первыми йходами блока обнаружения сбоев и первого элемента И, выход которого соединен с установочным входом счетчика, выходы которого соединены с одноименными входами распределителя импульсов, первый выход которога соединен с вторыми входами первого элемента И и блока обнаружения сбоев, второй выход распределителя импульсов соединен с- тактовым входом триггера, третий выход является первым управляющим - выходом устройства, четвертый выход соединен с третьим входе блока обнаружения сбоев пятый выход сое- динен с первым входом второго элемента И, четвертым входом блока обнаружения сбоев и является вторым управляюпщм выходом устройства, выход блока обнаружения сбоев являет- ся третьим управляющим выходом устройства., выход генератора тактовых импульсов соединен с вторьм входом

)0 152025

95999JO

второго элемента И, выход- которого соединен со счетным входом-счетчика.

фие.1

Фие.З

интервали-и

/ « ff I

-С

гП

П П П

1 I2ГТ

fflL

3

ФигЛ

JL

TL

ча

| Декодер | 1984 |

|

SU1236615A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-30—Подача