(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| "Устройство для контроля кода "1 из @ " | 1988 |

|

SU1654981A2 |

| Устройство для контроля кода "1 из N | 1986 |

|

SU1345353A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

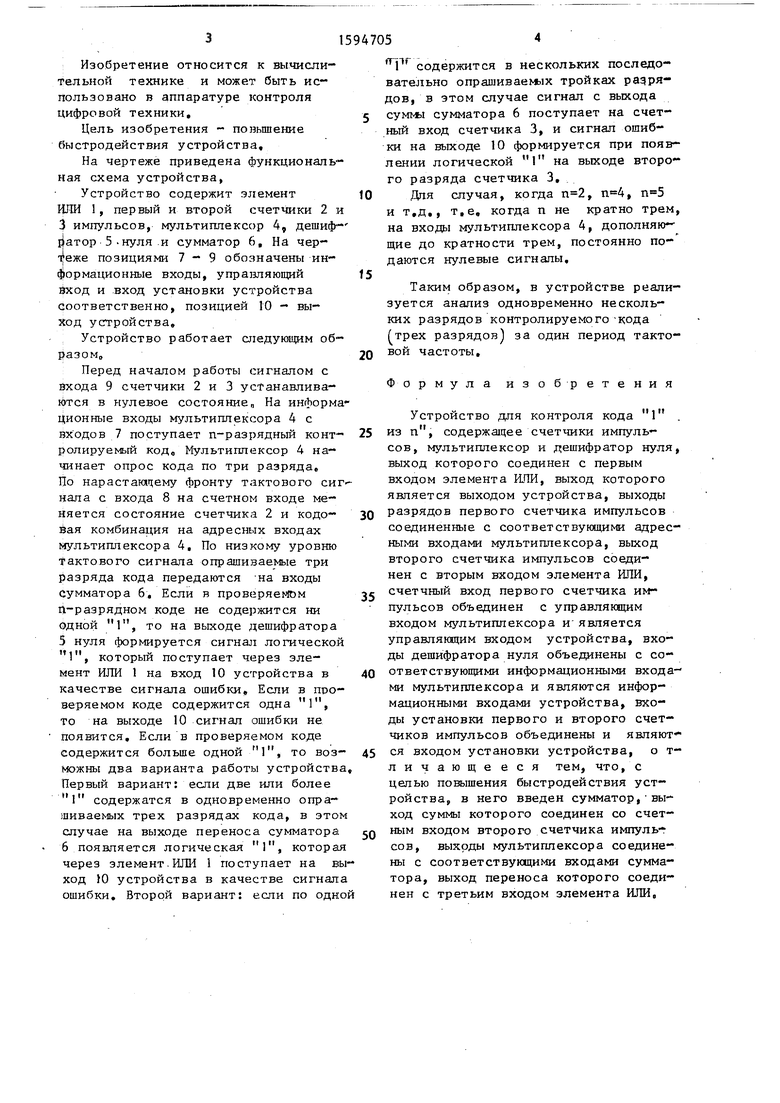

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре контроля цифровой техники. Обеспечивая анализ нескольких разрядов контролируемого хода в течение одного периода тактовой частоты, оно повышает быстродействие устройства. Устройство содержит элемент ИЛИ 1, счетчики 2 и 3 импульсов, мультиплексор 4, дешифратор 5 нуля и сумматор 6. 1 ил.

ю

СП

;о

4

1У1

Изобретение относится к вычислительной технике и может быть ис пользовано в аппаратуре контроля цифровой техники,

Цель изобретения - поньшение быстродействия устройства.

На чертеже приведена функциональная схема устройства,

Устройство содержит элемент

ИЛИ 1, первый и второй счетчики 2 и 3 импульсов, мультиплексор 4, дешиф-- 1|атор 5-нуля .и сумматор 6, На чер- позициями 7-9 обозначены информационные входы, упраззляющий йход и вход установки устройства Соответственно, позицией 10 - выход устройства.

Устройство работает следующим об- разом

Перед началом работы сигналом с входа 9 счетчики 2 и 3 устанавливаются в нулевое состояние. На информационные входы мультиплексора 4 с вх одов 7 поступает п-разрядный конт- ролируемый коДв Мультиплексор 4 начинает опрос кода по три разряда. По нарастаклчему фронту тактового сигнапа с входа 8 на счетном входе меняется состояние счетчика 2 и кодо- йая комбинация на адресных входах мультиплексора 4, По низкому уровню тактового сигнала опрашиваемые три разряда кода передаются -на входы Сумматора 6, Если в проверяе1 Юм

П-разрядном коде не содержится ни одной 1, то на выходе дешифратора

5нуля формируется сигнал логической 1, который поступает через элемент ИЛИ 1 на вход 10 устройства в качестве сигнала ошибки. Если в проверяемом коде содержится одна 1,

то на выходе 10 сигнал ошибки не появится. Если в проверяемом коде содержится больше одной 1, то воз- можны два варианта работы устройства Первый вариант: если две или более I содержатся в одновременно опрашиваемых трех разрядах кода, в этом случае на выходе переноса сумматора

6появляется логическая 1, которая через элемент.ИЛИ 1 поступает на выход Ю устройства в качестве сигнап:а ошибки. Второй вариант: если по одно

Г содержится в нескольких последовательно опрашиваемых тройках разрядов, в этом случае сигнал с выхода суммь: сумматора 6 поступает на счетный вход счетчика 3, и сигнал ошибки на выходе 10 формируется при появлении логической 1 на выходе второго разряда счетчика 3,

Дпя случая, когда , , и т,д,, т,е, когда п не кратно трем на входы мультиплексора 4, дополняю щие до кратности трем, постоянно подаются нулевые сигналы.

Таким образом, в устройстве реализуется анализ одновременно нескольких разрядов контролируемого-кода fтрех разрядов) за один период тактовой частоты.

Формула изобретения

Устройство для контроля кода 1 из п, содержащее счетчики импульсов, мультиплексор и дешифратор нуля выход которого соединен с первым входом элемента ИЛИ, выход которого является выходом устройства, выходы разрядов первого счетчика импульсов соединенные с соответствунядими адресными входами мультиплексора, выход второго счетчика импульсов соединен с вторым входом элемента ИЛИ, счетчный вход первого счетчика импульсов объединен с управляющим входом мультиплексора и является управляющим входом устройства, входы дешифратора нуля объединены с соответствующими информационными входами мультиплексора и являются информационными входами устройства, входы установки первого и второго счетчиков импульсов объединены и являют ся входом установки устройства, о т личающе еся тем, что, с целью поизшения быстродействия устройства, в него введен сумматор, вы ход суммы которого соединен со счетным входом второго счетчика импульсов, выходы мультиплексора соединены с соответствующими входами сумматора, выход переноса которого соединен с третьим входом элемента ИЛИ,

| Устройство контроля кода "1 из @ | 1984 |

|

SU1195451A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля кода "1 из N | 1986 |

|

SU1345353A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-09-23—Публикация

1988-02-01—Подача