Изобретение относится к вычислительной технике, в частности к созданию электрически перепрограммируемых запоминающих устройств (ЗППЗУ), способных сохранять информацию после отключения питающего напряжения.

Цель изобретения - повышение надежности и времени хранения информации.

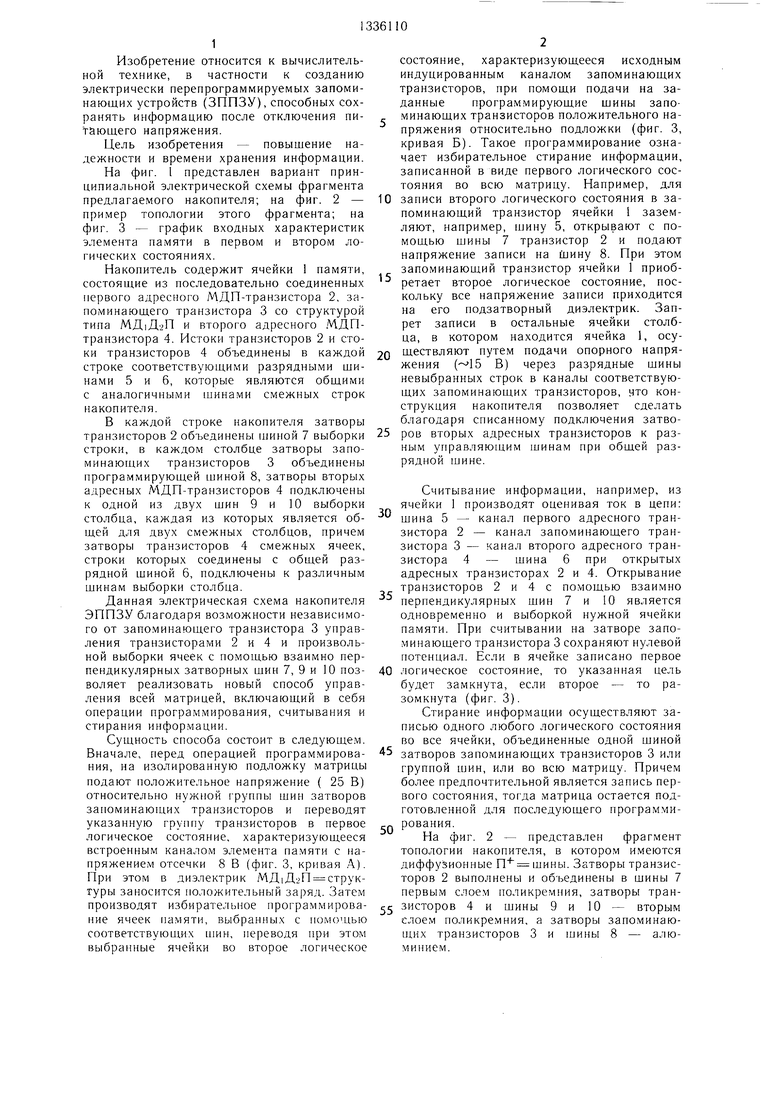

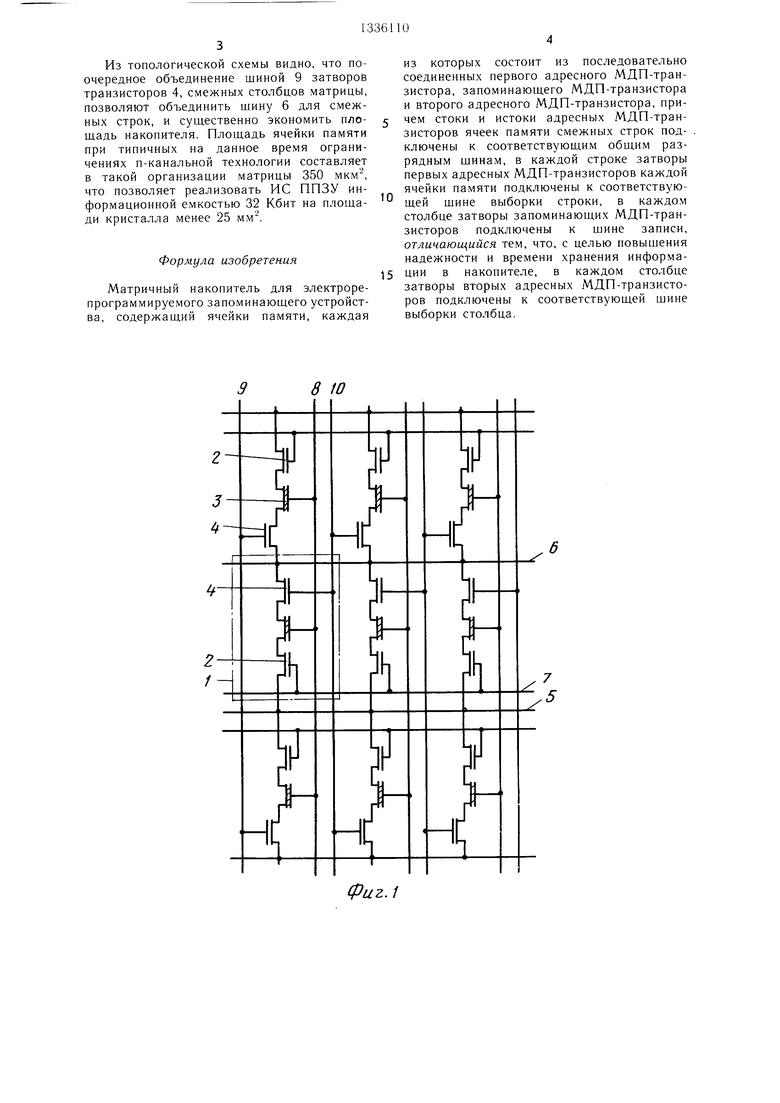

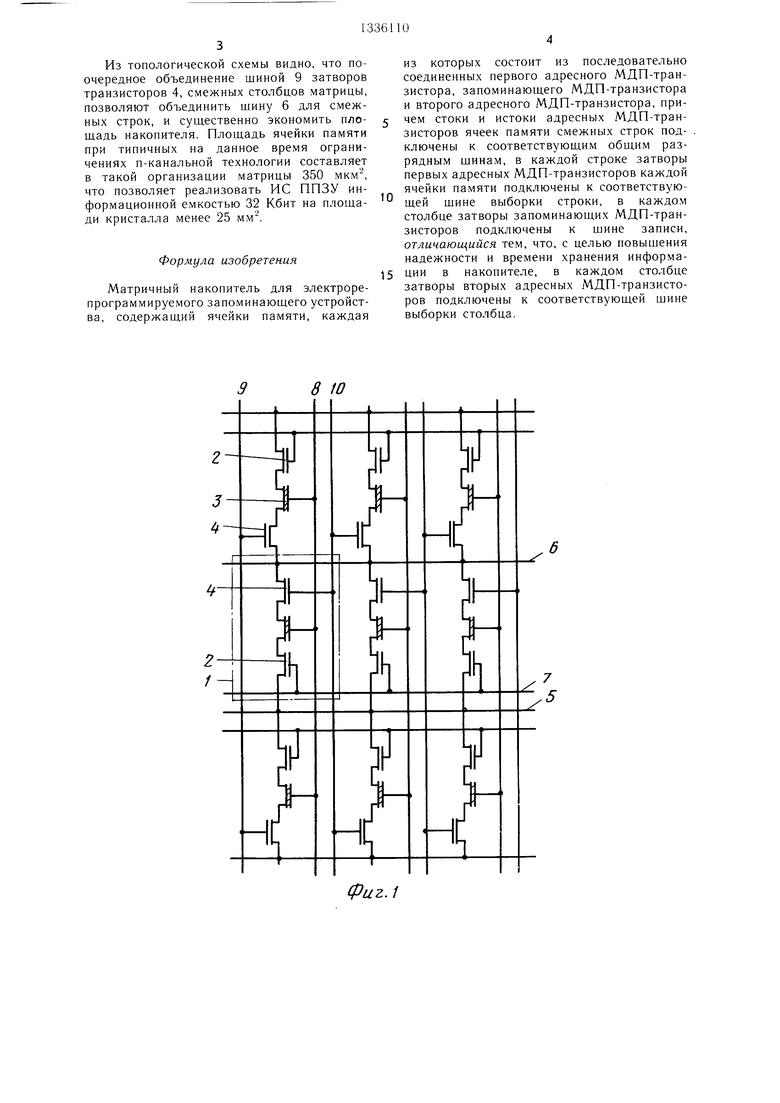

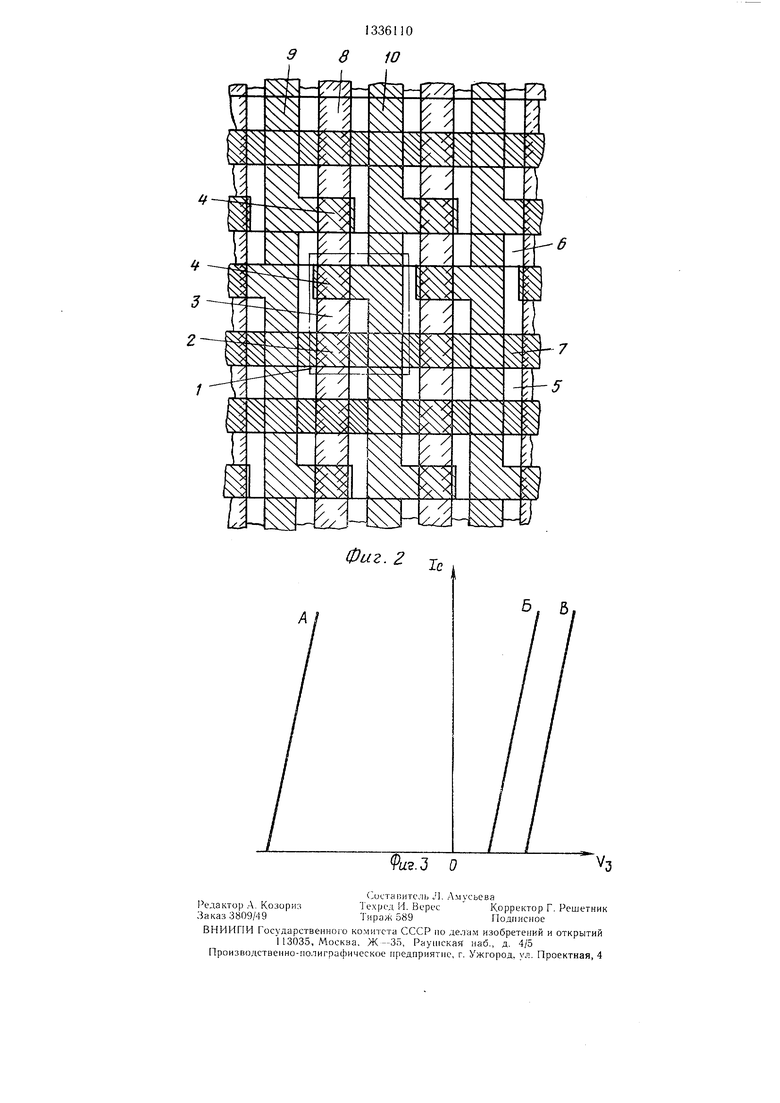

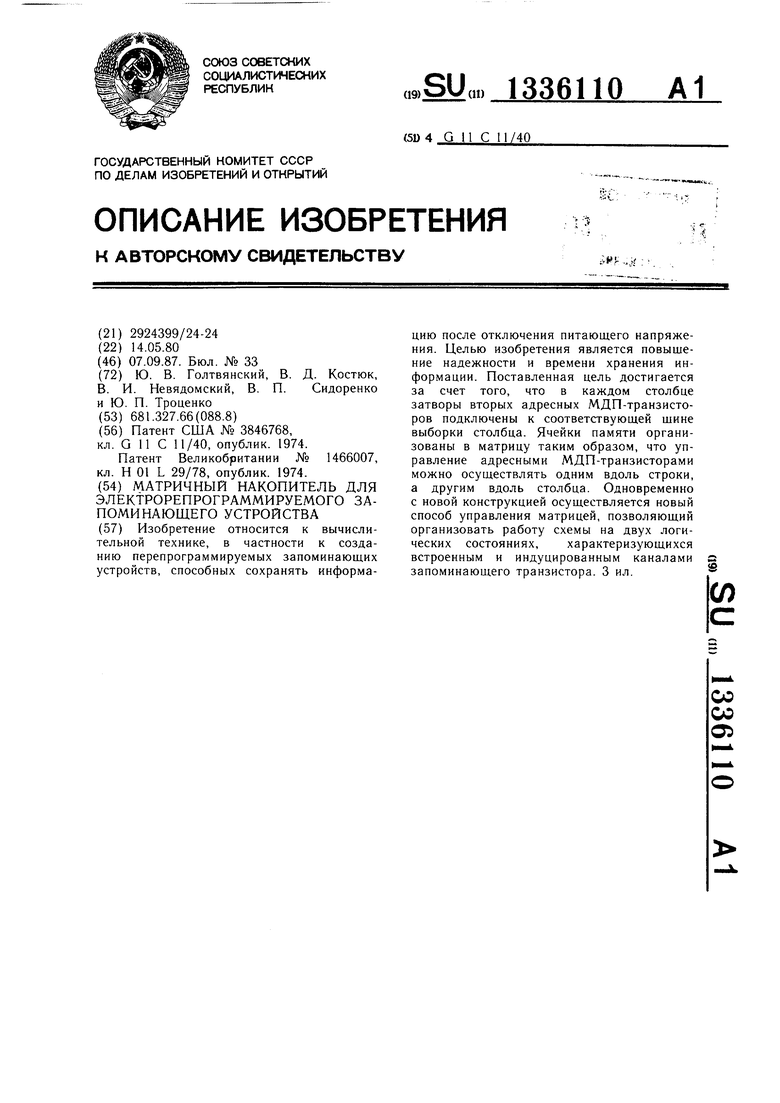

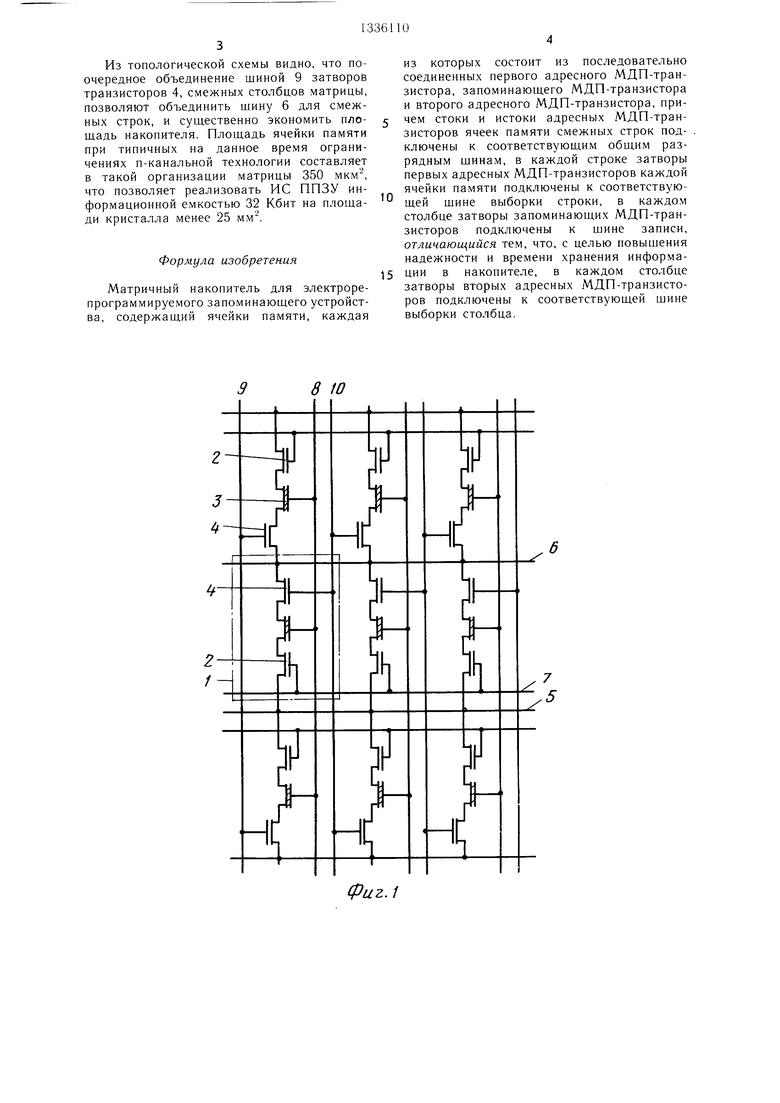

На фиг. 1 представлен вариант принципиальной электрической схемы фрагмента предлагаемого накопителя; на фиг. 2 - пример топологии этого фрагмента; на фиг. 3 - график входных характеристик элемента памяти в первом и втором логических состояниях.

Накопитель содержит ячейки 1 памяти, состоящие из последовательно соединенных первого адресного МДП-транзистора 2, запоминающего транзистора 3 со структурой типа МД|Д2П и второго адресного МДП- транзистора 4. Истоки транзисторов 2 и стоки транзисторов 4 объединены в каждой строке соответствующими разрядными щи- нами 5 и 6, которые являются общими с аналогичными шинами смежных строк накопителя.

В каждой строке накопителя затворы транзисторов 2 объединены шиной 7 выборки строки, в каждом столбце затворы запоминающих транзисторов 3 объединены программируюихей шиной 8, затворы вторых адресных МДП-транзисторов 4 подключены к одной из двух тин 9 и 10 выборки столбца, каждая из которых является общей для двух смежных столбцов, причем затворы транзисторов 4 смежных ячеек, строки которых соединены с общей разрядной щиной 6, подключены к различным щинам выборки столбца.

Данная электрическая схема накопителя ЭППЗУ благодаря возможности независи.мо- го от запоминающего транзистора 3 управления транзисторами 2 и 4 и произвольной выборки ячеек с помощью взаимно перпендикулярных затворных щин 7, 9 и 10 позволяет реализовать новый способ управления всей матрицей, включающий в себя операции программирования, считывания и стирания инфор.мации.

Сущность способа состоит в следующе.м. Вначале, перед операцией программирования, на изолированную подложку матрицы

подают положительное напряжение ( 25 Б) относительно нужной группы шин затворов запоминающих транзисторов и переводят указанную группу транзисторов в первое логическое состояние, характеризующееся встроенным каналом элемента памяти с напряжением отсечки 8 В (фиг. 3, кривая А). При этом в диэлектрик МД1Д2П структуры заносится положительный заряд. Затем производят избирательное программирование ячеек памяти, выбранных с помощью соответствующих тин, переводя при этом выбранные ячейки во второе логическое

0

5

0

5

0

5

0

5

0

5

состояние, характеризующееся исходным индуцированным каналом запоминающих транзисторов, при помощи подачи на заданные программирующие щины запоминающих транзисторов положительного напряжения относительно подложки (фиг. 3, кривая Б). Такое программирование означает избирательное стирание информации, записанной в виде первого логического состояния во всю матрицу. Например, для записи второго логического состояния в запоминающий транзистор ячейки 1 заземляют, например, щину 5, открывают с помощью щины 7 транзистор 2 и подают напряжение записи на илину 8. При этом запоминающий транзистор ячейки 1 приобретает второе логическое состояние, поскольку все напряжение записи приходится на его подзатворный диэлектрик. Запрет записи в остальные ячейки столбца, в котором находится ячейка 1, осуществляют путем подачи опорного напряжения ( В) через разрядные щины невыбранных строк в каналы соответствующих запоминающих транзисторов, что конструкция накопителя позволяет сделать благодаря списанному подключения затворов вторых адресных транзисторов к разным управляющим щинам при общей разрядной шине.

Считывание информации, напри.мер, из ячейки 1 производят оценивая ток в цепи: шина 5 - канал первого адресного транзистора 2 - канал запоминающего транзистора 3 - канал второго адресного транзистора 4 - шина б при открытых адресных транзисторах 2 и 4. Открывание транзисторов 2 и 4 с помощью взаимно перпендикулярных щин 7 и 10 является одновременно и выборкой нужной ячейки памяти. При считывании на затворе запоминающего транзистора 3 сохраняют нулевой потенциал. Если в ячейке записано первое логическое состояние, то указанная цель будет замкнута, если второе - то разомкнута (фиг. 3).

Стирание информации осуществляют записью одного любого логического состояния во все ячейки, объединенные одной щиной затворов запоминающих транзисторов 3 или группой щин, или во всю матрицу. Причем более предпочтительной является запись первого состояния, тогда матрица остается подготовленной для последующего программирования.

На фиг. 2 - представлен фрагмент топологии накопителя, в котором имеются диффузионные П щины. Затворы транзисторов 2 выполнены и об ьединены в щины 7 первым слоем поликремния, затворы транзисторов 4 и шины 9 и 10 - вторым слоем поликремния, а затворь запоминающих транзисторов 3 и шины 8 - алюминием.

Из топологической схемы видно, что поочередное объединение шиной 9 затворов транзисторов 4, смежных столбцов матрицы, позволяют объединить шину 6 для смежных строк, и существенно экономить пло- шадь накопителя. Площадь ячейки памяти при типичных на данное время ограничениях п-канальной технологии составляет в такой организации матрицы 350 мкм -, что позволяет реализовать ИС ППЗУ информационной емкостью 32 Кбит на площади кристалла менее 25 мм.

Формула изобретения

Матричный накопитель для электроре- программируемого запоминающего устройства, содержащий ячейки памяти, каждая

из которых состоит из последовательно соединенных первого адресного МДП-тран- зистора, запоминающего МДП-транзистора и второго адресного МДП-транзистора, причем стоки и истоки адресных МДП-тран- зисторов ячеек памяти смежных строк подключены к соответствующим общим разрядным щинам, в каждой строке затворы первых адресных МДП-транзисторов каждой ячейки памяти подключены к соответствующей щине выборки строки, в каждом столбце затворы запоминающих МДП-транзисторов подключены к шине записи, отличающийся тем, что, с целью повыщения надежности и времени хранения информации в накопителе, в каждом столбце затворы вторых адресных МДП-транзисторов подключены к соответствующей шине выборки столбца.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| НАКОПИТЕЛЬ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1995 |

|

RU2106022C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

Изобретение относится к вычислительной технике, в частности к созданию перепрограммируемых запоминающих устройств, способных сохранять информацию после отключения питающего напряжения. Целью изобретения является повышение надежности и времени хранения информации. Поставленная цель достигается за счет того, что в каждом столбце затворы вторых адресных МДП-транзисто- ров подключены к соответствующей щине выборки столбца. Ячейки памяти организованы в матрицу таким образом, что управление адресными МДП-транзисторами можно осуществлять одним вдоль строки, а другим вдоль столбца. Одновременно с новой конструкцией осуществляется новый способ управления матрицей, позволяющий организовать работу схемы на двух логических состояниях, характеризующихся встроенным и индуцированным каналами запоминающего транзистора. 3 ил. ё (Л со 00 05

8 W

Фиг.1

р

Фиг. 2 J,

Риг.Л О

V3

Корректор Г. Решетник Подписное

Редактор А. КозоризТехред И. Верес

Заказ 3809/49Тираж 589

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, A locKsa, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(Доставитель Л. Лмусьева

Корректор Г. Решетник Подписное

| Патент США № 3846768, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Устройство контроля исправности счетчика | 1987 |

|

SU1466007A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1987-09-07—Публикация

1980-05-14—Подача