Изобретение относится к вычислительной технике и может быть использовано для создания постоянных (ПЗУ) и репрограммируемых (РПЗУ) запоминающих устройств повышенной информационной емкости на основе МДП-структур.

Одним из важнейших параметров накопителей полупроводниковых ЗУ с энергонезависимым хранением информации является информационная емкость. Известны наиболее плотнокомпонуемые в интегральном исполнении, так называемые бесконтактные накопители [1, 2] в которых контакты между диффузионными разрядными шинами и шунтирующими их алюминиевыми шинами выполняют на относительно большом расстоянии друг от друга, как правило, через каждые 16 элементов памяти.

В качестве прототипа выбран накопитель запоминающего устройства [3] выполненный на полупроводниковой подложке в виде матрицы запоминающих МДП-транзисторов, сток-истоковые электроды которых подключены к соответствующим разрядным шинам, направленным вдоль столбцов матрицы, а затворы подключены к адресным шинам, направленным вдоль строк матрицы. В интегральном исполнении на кремниевой подложке контакты между диффузионными и шунтирующими их алюминиевыми шинами сформированы периодически между группами поликремниевых адресных шин. При этом в прототипе контакты расположены в шахматном порядке, т. е. для каждой диффузионной шины через две группы адресных шин, а для двух смежных с ней диффузионных шин также через две группы адресных шин, но со сдвигом на одну группу. Каждая диффузионная шина и соответствующая ей алюминиевая шина расположены параллельно одна другой, и количество диффузионных шин равно числу металлических шин. В качестве запоминающих элементов в этом накопителе используют, например. МДП-транзисторы с плавающим затвором, запись информации в которые осуществляется канальной инжекцией горячих электронов, а стирание ультрафиолетовым (УФ) облучением.

В накопителе данной конструкции, в частности прототипе, критичным размером, ограничивающим дальнейшую минимизацию площади накопителя по оси, параллельной столбцам матрицы, является шаг по шинам металлизации (ширина мины плюс зазор). Сложность травления алюминиевой пленки приводит к тому, что минимальный шаг шин металлизации превышает аналогичный параметр для пленок других материалов, используемых в МДП-технологии, примерно в полтора раза, а это препятствует дальнейшему повышений плотности компоновки накопителя.

Настоящее изобретение направлено на устранение этого недостатка и повышение плотности накопителя в интегральном исполнении.

Получение запланированного результата достигается тем, что во фрагментах накопителя разрядные шины попарно объединены между собой таким образом, что произвольная разрядная шина с порядковым номером i объединена с разрядной шиной, имеющей порядковый номер i-j или i+j в зависимости от четности или нечетности номера i, где j=3,

В интегральном исполнении на кремниевой подложке столбцовые разрядные шины выполнены диффузионными, адресные строчные шины из поликремния, а попарное объединение диффузионных шин произведено алюминиевыми шинами зигзагообразной формы с помощью контактных окон, выполненных к диффузионным шинам в промежутках между группами адресных шин.

Оптимальным значением числа j с точки зрения компоновки является 3, что в дальнейшем и будет использоваться.

Разрядные шины накопителя в целом могут быть сформированы в виде последовательности изолированных друг от друга отрезков диффузионных шин, располагаемых по накопителю в шахтном порядке, каждый из которых пересечен двумя группами адресных шин и имеет между ними контакт к алюминиевой шине, а зазоры между отрезками диффузионных шин расположены между контактами алюминиевых шин к двум отрезкам диффузионных шин, принадлежащих двум смежным столбцам матрицы, при этом алюминиевые шины соединяют отрезки диффузионных шин вдоль столбцов матрицы таким образом, что любой отрезок, относящийся к i-му столбцу матрицы, соединен с двумя ближайшими отрезками, относящимися к столбцу с порядковым номером i-3 или i+3 в зависимости от четности или нечеткости номера i.

Положительный эффект при использовании данного технического решения достигается за счет того, что в предлагаемой конструкции шаг металлизации практически в два раза свободнее аналогичного параметра для диффузионных разрядных шин. Это позволит увеличить плотность информации в накопителе. В предлагаемой конструкции шаг металлизации уже не является параметром, ограничивающим плотность информации. Как будет показано ниже, предлагаемая конструкция позволяет осуществлять индивидуальную выборку каждого элемента памяти при записи и считывании информации.

В случае, когда разрядные шины накопителя в целом сформированы в виде последовательности изолированных друг от друга зазорами отрезков диффузионных шин, взаимное расположение контактных окон и зазоров между торцами отрезков диффузионных шин устраняет жесткие ограничения на размеры и величину рассовмещения, контактных окон. В такой конструкции размер элементов памяти по строкам матрицы определяется длиной канала транзисторов и ограничениями по ширине диффузионных разрядных шин. Увеличение информационной плотности накопителя за счет использования предлагаемой конструкции составляет 30-40%

Неизвестны конструкции матричных накопителей для интегральных схем постоянной памяти с одноуровневой металлизирующей разводкой, в которых одна шина металлизации шунтирует две диффузионные разрядные шины, и при этом имеется возможность производить индивидуальную выборку каждого элемента памяти при записи и считывании информации. Таким образом, предлагаемая конструкция обладает существенным отличием.

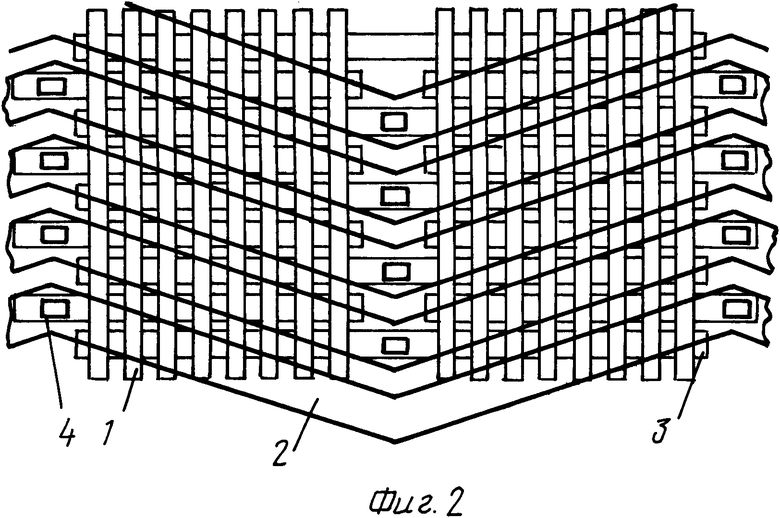

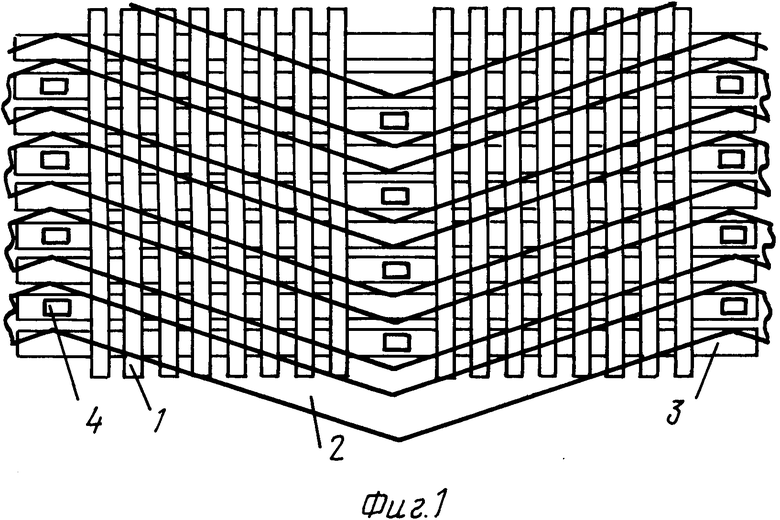

На фиг. 1 представлен фрагмент топологического построения предлагаемого накопителя в интегральном исполнении, где 1 адресная поликремниевая шина, 2 шина металлизации, 3 диффузионная разрядная шина, 4 контактное окно; на фиг. 2 случай, когда фрагменты диффузионных разрядных шин выполнены в виде отрезков, расположенных в шахматном порядке; на фиг.3 принципиальная электрическая схема фрагмента накопителя запоминающего устройства для частного случая, когда ячейки памяти выполнены в виде МДП-транзисторов с плавающим затвором, перекрывающим часть канала со стороны стоковой области, где C1-C9 - ячейки памяти, B1-B5 шины металлизации, A1 и A2 адресные шины.

Рассмотрим работу фрагмента накопителя РПЗУ на основе ячеек памяти с плавающим затвором (фиг. 3), имея при этом в виду, что она аналогична для обоих вариантов, изображенных на фиг. 1 и 2.

Если на разрядную шину B3 и затворную шину A1 подать программирующие напряжения, соответственно Up и Upp например, Up=8B, Upp=12B, а все остальные шины обнулить, произойдет одновременная запись информации в ячейки памяти C4 и C7. Для запрета записи в ячейку памяти C4 на шину В1 необходимо подать напряжение Ui такой величины, чтобы выполнялось соотношение 0<Uso<Ui<Udo<Up, где Uso минимальное напряжение на истоке, при котором отсутствует запись в ячейку памяти с напряжением на стоке, равном Up, Udo - максимальное напряжение на стоке, при котором отсутствует запись в ячейку памяти с нулевым напряжением на истоке. Как правило, этому требованию соответствует значение Ui= Up/2. Аналогично, для запрета записи в ячейку C7 напряжение Up/2 необходимо подать на шину В4.

При считывании информации одну из разрядных шин, например, B3 обнуляют, а на все остальные разрядные шины подают напряжение Urr, например, 2В. На выбранную затворную шину A1 подают напряжение Ucc, например, 5В. Токи считывания через ячейки памяти C4, C5, C7 и C8 измеряют соответственно на шинах В1, В2, В4 и В5. Для исключения влияния сопротивления диффузионных разрядных шин, которое в режиме считывания может приводить к протеканию паразитного тока через шины металлизации, соответствующие ячейкам памяти с высоким значением порогового напряжения, напряжение Ur должно быть достаточно большим, например, 2В или более.

Библиографические данные

1. Патент США N 4597060, кл. G 11 C 11/40, 365/185, 365/189, 1989.

2. Esguivel J. et al, "High density contactless self aligned EPROM cell array technology," IEDM Tech. Dig. 1986, pp. 592-595.

3. Патент США N 4760554, кл. G 11 C 13/00, 365/51, 365/189. 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

| Ячейка памяти для ОЗУ с энергонезависимым хранением информации (ее варианты) | 1982 |

|

SU1161989A1 |

| Ячейка памяти | 1976 |

|

SU681455A1 |

Накопитель запоминающего устройства относится к бесконтактным накопителям энергонезависимых ячеек памяти и может быть использовано в микроэлектронике для создания ПЗУ, РПЗУ, и ЭРПЗУ повышенной информационной емкости. Технический результат достигается тем, что используется коммутация ячеек памяти накопителя, которая позволяет в два раза уменьшить количество шин металлизации. Это становится возможным благодаря тому, что каждая шина металлизации, имеющая зигзагообразную форму, шунтирует две диффузионные с порядковыми номерами i и i-3 или i+3 в зависимости от четности или нечетности номера i. При этом обеспечивается индивидуальная выборка каждой ячейки памяти при программировании и считывании. Диффузионные разрядные шины разделены на изолированные друг от друга отрезки, причем зазоры между отрезками диффузионных шин расположены между контактами шин металлизации к отрезкам двух смежных диффузионных шин. Техническое решение позволяет увеличить допуск на уход размеров и рассовмещение слоев на этапе формирования контактных окон и слоя металлизации и повысить плотность информации в накопителе. 2 з.п. ф-лы, 3 ил.

| US, патент, 4597060, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| US, патент, 4760554, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1998-02-27—Публикация

1995-03-29—Подача