Изобретение относится к импульсной технике и может быть использовано при построении различных цифровых ИС с парафазными выходами.

Целью изобретения является уменьшение асимметрии выходных сигналов, снижение уровня логического нуля и повьшение нагрузочной способности по инверсному выходу.

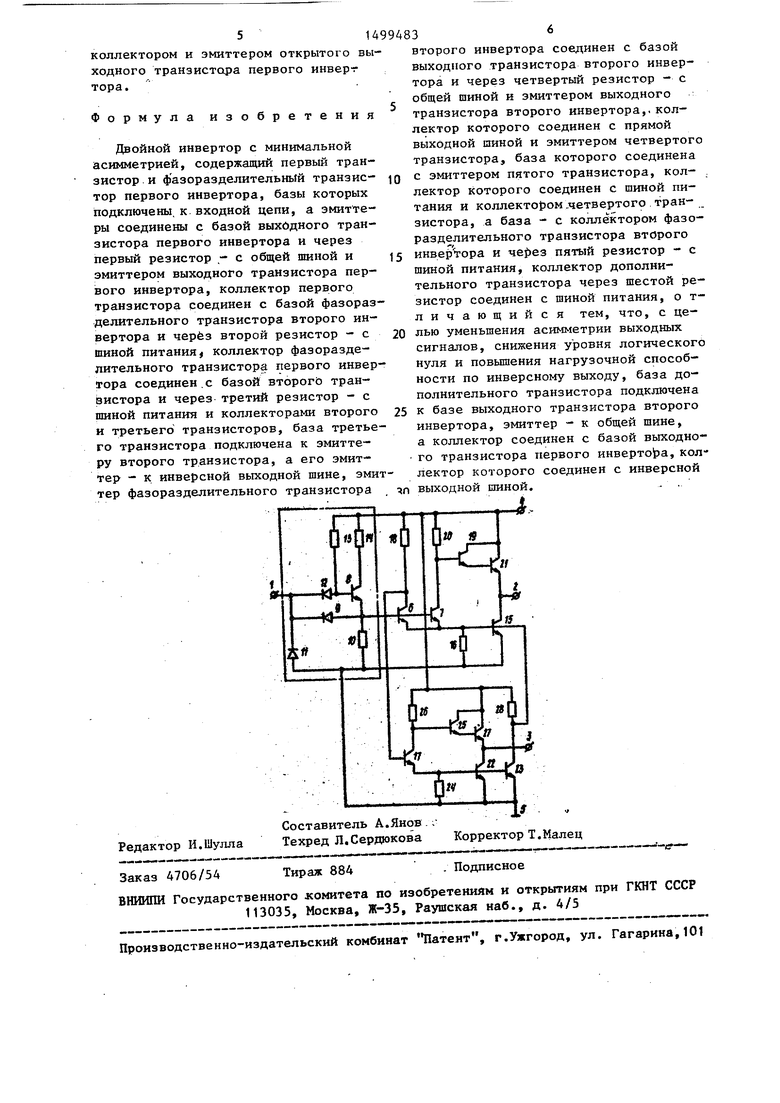

На чертеже представлена электрическая принципиальная схема двойного инвертора с минимальной асимметрией.

Двойной инвертор с минимальной асимметрией содержит шину 1, инверсную выходную 2 и прямую выходную 3 шины, шину 4 питания, общую шину 5, первый транзистор 6 и фазораздели-. тельный транзистор 7 первого инвертора, базы которых соединены вместе и подключены к эмиттеру входного транзистора 8, аноду первого диода 9 Шот- тки и через седьмой резистор 10 к общей шине 5 и аноду второго диода 11 Шоттки, катод которого подключен к катоду первого диода 9 Шоттки, входной шине 1 и катоду третьего диода 12, анод которого.подключен к базе входного транзистора 8 и через восьмой резистор 13 к шине 4 питания и выводу девятого резистора 14, второй вод которого соединен с коллектором входного транзистора 8, эмиттеры первого 6 и фазоразделительного 7 транзисторов первого инвертора соединены с базой выходного транзистора 15 первого инвертора и через первый резистор 16 с общей шиной 5 и эмиттером транзистора 15, коллектор транзистора 6 соединен с базой фазоразделительного транзистора 17 второго инвертора и через второй резистор 18 с шиной 4 питания, коллектор транзистора 7 соединен с базой второго траи- и :тора 19.и через третий резистор 20

4 СО СГ 4 (Х

сс

сГшиной 4 питания и коллекторами второго 19 и третьего 21 транзисторов, база третьего транзистора 21 подключена к эмиттеру второго транзисто-. ра 19, а его эмиттер - к инверсной выходной шине 2 и коллектору транзистора 15, эмиттер транзистора 17 соединен с базой выходного транзистора 22 второго инвертора и базой дополнительного транзистора 23, эмиттеры которых подключены к общей шине -5 и через четвертый резистор 24 к эмиттеру фазоразделительного транзистора 17 второго инвертора, коллектор которого подключен к базе пятого транзистора 25 и через пятый резистор 26 к шине 4 питания, коллектору четвертого транзистора 27 и коллектору пятого транзистора 25, эмиттер которого подключен к базе четвертого транзистора 27, эмиттер которого подключен к прямой выходной шине 3 и коллектору транзистора 22. Коллектор транзист ора 23 соединен с базой транзистора 15 и через шестой резистор 28 с шиной питания.

Двойной инвертор работает следующим образом.

Если на входную пшну 1 подан низкий уровень напрйжения, то диод 12 открыт, а транзисторы 8,6,7 и 15 закрыты, так как отсутствует ток в базовых цепях этих транзисторов. На инверсной выходной шине 2 сформируется высокий уровень напряжения, определяемый открытыми транзисторами 19 и 21. Высокий уровень напряжения на коллекторе закрытого транзистора 6 приводит к появлению тока в базовой цени транзистора 17. Транзистор 17 открьюается и начинает протекать ток через резистор 26, образующий базовый ток транзисторов 22 и 23. Открытый транзистор 22 формирует на прямой выходной шине 3 низкий уровень напряжения. Открытый транзистор 23 устаг-.; навливает на базе транзистора 15 уровень напряжения, равный напряжению между коллектором и эмиттером открытого транзистора 23. Таким образом, при наличии на шине 1 низкого уровня напряжения на шине 2 формируется высокий уровень напряжения, а на шине 3 - низкий уровень напряжения. При изменении на шине 1 напряжения с низ кого уровня на высокий диод 12 закрывается, в базу транзистора 8 поступает ток от шины 4 питания через

0

5

0

5

0

5

0

5

0

5

резистор 13, транзистор 8 открывается, начинает протекать ток через резистор 14 в базу транзисторов 6 и 7, они открьшаются, в коллекторных цепях этих транзисторов появляются токи, определяемые резисторами 18 и 20 соответственно, которые поступают через коллектор - эмиттер открытого транзистора 23 в общую шину 5. Таким образом, транзистор 15 продолжает оставаться закрытым, поскольку открытый транзистор 23 удерживает на его базе напряжение, недостаточное для отпирания транзистора 15.

При выключении транзистора 17 происходит выключение транзистора 22 и начинается переход на шине 3 от низкого уровня напряжения к высокому. Транзистор 23 начинает выключаться одновременно с транзистором 22, и при возрастании на его коллекторе напряжения до величины напряжения отпирания перехода база - эмиттер транзистора 15 в базу транзистора 15 начинает поступать ток от шины 4 питания через резистор 28 и резисторы 18 и 20, приводящий к открыванию транзистора 15 и установлению на выходе 2 низкого уровня напряжения. На выходе 3 при этом устанавливается высокий уровень напряжения, определяемый открытыми транзисторами 25 и 27. Таким образом, появление низкого уровня напряжения на выходе 2 согласовано по времени с появлением высокого уровня напряжения на выходе 3. Анти- звонный диод 11 в схеме предназначен для ограничения величины отрицательных помех на входе схемы. Диод 9 и резистор 10 образуют цепи выключения транзисторов 6 и 7. Резисторы 16 и 24 обеспечивают цепи выключения транзисторов 15 и 22, 23 соответственно.

Таким образом, введение обратной связи между выходными транзисторами 22 и 15 приводит к тому, что низкий уровень напряжения на инверсном выходе 2 схемы начинает фop Iиpoвaтьcя в момент перехода прямого выхода 3 от низкого уровня к высокому. Следовательно, устраняется асимметрия между сигналом на шине 2 и сигналом на шине 3 при переходе входного сигнала на шине 1 от низкого уровня напряжения высокому. Величина низкого уровня напряжения на инверсном выходе равна напряжению между

Редактор И.Шулла Заказ 4706/54

Составитель А.Янов. ,Техред Л.Сердюкова Корректор Т.Малец

Тираж 884

. Подписное

. Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| Маломощный транзисторный логический элемент | 1988 |

|

SU1598157A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Формирователь импульсов (его варианты) | 1980 |

|

SU974562A1 |

| Логический элемент | 1985 |

|

SU1275758A1 |

Изобретение относится к импульсной технике и может быть использовано в вычислительной технике и системах повышенной производительности. Целью изобретения является уменьшение асимметрии выходных сигналов, снижение уровня логического нуля и повышение нагрузочной способности по инверсному выходу путем применения обратной связи между выходными транзисторами схемы. Инвертор содержит входную цепь, два инвертора и дополнительный транзистор, база которого подключена к базе выходного транзистора второго инвертора, эмиттер - к общей шине, а коллектор соединен с базой выходного транзистора и через резистор с шиной питания. 1 ил.

| Патент США Р 3962589, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1984-12-28—Подача