Фиг.1

Изобретение относится к вычислительной технике и предназначено доя реализации обработки информации в конвейерном режиме в реальном времени и в режиме множественных потоков команд и данных, при-этом межпроцессорный обмен в системе осуществляется асинхронное

Цель изобретения - повышение про- {изводительности при одновременном уменьшении аппаратурных затрат и упрощении процедуры межпроцессорного

обмена

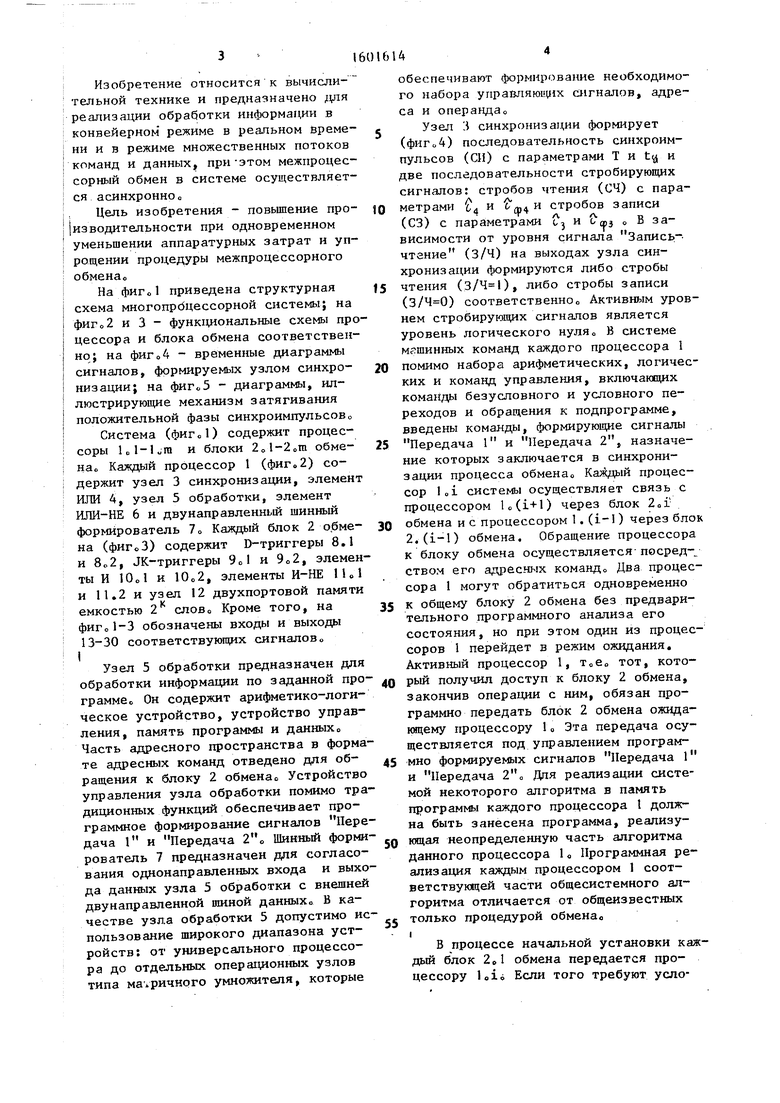

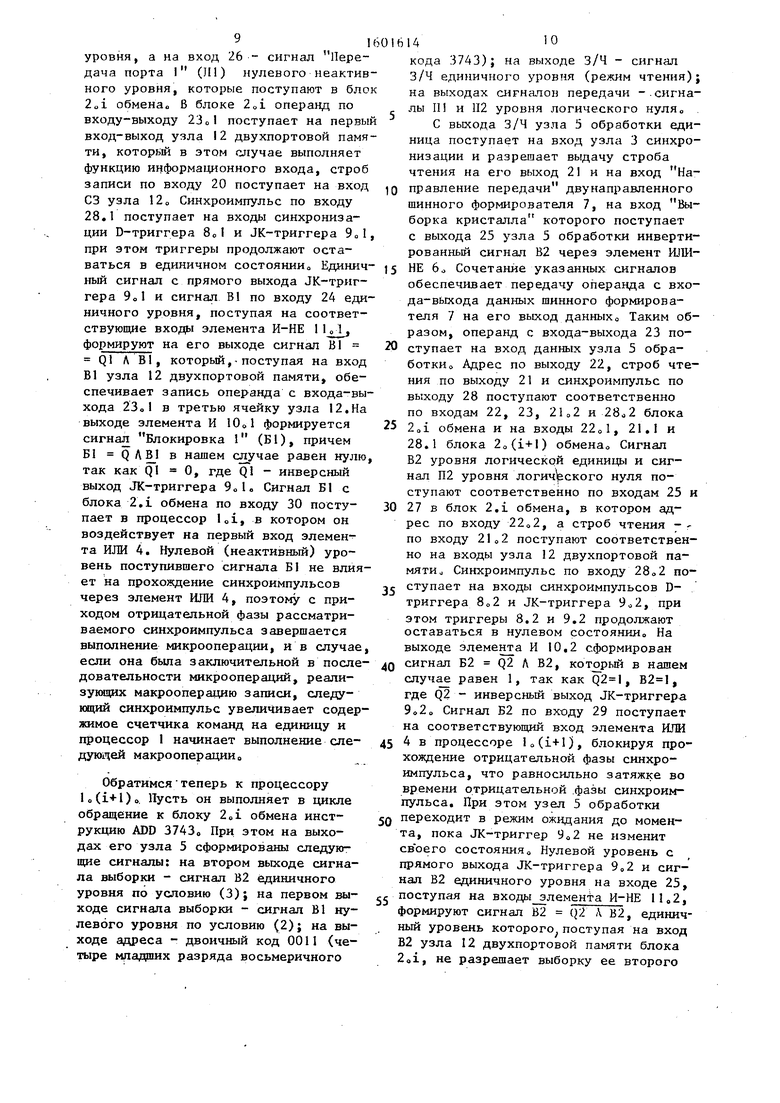

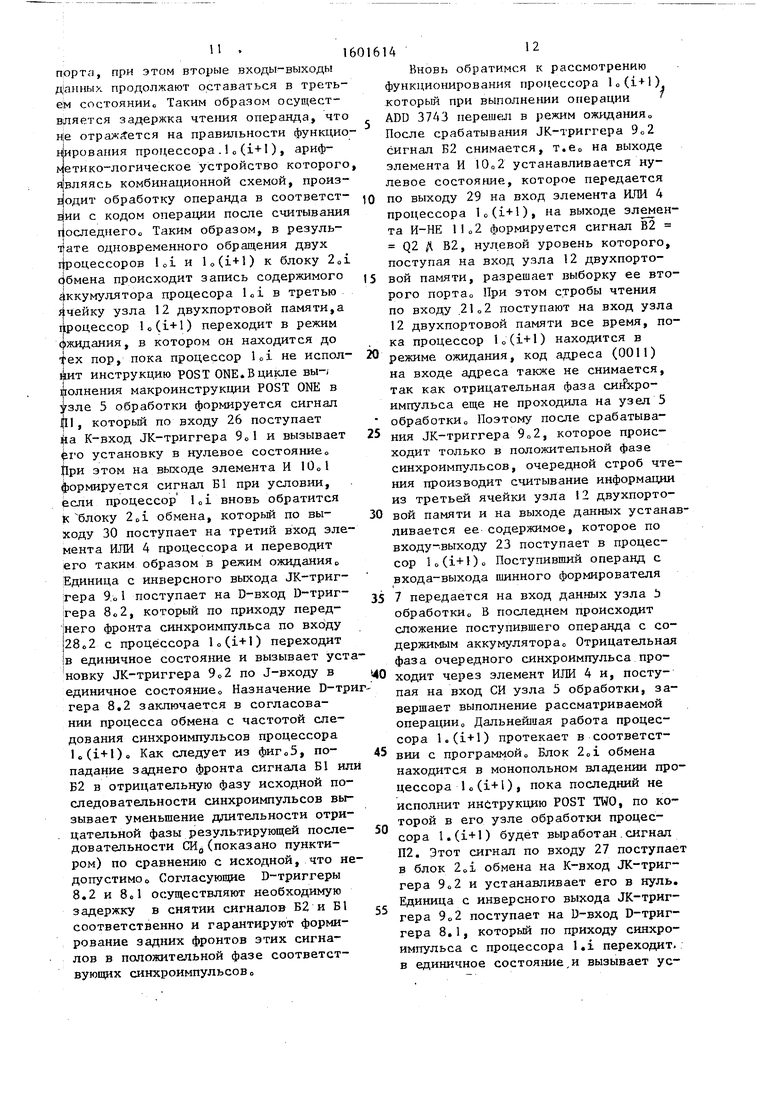

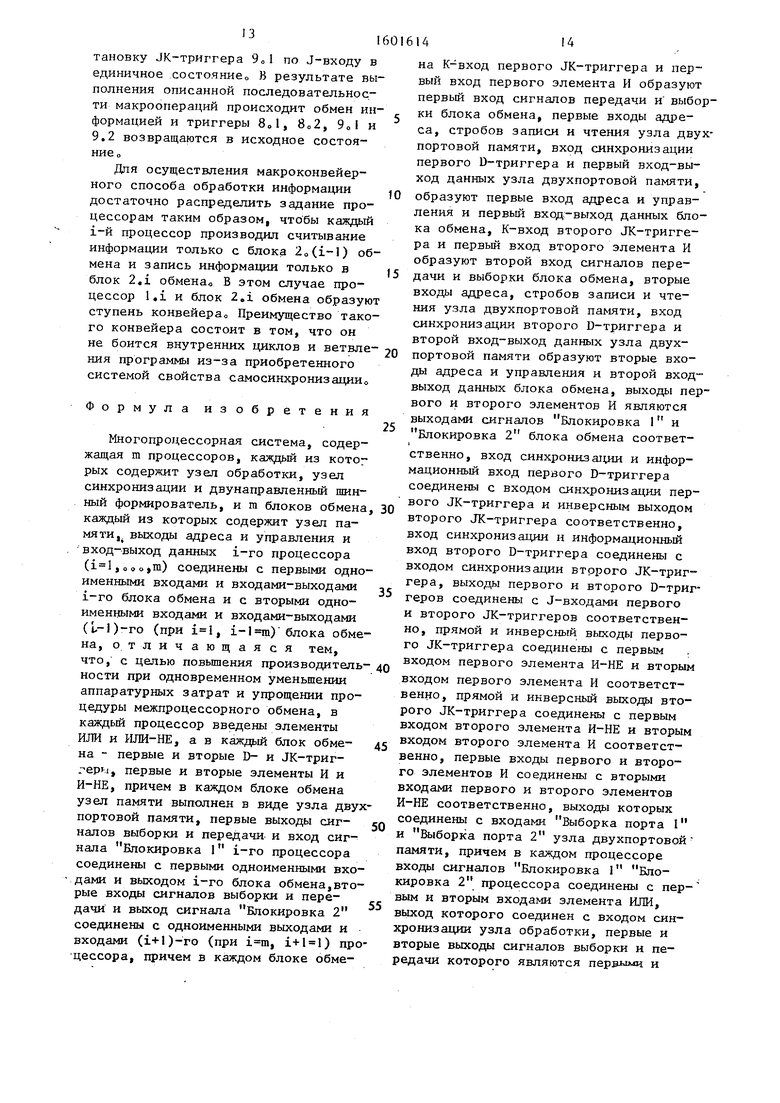

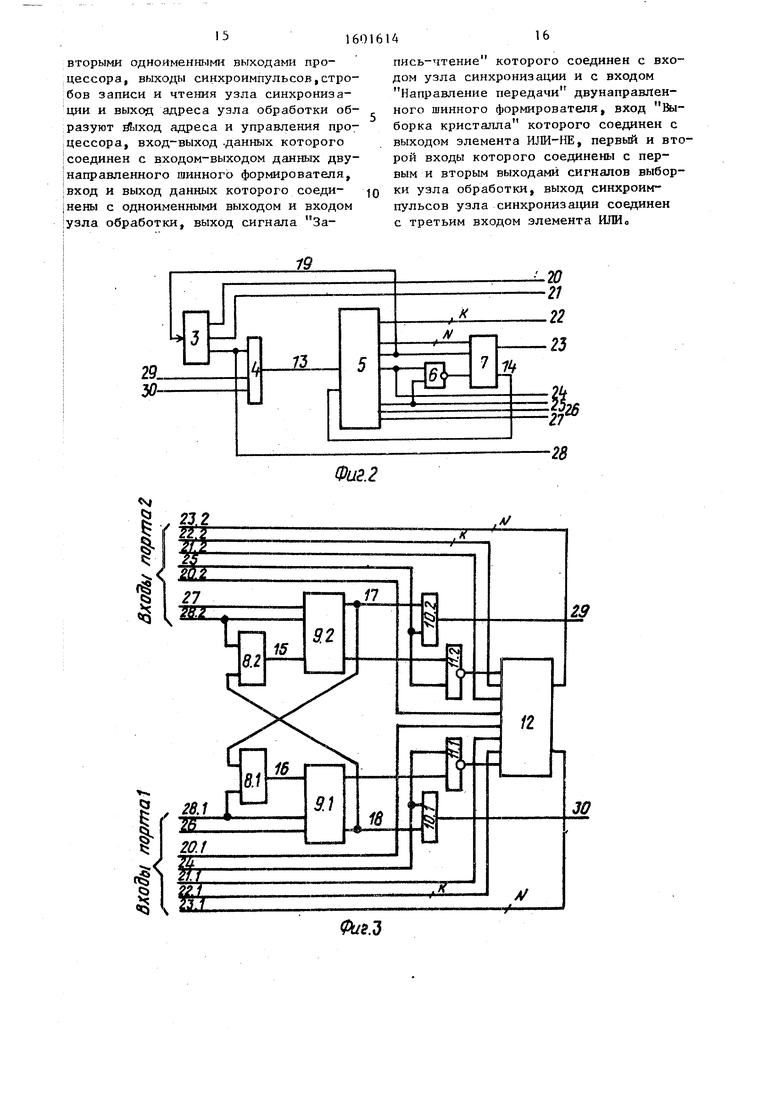

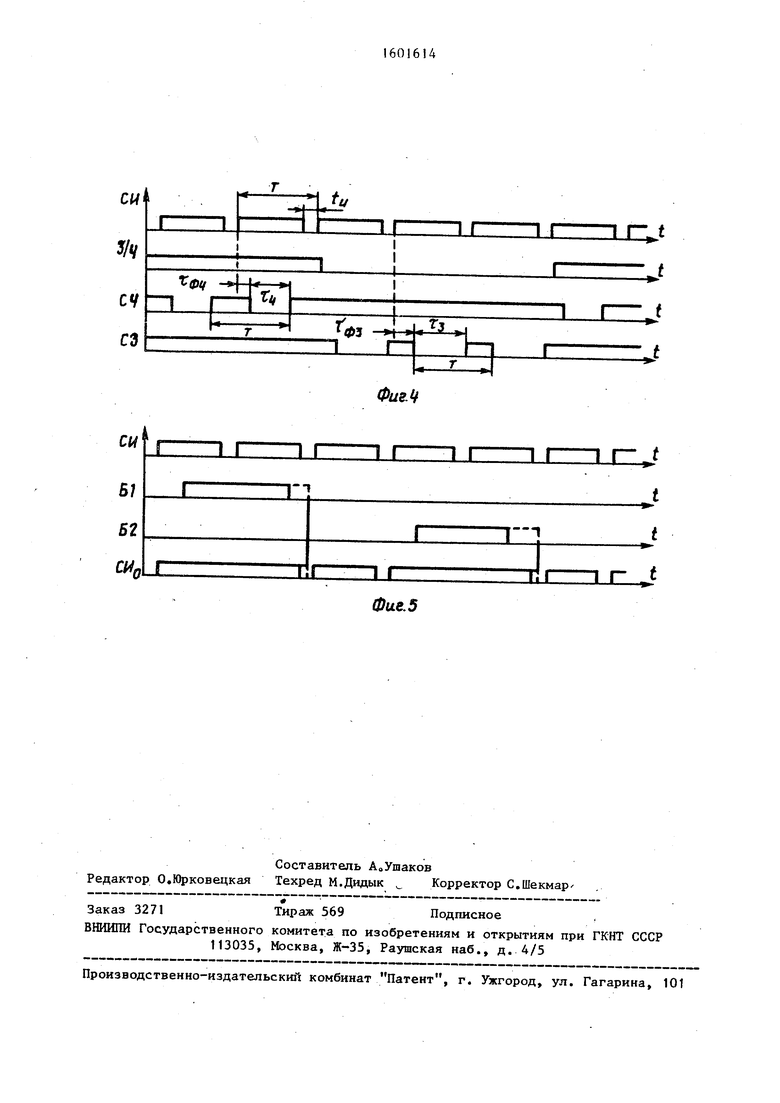

На фиго приведена структурная схема многопроцессорной системы; на фиг о 2 и 3 - функ1щональные схемы процессора и блока обмена соответственно; на фиг о4 - временные диаграммы сигналов, формируемых узлом синхронизации; на фиГоЗ - диаграммы, иллюстрирующие механизм затягивания положительной фазы синхроимпульсов

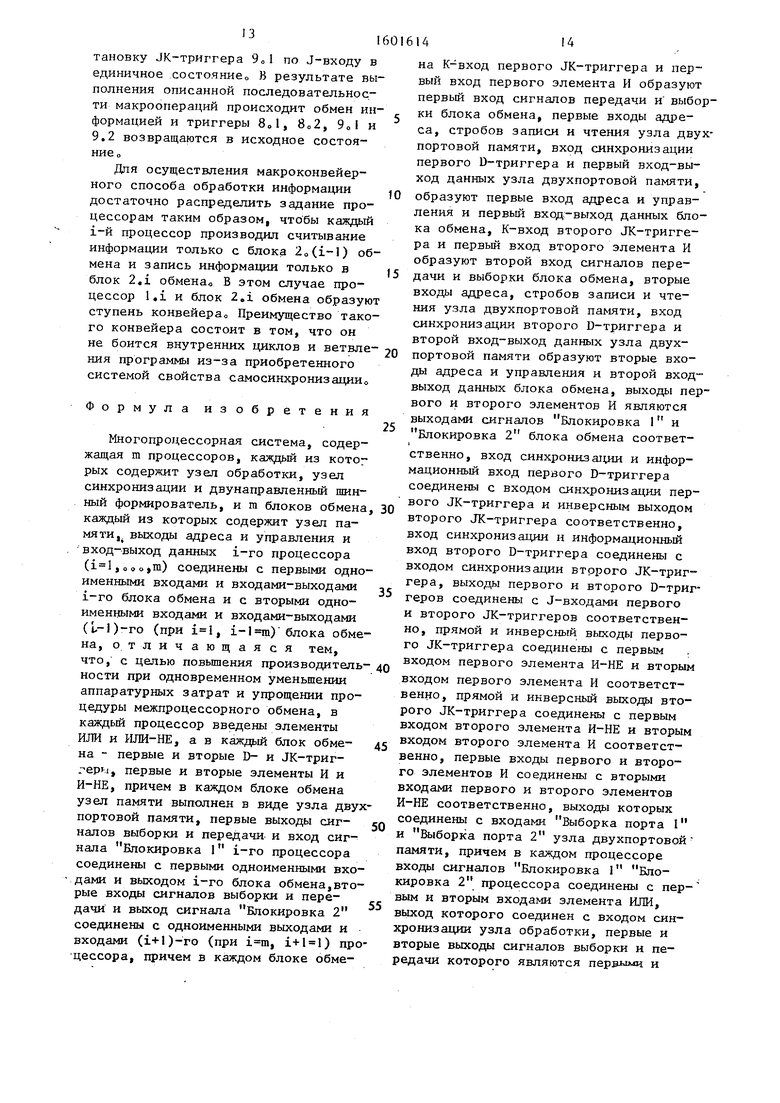

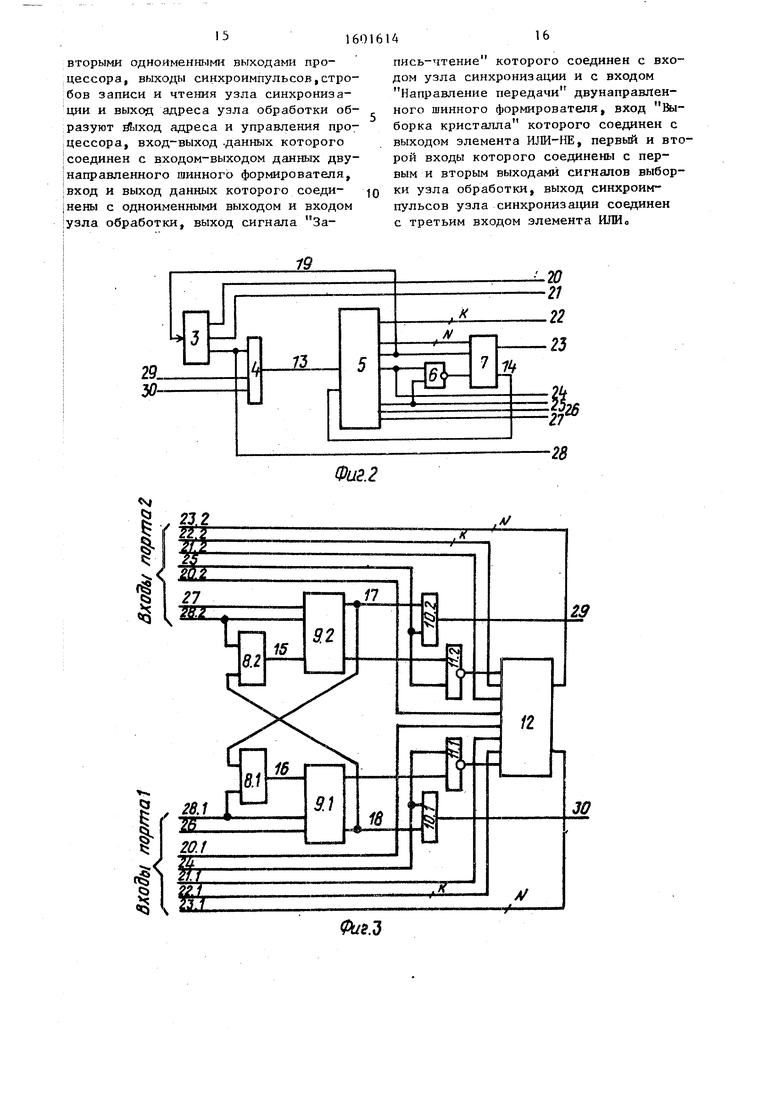

Система (фиГсО содержит процессоры 1о1-1ога и блоки 2И-2от обмена Каждый процессор 1 (фиго2) содержит узел 3 синхронизации, элемент ИЛИ 4, узел 5 обработки, элемент ИЛИ-НЕ 6 и двунаправленный шинный формирователь 7„ Каждый блок 2 обмена (фигоЗ) содержит D-триггеры 8.1 и 8„2, JK-триггеры 9о1 и 9о2, элементы И lOol и 10о2, элементы И-НЕ ПИ и 11.2 и узел 12 двухпортовой памяти емкостью 2 слов о Кроме того, на фиго 1-3 обозначены входы и выходы 13-30 соответствующих сигналов

Узел 5 обработки предназначен для обработки информации по заданной программе о Он содержит арифметико-логическое устройство, устройство управления, памяти программы и данных Часть адресного пространства в формате адресных команд отведено для обращения к блоку 2 обмена Устройство управления узла обработки помимо традиционных функций обеспечив ает программное формирование сигналов Передача 1 и Передача 2 Шинный формирователь 7 предназначен дпя согласования однонаправленных входа и выхода данных узла 5 обработки с внешней двунаправленной шиной данных В ка честве узла обработки 5 допустимо ис пользование широкого диапазона устройств: от универсального процессора до отдельных опертщонных узлов типа матричного умножителя, которые

обеспечивают формирование необходимого набора упрайляющих сигналов, адреса и операнда

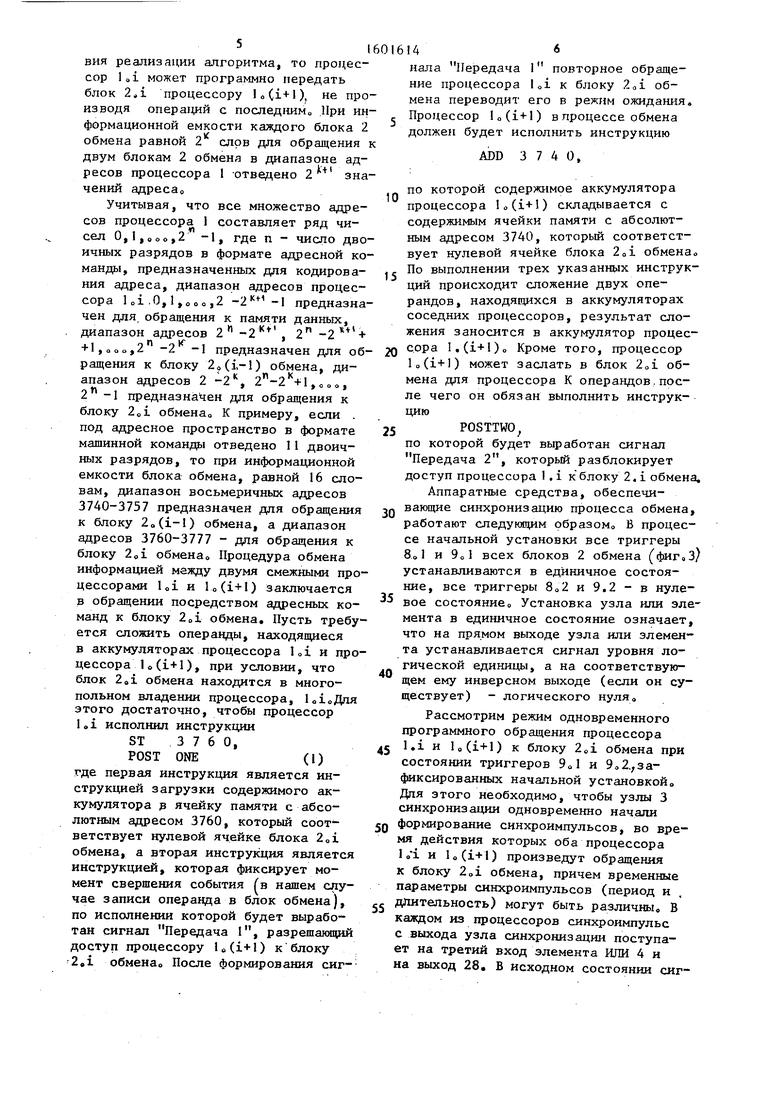

Узел 3 синхронизации формирует (фиго4) последовательность синхроимпульсов (СИ) с параметрами Т и ty и две последовательности стробируюпуг1х сигналов: стробов чтения (СЧ) с пара- 0 метрами 4 0)4 стробов записи

ч т /V л (СЗ) с параметрами с и о

срз

В зависимости от уровня сигнала Запись-- чтение (З/Ч) на выходах узла синхронизации формируются либо стробы 5 чтения (), либо стробы записи

() соответственно Активным уровнем стробирующих сигналов является уровень логического нуля В системе машинных команд каждого процессора 1 0 помимо набора арифметических, логических и команд управления, включакщих команды безусловного и условного переходов и обращения к подпрограмме, введены команды, формирующие сигналы 5 Передача Г и Передача 2, назначение которых заключается в синхронизации процесса обмена Каждый процессор i системы осуществляет связь с процессором l(i+l) через блок 30 обмена и с процессором 1. (i-1) через блок 2.() обмена. Обращенке процессора к блоку обмена осуществляется-посред- ством его адресных команд Два процессора 1 могут обратиться одновременно 35 к общему блоку 2 обмена без предварительного программного анализа его состояния, но при этом один из процессоров 1 перейдет в режим ожидания. Активный процессор 1, тот, кото- 40 Рьи получил доступ к блоку 2 обмена, закончив операции с ним, обязан программно передать блок 2 обмена ожида- кщему процессору 1 Эта передача осуществляется под управлением програм- 45 мно формируемых сигналов Передача 1 и Передача 2 Дпя реализации системой некоторого алгоритма в память программы каждого процессора I должна быть занесена программа, реализу- 50 кицая неопределенную часть алгоритма данного процессора 1 Программная реализация каждым процессором 1 соответствующей части общесистемного алгоритма отличается от общеизвестных 55 только процедурой обмена

В процессе начальной установки каждый блок 2о1 обмена передается процессору loii Если того требуют уелоВИЯ реализации алгоритма, то процессор loi может программно передать блок 2Д процессору l,Ci+l), не производя операгщй с последним При информационной емкости каждого блока 2 обмена равной 2 слов для обращения к двум блокам 2 обмена в диапазоне адресов процессора 1 отведено значений адреса

Учитывая, что все множество адре16

сов процессора 1 составляет ряд чисел 0,1,000,2 -1, где п - число двоичных разрядов в формате адресной команды, предназначенных для кодирования адреса, диапазон адресов процессора Ioi.0,1,000,2 предназначен для, обращения к памяти данных.

2 -2

Kt

2 -2

«+

диапазон адресов

+1,000,2 -2 -1 предназначен для обращения к блоку 2o(i-l) обмена, диапазон адресов 2-2, , о о о, 2 -1 предназначен для обращения к блоку 2oi обменао К примеру, если под адресное пространство в формате машинной команды отведено I1 двоичных разрядов, то при информационной емкости блока обмена, равной 16 словам, диапазон восьмеричных адресов 3740-3757 предназначен для обращения к блоку 2o(i-l) обмена, а диапазон адресов 3760-3777 - дпя обращения к блоку 2oi обменао Процедура обмена информацией между двумя смежными процессорами loi и lo(i+l) заключается в обращении посредством адресных команд к блоку 2„1 обмена. Пусть требуется сложить операнды, находящиеся в аккумуляторах процессора Ki и про- цессораЧо(1+1), при условии, что блок 2oi обмена находится в многопольном владении процессора, ЫоДпя этого достаточно, чтобы процессор 1.i исполнил инструкции ST 3760, POST ONE(I)

где первая инструкция является инструкцией загрузки содержимого аккумулятора э ячейку памяти с абсо- ютшлм адресом 3760, который соот етствует нулевой ячейке блока 2oi бмена, а вторая инструкция является нструкцией, которая фиксирует моент свершения события (в нашем слуае записи операнда в блок обмена), о исполнении которой будет вырабоан сигнал Передача 1, разрешаютщй оступ процессору le(i+l) к блоку ,1 обменао После формирования сиг16016 14

нала Передача 1 повторное обращение процессора I к блоку 2,i обмена переводит его в реким ожидания. Процессор I,(i-(-l) в процессе обмена должен будет исполнить инструкцию

ADD 3740,

10

15

20

25

30

по которой содержимое аккумулятора процессора lo(i+l) складывается с содержимым ячейки памяти с абсолютным адресом 3740, который соответствует нулевой ячейке блока 2oi обменао По выполнении трех указанных инструкций происходит сложение двух операндов, находящихся в аккумуляторах соседних процессоров, результат сложения заносится в аккумулятор процессора l,(i+l)o Кроме того, процессор lo(i+l) может заслать в блок 2,i обмена дня процессора К операндов,после чего он обязан выполнить инструкцию

POSTTWO

по которой будет выработан сигнал Передача 2, который разблокирует доступ процессора 1.1 к блоку 2.1 обмена.

Аппаратные средства, обеспечивающие синхронизацию процесса обмена, работают следующим образомо В процессе начальной установки все триггеры 8о1 и 9о1 всех блоков 2 обмена (фигоЗ) устанавливаются в единичное состояние, все триггеры 8о2 и 9,2 - в нуле- вое состояние Установка узла шш элемента в единичное состояние означает, что на прямом выходе узла или элемента устанавливается сигнал уровня логической единицы, а на соответствующем ему инверсном выходе (если он существует) - логического нуляо

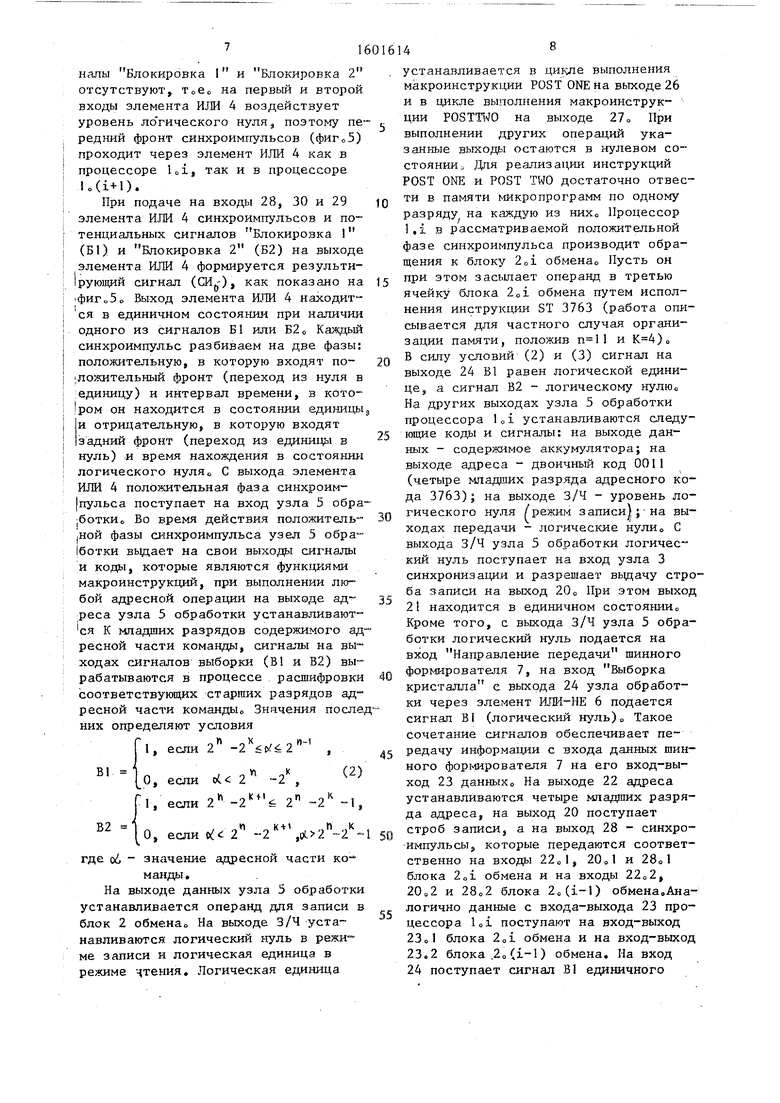

Рассмотрим режим одновременного программного обращения процессора l.i и Io(i+l) к блоку 2oi обмена при состоянии триггеров 9о1 и 9о2.,зафиксированных начальной установкойо Для этого необходимо, чтобы узлы 3 синхронизации одновременно начали формирование синхроимпульсов, во время действия которых оба процессора 1 о г и 1 о (i+l) произведут обращения к блоку 2oi обмена, причем временные параметры синхроимпульсов (период и 5 длительность) могут быть различны, В каждом из процессоров синхроимпульс с выхода узла синхронизации поступает на третий вход элемента ИЛИ 4 и на выход 28, В исходном состоянии сиг5

0

налы Блокировка 1 и Блокировка 2 отсутствуют, т о во на первый и второй входы элемента HJM 4 воздействует уровень логического нуля, поэтому передний фронт синхроимггульсов (фиго5) проходит через элемент ИЛИ 4 как в процессоре Ki, так и в процессоре lc(i+l).

При подаче на входы 28, 30 и 29 элемента ИЛИ 4 синхроимпульсов и потенциальных сигналов Блокировка (Б1) и Блокировка 2 (Б2) на выходе элемента ИЛИ 4 формируется результирующий сигнал (СИ.г) как показано на фиг„5о Выход элемента ШШ 4 находится в единичном состоянии при наличии одного из сигналов Б1 или Каждый синхроимпульс разбиваем на две фазы: положительную, в которую входят положительный фронт (переход из нуля в единицу) и интервал времени, в котором он находится в состоянии единицы и отрицательную, в которую входят задний фронт (переход из единицы в нуль) и время нахождения в состоянии логического нуляо С выхода элемента ИЛИ 4 положительная фаза синхроим- |пульса поступает на вход узла 5 обра- :боткИс Во время действия положитель- (Ной фазы синхроимпульса узел 5 обра- |ботки выдает на свои выхода сигналы и коды, которые являются функциями макроинструкций, при выполнении любой адресной операции на выходе адреса узла 5 обработки устанавливают- ся К младших разрядов содержимого адресной части команды, сигналы на выходах сигналов выборки (В1 и В2) вырабатываются в процессе расшифровки соответствующих старших разрядов адресной части командыо Значения послед них определяют условия

1, если 2

0,если о(. 2 -2

1,если 2 2

(2) S

В2

к+

о, если 2 -2 , -2

где (х. - значение адресной части ко-

манды

На выходе данных узла 5 обработки устанавливается операнд для записи в блок 2 обмена На выходе З/Ч устанавливаются логический нуль в режиме записи и логическая единица в режиме чтения. Логическая единица

5

0

0

5

5

устанавливается в выполнения макроинструкции POST ONE на выходе 26 и в цикле выполнения макроинструкции РОЗТтаО на выходе 27 При выполнении других операций указанные выходы остаются в нулевом состоянии. Для реализации инструкций POST ONE и POST TWO достаточно отвести в памяти микропрограмм по одному разряду на к;шдую из нихо Процессор 1,1 в рассматриваемой положительной фазе синхроимпульса производит обращения к блоку 2oi обменао Пусть он при этом засылает операнд в третью ячейку блока 2oi обмена путем исполнения инструкции ST 3763 (работа описывается для частного случая орггии- зации памяти, положив и )о В силу условий (2) и (3) сигнал на выходе 24 В1 равен логической единице, а сигнал В2 - логическому нулюо На других выходах узла 5 обработки процессора Ui устанавливаются следующие коды и сигналы: на выходе данных - содержимое аккумулятора; на выходе адреса - двоичный код ООП (четыре МЛЯДИ1ИХ разряда адресного кода 3763); на выходе З/Ч - уровень логического нуля /режим записи);;-на выходах передачи - логические нулио С выхода З/Ч узла 5 обработки логичес кий нуль поступает на вход узла 3 синхронизации и разрешает выдачу строба записи на выход 20о При этом выход 2 находится в единичном состоянии Кроме того, с выхода З/Ч узла 5 обработки логический нуль подается на вход Направление передачи шинного формирователя 7, на вход Выборка кристалла с выхода 24 узла обработки через элемент ИЛИ-НЕ 6 подается сигнал В1 (логический нуль) Такое сочетание сигналов обеспечивает передачу информации с входа данных шинного фор1 1ирователя 7 на его вход-выход 23 данныхо На выходе 22 адреса устанавливаются четыре младших разряда адреса, на выход 20 поступает строб записи, а на выход 28 - синхро- импульсы, которые передаются соответственно на входы 22о1, 20о 1 и 28о1 блока 2oi обмена и на входы 22,,2, 20о 2 и 28о2 блока 2,(i-l) обмена.Ана- логично данные с входа-выхода 23 процессора loi поступают на вход-выход

23о 1 блока 2(,i обмена и на вход-выход 23,2 блока ,2о(i-1) обмена. На вход

24поступает сигнал В1 единичного

уровня, а на вход 26 - сигнал Передача порта I (III) нулевого неактивного уровня, которые поступают в бло 2„1 обмена„ В блоке 2 операнд по входу-выходу 23 оt поступает на первы вход-выход узла 12 двухпортовой памяти, которьй в этом случае выполняет функцию информационного входа, строб записи по входу 20 поступает на вход СЗ узла 12„ Синхроимпульс по входу 28,1 поступает на входы синхронизации D-триггера 8о1 и JK-триггера 9о1 при этом триггеры продолжают оставаться в единичном состоянии Единиц- ный сигнал с прямого выхода JK-триггера 9о1 и сигнал В1 по входу 24 единичного уровня, поступая на соответствующие входы элемента И-НЕ 11„ 1 формируют на его выходе сигнал В1 Q1 Л В1, который,-поступая на вход В1 узла 12 двухпортовой памяти, обеспечивает запись операнда с входа-выхода 23,, 1 в третью ячейку узла 12,На выходе элемента И lOol формируется сигнал Блокировка 1 (Б I), причем Б1 Q Л в нашем случае равен нулю, так как Q1 О, где Q1 - инверсный выход JK-триггера 9о1о Сигнал Б1 с блока 2,1 обмена по входу 30 поступает в процессор loi, в котором он воздействует на первый вход элемента ИЛИ 4, Нулевой (неактивный) уровень поступившего сигнала Б1 не влияет на прохождение синхроимпульсов через элемент ИЛИ 4, поэтому с приходом отрицательной фазы рассматриваемого синхроимпульса завершается выполнение микрооперации, ив случае, если она была заключительной в последовательности микроопераций, реализующих макрооперацию записи, следующий синхроимпульс увеличивает содержимое счетчика комаид на единицу и процессор 1 начинает выполнение следующей макрооперациио

Обратимся теперь к процессору lo(i+l)o. Пусть он выполняет в цикле обращение к блоку 2,i обмена инструкцию ADD 3743,, При этом на выходах его узла 5 сформированы следующие сигналы: на втором выходе сигнала выборки - сигнал В2 единичного уровня по условию (3); на первом ил- ходе сигнала выборки - сигнал В1 нулевого уровня по условию (2); на выходе адреса - двоичный код 0011 (четыре младших разряда восьмеричного

10

20

j

кода 3743); на выходе З/Ч - сигнал З/Ч единичного уровня (режим чтения); на выходах сигналон передачи -.сигналы П и 112 уровня логического нуля

С выхода З/Ч узла 5 обработки единица поступает на вход узла 3 синхронизации и разрешает выдачу строба чтения на его выход 21 и на вход Направление передачи двунаправленного шинного формирователя 7, на вход Выборка кристалла которого поступает с выхода 25 узла 5 обработки инвертированный сигнал В2 через элемент ШШ- НЕ 6о Сочетание указанных сигналов обеспечивает передачу операнда с вхо- да-вь1хода данных шинного формирователя 7 на его выход данныхо Таким образом, операнд с входа-выхода 23 поступает на вход данных узла 5 обработки Адрес по выходу 22, строб чтения по выходу 21 и синхроимпульс по выходу 28 поступают соответственно по входам 22, 23, 21с,2 и 28о2 блока 25 2oi обмена и на входы 22о1, 21,1 и 28,1 блока 2,(i-)-I) обмена Сигнал В2 уровня логической единицы и сигнал П2 уровня логического нуля поступают соответственно по входам 25 и 27 в блок 2,1 обмена, в котором адрес по входу 22о2, а строб чтения - г- по входу 21 о 2 поступают соответственно на входы узла 12 двухпортовой памяти о Синхроимпульс по входу 28о 2 поступает на входы синхроимпульсов D- триггера 8„2 и JK-триггера 9о2, при этом триггеры 8.2 и 9,2 продолжают оставаться в нулевом состоянии На выходе элемента И 10,2 сформирован сигнал Б2 Q2 Л В2, в нашем случае равен 1, так как , , где Q2 инверсный выход JK-триггера 9о2, Сигнал Б2 по входу 29 поступает на соответствующий вход элемента ИЛИ 5 в процессоре К(1+1), блокируя прохождение отрицательной фазы синхроимпульса, что равносильно затяжке во времени отрицательной .фазы синхроимпульса. При этом узел 5 обработки 0 переходит в режим ожидания до момента, пока JK-триггер 9о2 не изменит св оего состояния,, Нулевой уровень с прямого выхода JK-триггера 9о2 и сигнал В2 единичного уровня на входе 25, J поступая на входы элемен а И-НЕ И „2, формируют сигнал В2 Q2 Л В2, единичный уровень которого поступая на вход В2 узла 12 двухпортовой памяти блока 2о1, не разрешает выборку ее второго

30

35

40

11 1

порта, при этом вторые входы-выходы Данных продолжают оставаться в третьем состояниИс Таким образом осуществляется задержка чтения операнда, что Hie отражается на правильности функцио фрования процессора . 1 о (i+1) , ариф- фтико-логическое устройство которого я вляясь комбинационной схемой, произ- Е|ОДИТ обработку операнда в соответст- Е|ИИ с кодом операции после считывания последнего Таким образом, в резуль- TJaTB одновременного обращения двух 1|роцессоров loi и 1о() к блоку 2oi обмена происходит запись содержимого Аккумулятора процесора loi в третью 4чейку узла 12 двухпортовой памяти,а процессор lc(i+l) переходит в режим фжидания, в котором он находится до tex пор, пока процессор loi не испол- фит инструкцию POST ONE. В цикле вы-/ волнения макроинструкции POST ONE в зле 5 обработки формируется сигнал

|11 , которьш по входу 26 поступает а К-вход JK-триггера 9о1 и вызывает го установку в нулевое состояниео рк этом на выходе элемента И lOol формируется сигнал Б1 при условии, если процессор loi вновь обратится К блоку 2Д обмена, которьм по вы- ходу 30 поступает на третий вход элемента ИЖ 4 процессора и переводит его таким образом в режим ожидания Единица с инверсного выхода JK-триг- irepa 9.01 поступает на D-вход D-триг- irepa 802, который по приходу перед- 1него фронта синхроимпульса по входу j28c2 с процессора lo(i+l) переходит IB единичное состояние и вызывает уст новку JK-триггера 9о2 по J-входу в единичное состояниео Назначение D-тр гера 8,2 закпючается в согласовании процесса обмена с частотой следования синхроимпульсов процессора lo(i+l) Как следует из фигоЗ, по- падание заднего фронта сигнала Б1 ил Б2 в отрицательную фазу исходной последовательности синхроимпульсов вызывает уменьшение длительности отрицательной фазы результирующей после- довательности СИд(показано пунктиром) по сравнению с исходной, что ндопустимо о Согласующие D-триггеры 8,2 и 8«1 осуществляют необходимую задержку в снятии сигналов Б2 и Б1 соответственно и гарантируют формирование задних фронтов этих сигналов в положительной фазе соответствующих синхроимпульсов о

14

12

5 0 5

Вновь обратимся к рассмотрению функцио1шрования процессора 1 о (i 1 ), которьш при выполне ши операции ADD 3743 перешел в режим ож одания,. После срабатывания JK-триггера 9о2 сигнал Б2 снимается, т.ео на выходе элемента И Юс2 устанавливается нулевое состояние, которое передается по выходу 29 на вход элемента ИЛИ 4 процессора lo(i+l), на выходе элемента И-НЕ 11о2 формируется сигнал В2 Q2 Д В2, нулевой уровень которого, поступая на вход узла 12 двухпортовой памяти, разрешает выборку ее второго порта При этом стробы чтения по входу ,21 о 2 поступают на вход узла 12 двухпортовой памяти все время, пока процессор lo(i+l) находится в режиме ожидания, код адреса (0011) на входе адреса также не снимается, так как отрицательная фаза си1&ро- импульса еще не проходила на узел 5 обработки Поэтому после срабатывания JK-триггера 9о2, которое происходит только в положительной фазе синхроимпульсов, очередной строб чтения производит считывание информации из третьей ячейки узла 12 двухпортовой памяти и на выходе данных устаналивается ее содержимое, которое по входу-выходу 23 поступает в процессор lo(i+Oo Поступивший операнд с входа-выхода шинного формирователя 7 передается на вход данных узла Ь обработки В последнем происходит сложение поступившего операнда с содержимым аккумулятора Отрицательная фаза очередного синхроимпульса проходит через элемент ИЛИ 4 и, поступая на вход СИ узла 5 обработки, завершает выполнение рассматриваемой операциио Дальнейшая работа процессора l.(i+l) протекает в соответствии с программой Блок обмена находится в монопольном владении процессора lo(i+l), пока последний не исполнит инструкцию POST TWO, по которой в его узле обработки процессора l.(i+l) будет выработан.сигнал П2. Этот сигнал по входу 27 поступае в блок 2Д обмена на К-вход JK-триггера и устанавливает его в нуль. Единица с инверсного выхода JK-триггера 9о2 поступает на D-вход D-триг- гера 8.1, который по приходу синхроимпульса с процессора 1,1 переходит, в единичное состояние,и вызывает ус10

1601614

ра 9„1 по J-входу в ие,, В результате вый носледовательнос- происходит обмен инеры 8о1, 8о2, 9о1 и в исходное состоя

ния макроконвейер- ботки информации делить задание проразом, чтобы каждый зводил считывание с блока 2o(i-i) обрмации только в этом случае про2.1 обмена образуют Преимущество такоит в том, что он их циклов и ветвле- JQ а приобретенного самосинхронизациис

15

на вы пе ки са по пе хо об ле ка ра обр да вхо ния син вто пор ды вых вог вых Бл ств мац сое вог вто вхо вход вход гер геро и вт но, го J вход вход венн рого вход вход венн го эл вход И-НЕ соеди и й памят входы киров вым и выход хрони вторы редач

Формула изобретения

25

Многопроцессорная система, содержащая m процессоров, каждый из котог рых содержит узел обработки, узел синхронизации и двунаправленный шинный формирователь, и га блоков обмена, 30 каждый из которых содержит узел памяти,, выходы адреса и управления и вход-выход данных 1-го процессора (,o,m) соединены с первыми одноименными входами и входами-выходами 1-го блока обмена и с вторыми одноименными входами и входами-выходами (L-l)-ro (при , ) блока обмена, отличающаяся тем, что, с целью повышения производитель- 40 ности при одновременном уменьшении аппаратурных затрат и упрощении процедуры межпроцессорного обмена, в каждый процессор введены элементы ИЛИ и РШИ-НЕ, а в каждый блок обмена - первые и вторые D- и JK-триг- герм, первые и вторые элементы И и И-НЕ, причем в каждом блоке обмена узел памяти выполнен в виде узла двухпортовой памяти, первые выходы сиг- jO налов выборки и передачи и вход сигнала Блокировка Г 1-го процессора соединены с первыми одноименными вхо- дами и выходом 1-го блока обмена,вторые входы сигналов выборки и передачи и выход сигнала Блокировка 2 соединены с одноименными выходами и входами (1+1)-го (при , ) процессора, причем в каждом блоке обме45

55

14

10

в ы

т- JQ

15

25

30 40jO45

5

на К-вход первого JK-триггера и первый вход первого элемента И образуют первый вход сигналов передачи и выборки блока обмена, первые входы адреса, стробов записи и чтения узла двухпортовой памяти, вход синхронизации первого D-триггера и первый вход-выход данных узла двухпортовой памяти, образуют первые вход адреса и управления и первый вход-выход данных блока обмена, К-вход второго JK-триггера и первый вход второго элемента И образуют второй вход сигналов передачи и выборки блока обмена, вторые входы адреса, стробов записи и чтения узла двухпортовой памяти, вход синхронизации второго D-триггера и второй вход-выход данных узла двухпортовой памяти образуют вторые входы адреса и управления и второй вход- выход данных блока обмена, выходы первого и второго элементов И являются выходами сигналов Блокировка 1 и Блокировка 2 блока обмена соответственно, вход синхрониз шщи и информационный вход первого D-триггера соединены с входом синхронизации первого JK-триггера и инверсным выходом второго JK-триггера соответственно, вход синхронизации и информационный вход второго D-триггера соединены с входом синхронизации второго JK-триггера, выходы первого и второго D-триг- геров соединены с J-входами первого и второго JK-триггеров соответственно, прямой и инверс1шй выходы первого JK-триггера соединены с первым входом первого элемента И-НЕ и вторым входом первого элемента И соответственно, прямой и инверсный выходы второго JK-триггера соединены с первым входом второго элемента И-НЕ и вторым входом второго элемента И соответственно, первые входы первого и второго элементов И соединены с вторыми входами первого и второго элементов И-НЕ соответственно, выходы которых соединены с входами Выборка порта I и й,1борка порта 2 узла двухпортовой- памяти, причем в каждом процессоре входы сигналов Блокировка Г Блокировка 2 процессора соединены с пер- вым и вторым входами элемента ИЛИ, выход которого соединен с входом синхронизации узла обработки, первые и вторые выходы сигналов выборки и передачи которого являются первыми и

вторыми одноименными выходами процессора, выходы синхроимпульсов,стробов записи и чтения узла синхронизации и выход адреса узла обработки образуют адреса и управления процессора, вход-выход .данных которого соединен с входом-выходом данных двунаправленного шинного формирователя, вход и выход данных которого соединены с одноименными выходом и входом узла обработки, выход сигнала За

пись-чтение которого соединен с входом узла синхронизации и с входом Направление передачи двунаправленного шинного формирователя, вход ftj- борка кристалла которого соединен с выходом элемента ШШ-НЕ, первый и второй входы которого соединены с первым и вторым выходами сигналов выборки узла обработки, выход синхроимпульсов узла синхронизации соединен с третьим входом элемента ИЛИо

| название | год | авторы | номер документа |

|---|---|---|---|

| Ортогональная многопроцессорная система | 1990 |

|

SU1839261A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Матричная вычислительная система | 1989 |

|

SU1608700A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОСТАДИЙНОЙ МНОГОПОТОЧНОЙ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ И СПОСОБ ОБРАБОТКИ С ИСПОЛЬЗОВАНИЕМ ДАННОГО МОДУЛЯ | 2018 |

|

RU2681365C1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Вычислительный модуль и способ обработки с использованием такого модуля | 2018 |

|

RU2689433C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Процессор | 1989 |

|

SU1725224A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

Изобретение относится к вычислительной технике и предназначено для реализации обработки информации в конвейерном режиме в реальном времени и в режиме множественных потоков команд и данных, при этом межпроцессорный обмен в системе осуществляется асинхронно. Цель изобретения - повышение производительности при одновременном уменьшении аппаратурных затрат и упрощении процедуры межпроцессорного обмена. Обмен между процессорами 1 производится через блоки 2 обмена, содержащие узел двухпортовой памяти. Причем на время доступа одного процессора 1 к узлу двухпортовой памяти доступ другого процессора 1 блокируется. Используемые средства синхронизации доступа к узлу двухпортовой памяти упрощают реализацию системы. 5 ил.

Фиё.г

Фи.Ъ

л/

cw

CV

ZL

СФЦ

Гц

C3

/Ф,-4н

67 62 Сй л

н

Фиг.1

1

JZ-J

Фие.5

| Валях Ео Последовательно-параллельные вычисления: Перев,, с англ - Мо: Мир, 1985, СоП7-124с Авторское свидетельство СССР № 1259277, кл„ G 06 F 15/16, 1984с |

Авторы

Даты

1990-10-23—Публикация

1988-01-15—Подача