Изобретение относится к вычислительной технике, в частности к процессорам для обработки цифровой информации, v может быть использовано при построении специализированных многопроцессорных систем большого быстродействия для моделирования динамических объектов и систем управления, а также измерительных систем, работающих в режиме реального времени.

Наибольший экономический эффект может быть достигнут при использовании процессора в составе алигативной вычислительной системы при решении задач динамики объекта в режиме реального времени.

Цель изобретения - повышение быстродействия за счет исключения буферных пересылок операндов.

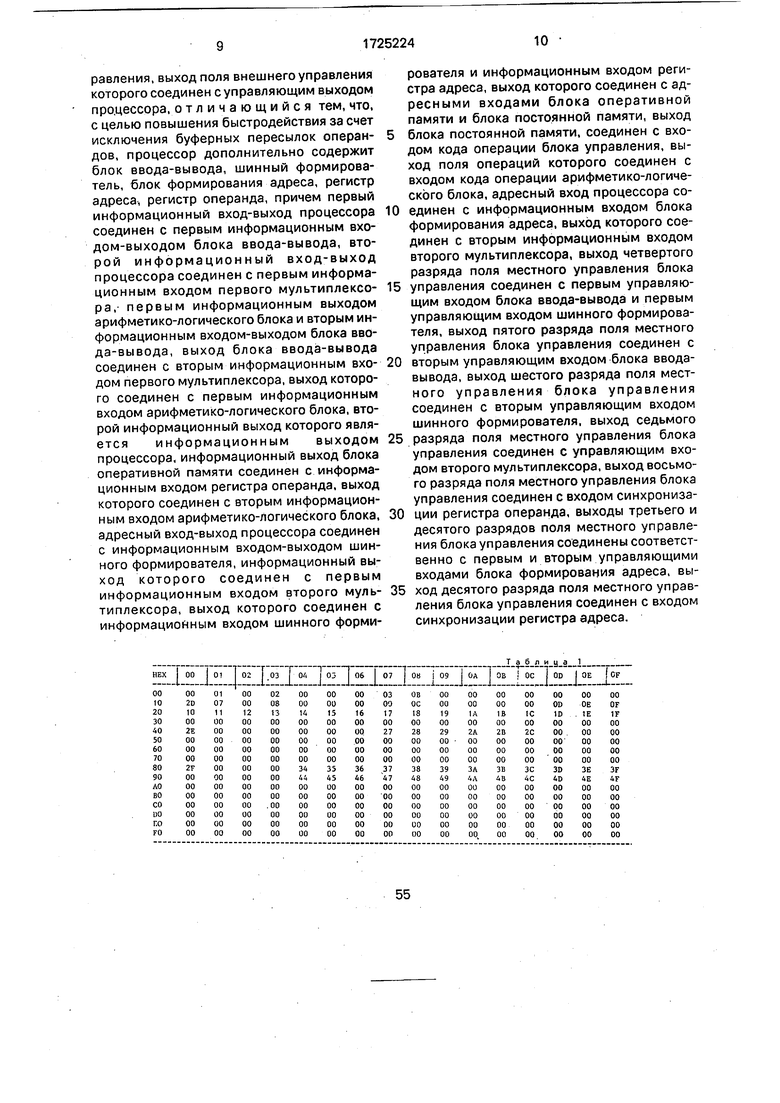

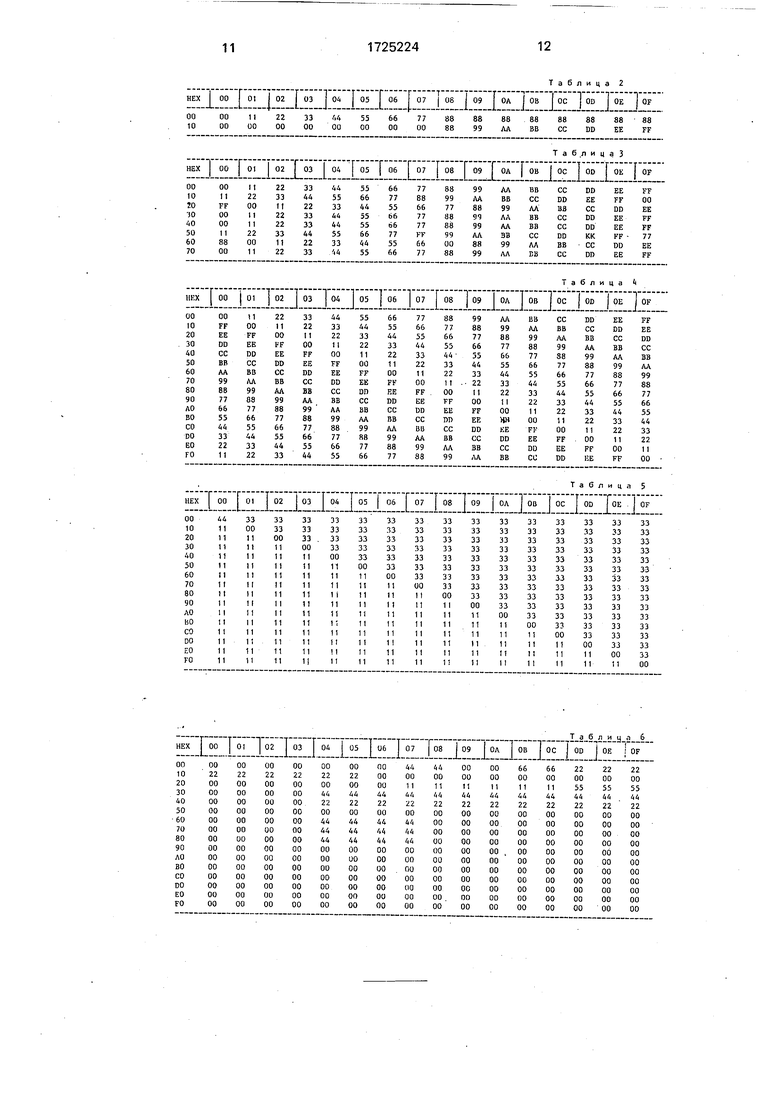

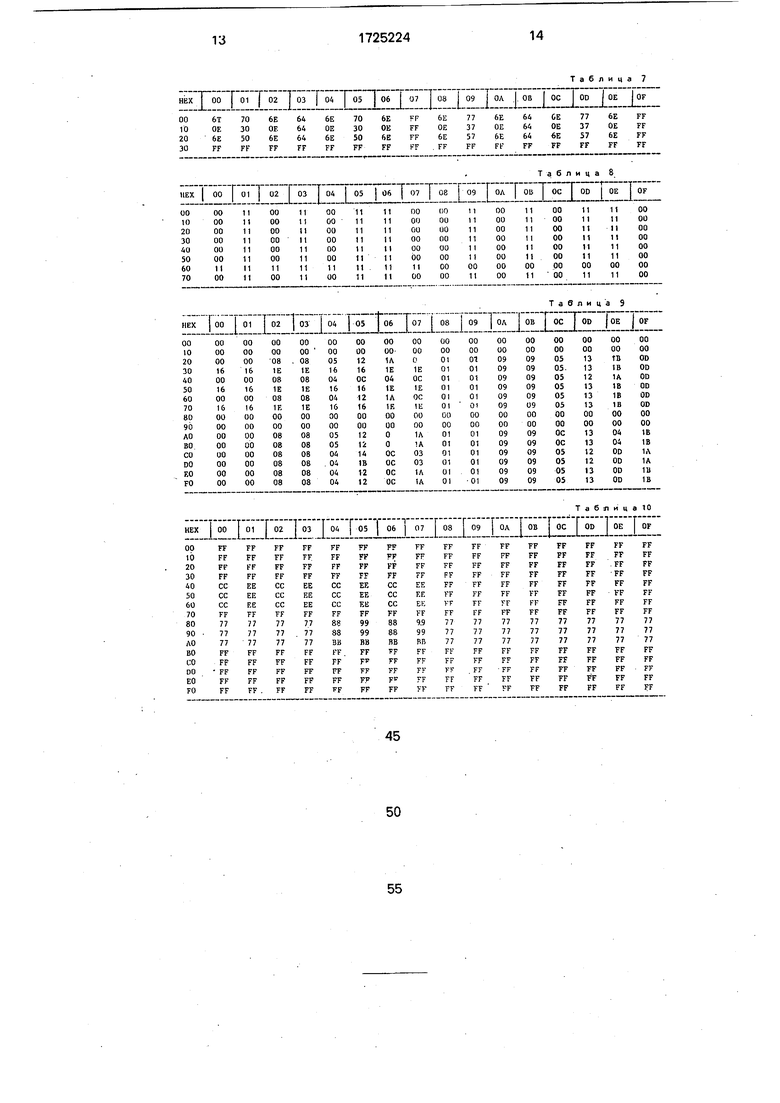

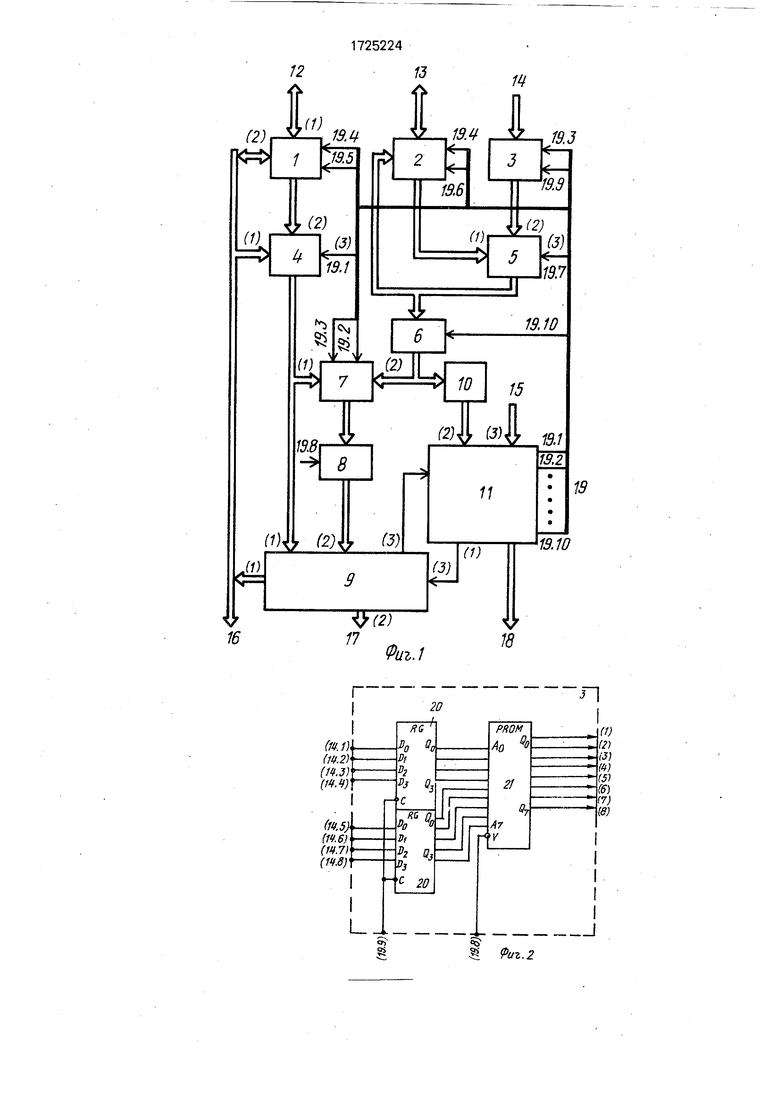

Нафиг.1 изображена структурная схема процессора; на фиг.2 - схема блока формирования адреса; на фиг.З - схема реализации арифметико-логического блока; на фиг.4 - схема реализации блока управлеVI

N)

сл

IN) Ю 4

ния; на фиг.5 - временная диаграмма синхроимпульсов; на фиг.6 - схема реализации блока ввода-вывода.

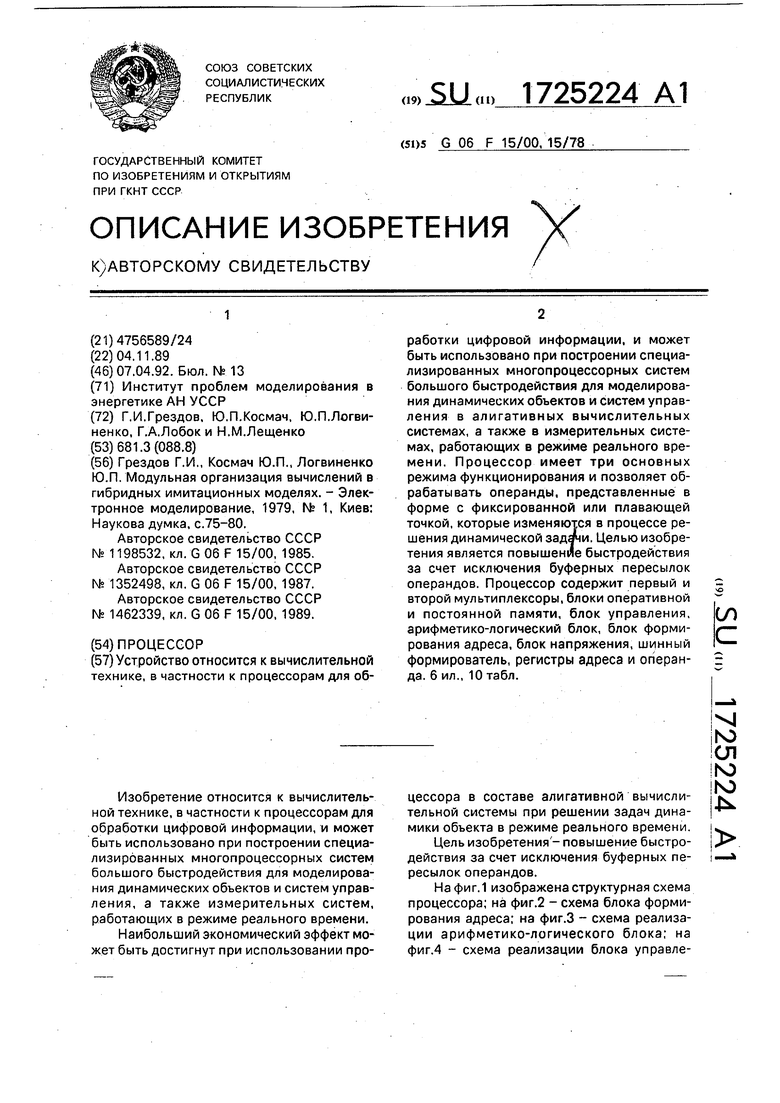

Процессор (фиг. 1) содержит блок 1 ввода-вывода, шинный формирователь 2, блок 3 формирования адреса, первый 4 и второй 5 мультиплексоры, регистр 6 адреса, блок 7 оперативной памяти, регистр 8 операнда, арифметико-логический блок (АЛ Б) 9, блок 10 постоянной памяти, блок 11 управления, первый информационный вход-выход 12, адресный вход-выход 13, адресный вход 14, вход 15 режима и синхронизации, второй информационный вход-выход 16, информационный выход 17, выход 18 поля внешнего управления, выход 19 поля местного управления. Цифрами в скобках (фиг.1) обозначены порядковые номера входов и выходов блоков.

Блок 3 формирования адреса (фиг.2) предназначен для обеспечения приема адреса переноса из аналоговой части алига- тивной вычислительной системы и преобразования в адрес обрабатываемого операнда и содержит регистры 20, память 21, пример программирования которой приведен в табл.1. Нагрузочные резисторы на схеме и далее не показаны.

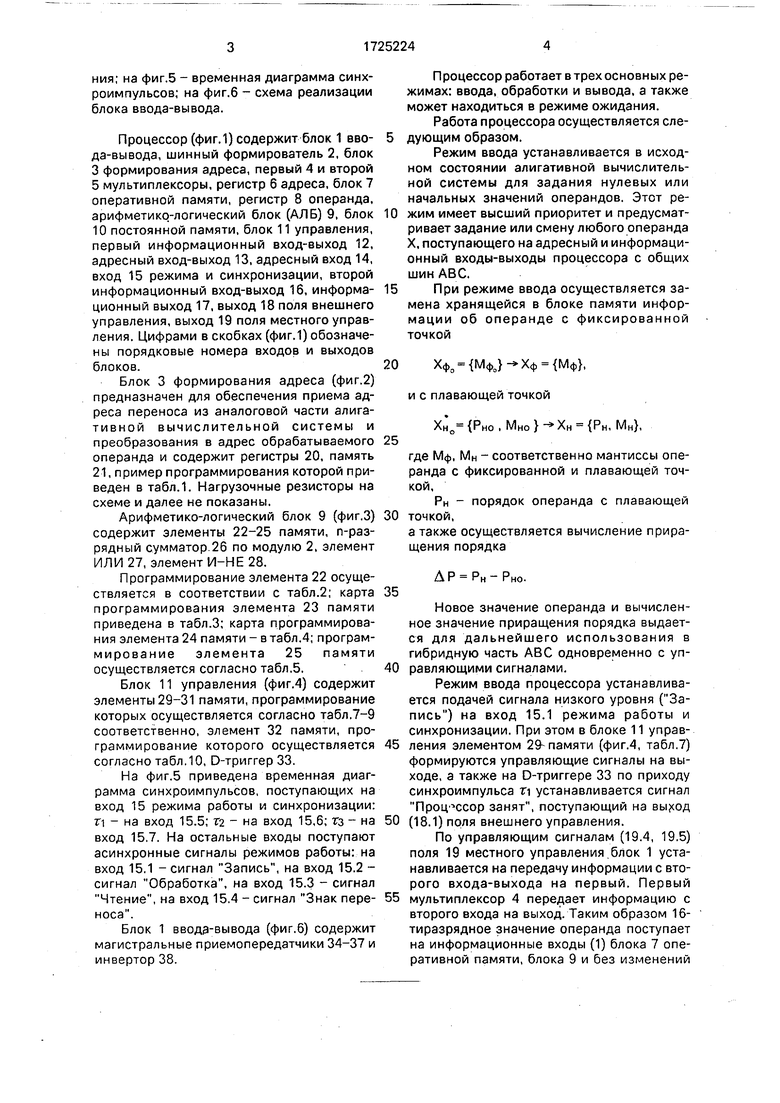

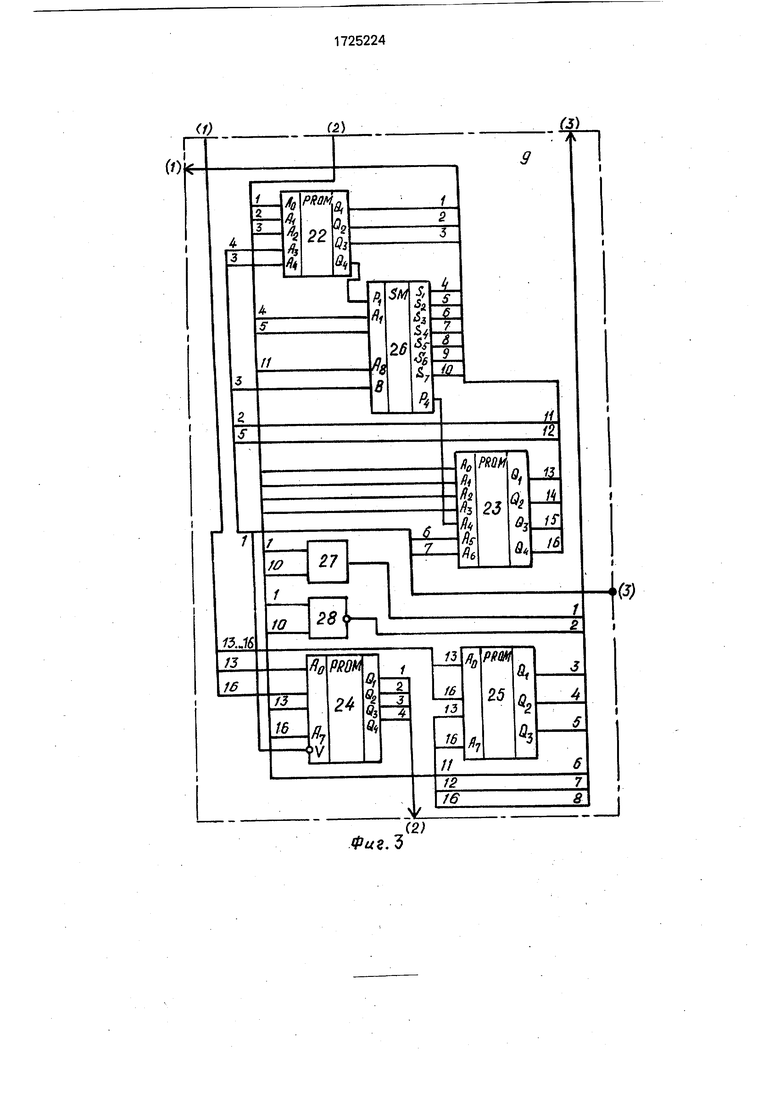

Арифметико-логический блок 9 (фиг.З) содержит элементы 22-25 памяти, п-раз- рядный сумматор.26 по модулю 2, элемент ИЛИ 27, элемент И-НЕ 28.

Программирование элемента 22 осуществляется в соответствии с табл.2; карта программирования элемента 23 памяти приведена в табл.3; карта программирования элемента 24 памяти - в табл.4; програм- мирование элемента 25 памяти осуществляется согласно табл.5.

Блок 11 управления (фиг.4) содержит элементы 29-31 памяти, программирование которых осуществляется согласно табл.7-9 соответственно, элемент 32 памяти, программирование которого осуществляется согласно табл.10, D-триггер 33.

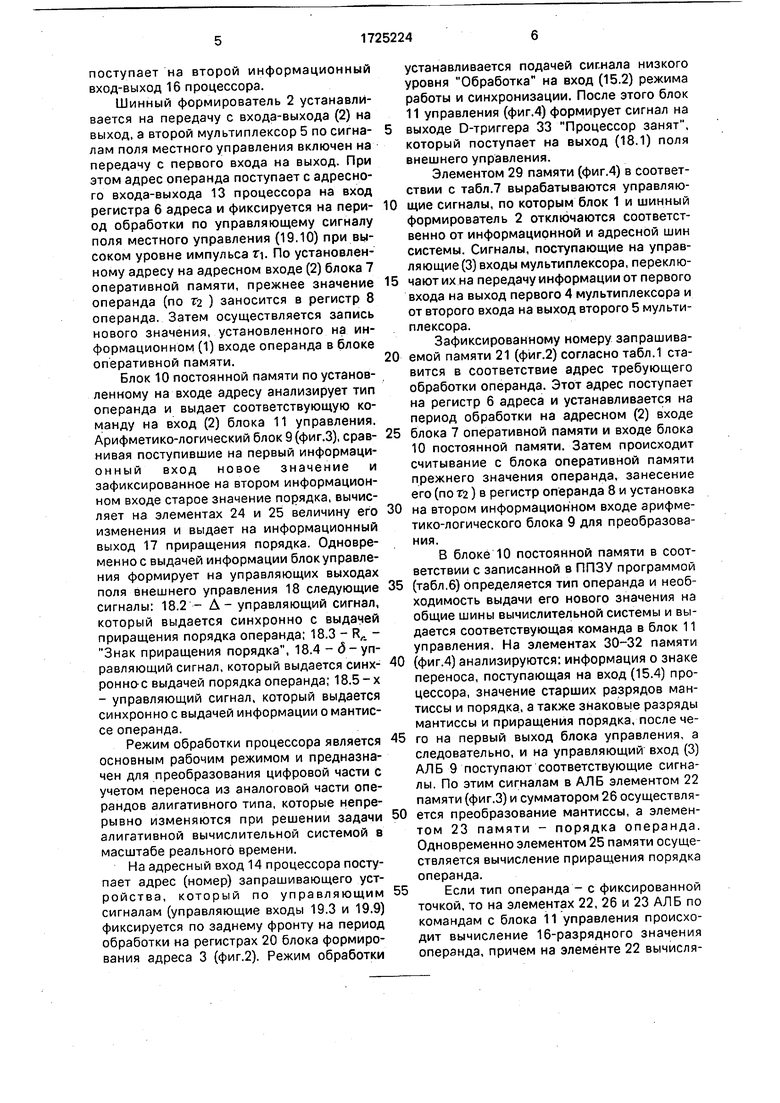

На фиг.5 приведена временная диаграмма синхроимпульсов, поступающих на вход 15 режима работы и синхронизации: П - на вход 15.5; та - на вход 15,6; тз - на вход 15.7. На остальные входы поступают асинхронные сигналы режимов работы: на вход 15.1 - сигнал Запись, на вход 15.2 - сигнал Обработка, на вход 15.3 - сигнал Чтение, на вход 15.4 - сигнал Знак переноса.

Блок 1 ввода-вывода (фиг.6) содержит магистральные приемопередатчики 34-37 и инвертор 38.

Процессор работает в трех основных режимах: ввода, обработки и вывода, а также может находиться в режиме ожидания.

Работа процессора осуществляется сле- дующим образом.

Режим ввода устанавливается в исходном состоянии алигативной вычислительной системы для задания нулевых или начальных значений операндов. Этот ре- жим имеет высший приоритет и предусматривает задание или смену любого операнда X, поступающего на адресный и информационный входы-выходы процессора с общих шин ABC.

При режиме ввода осуществляется замена хранящейся в блоке памяти информации об операнде с фиксированной точкой

Хф0 {Мфо}- Хф {Мф}, и с плавающей точкой

25

Хн0 {Рно , Мно } Хн {Рн, Мн},

где Мф, Мн - соответственно мантиссы операнда с фиксированной и плавающей точкой,

Рн - порядок операнда с плавающей точкой,

а также осуществляется вычисление приращения порядка

35

А Р Рн - Р

но.

Новое значение операнда и вычисленное значение приращения порядка выдается для дальнейшего использования в гибридную часть ABC одновременно с управляющими сигналами.

Режим ввода процессора устанавливается подачей сигнала низкого уровня (Запись) на вход 15.1 режима работы и синхронизации. При этом в блоке 11 управления элементом 29-памяти (фиг.4, табл.7) формируются управляющие сигналы на выходе, а также на D-триггере 33 по приходу синхроимпульса п устанавливается сигнал Процессор занят, поступающий на выход

(18.1) поля внешнего управления.

По управляющим сигналам (19.4, 19.5) поля 19 местного управления.блок 1 устанавливается на передачу информации с второго входа-выхода на первый. Первый

мультиплексор 4 передает информацию с второго входа на выход. Таким образом 16- тиразрядное значение операнда поступает на информационные входы (1) блока 7 оперативной памяти, блока 9 и без изменений

поступает на второй информационный вход-выход 16 процессора.

Шинный формирователь 2 устанавливается на передачу с входа-выхода (2) на выход, а второй мультиплексор 5 по сигна- лам поля местного управления включен на передачу с первого входа на выход. При этом адрес операнда поступает с адресного входа-выхода 13 процессора на вход регистра 6 адреса и фиксируется на пери- од обработки по управляющему сигналу поля местного управления (19.10) при высоком уровне импульса ъ. По установленному адресу на адресном входе (2) блока 7 оперативной памяти, прежнее значение операнда (по Т2 ) заносится в регистр 8 операнда. Затем осуществляется запись нового значения, установленного на информационном (1) входе операнда в блоке оперативной памяти.

Блок 10 постоянной памяти по установленному на входе адресу анализирует тип операнда и выдает соответствующую команду на вход (2) блока 11 управления. Арифметико-логический блок 9 (фиг.З), срав- нивая поступившие на первый информационный вход новое значение и зафиксированное на втором информационном входе старое значение порядка, вычисляет на элементах 24 и 25 величину его изменения и выдает на информационный выход 17 приращения порядка. Одновременное выдачей информации блок управления формирует на управляющих выходах поля внешнего управления 18 следующие сигналы: 18.2 - А- управляющий сигнал, который выдается синхронно с выдачей приращения порядка операнда; 18.3 - RA - Знак приращения порядка, 18.4 -д-управляющий сигнал, который выдается синх- ронно-с выдачей порядка операнда; 18.5-х - управляющий сигнал, который выдается синхронно с выдачей информации о мантиссе операнда.

Режим обработки процессора является основным рабочим режимом и предназначен для преобразования цифровой части с учетом переноса из аналоговой части операндов алигативного типа, которые непрерывно изменяются при решении задачи алигативной вычислительной системой в масштабе реального времени.

На адресный вход 14 процессора поступает адрес (номер) запрашивающего устройства, который по управляющим сигналам (управляющие входы 19.3 и 19.9) фиксируется по заднему фронту на период обработки на регистрах 20 блока формирования адреса 3 (фиг.2). Режим обработки

устанавливается подачей сиг-нала низкого уровня Обработка на вход (15.2) режима работы и синхронизации. После этого блок 11 управления (фиг.4) формирует сигнал на выходе D-триггера 33 Процессор занят, который поступает на выход (18.1) поля внешнего управления.

Элементом 29 памяти (фиг.4) в соответствии с табл.7 вырабатываются управляющие сигналы, по которым блок 1 и шинный формирователь 2 отключаются соответственно от информационной и адресной шин системы. Сигналы, поступающие на управляющие (3) входы мультиплексора, переключают их на передачу информации от первого входа на выход первого 4 мультиплексора и от второго входа на выход второго 5 мультиплексора.

Зафиксированному номеру запрашиваемой памяти 21 (фйг.2) согласно табл.1 ставится в соответствие адрес требующего обработки операнда. Этот адрес поступает на регистр 6 адреса и устанавливается на период обработки на адресном (2) входе блока 7 оперативной памяти и входе блока 10 постоянной памяти. Затем происходит считывание с блока оперативной памяти прежнего значения операнда, занесение его (по Т2) в регистр операнда 8 и установка на втором информационном входе арифметико-логического блока 9 для преобразования.

В блоке 10 постоянной памяти в соответствии с записанной в ППЗУ программой (табл.6) определяется тип операнда и необходимость выдачи его нового значения на общие шины вычислительной системы и выдается соответствующая команда в блок 11 управления. На элементах 30-32 памяти (фиг.4) анализируются: информация о знаке переноса, поступающая на вход (15.4) процессора, значение старших разрядов мантиссы и порядка, а также знаковые разряды мантиссы и приращения порядка, после чего на первый выход блока управления, а следовательно, и на управляющий вход (3) АЛБ 9 поступают соответствующие сигналы. По этим сигналам в АЛБ элементом 22 памяти (фиг.З) и сумматором 26 осуществляется преобразование мантиссы, а элементом 23 памяти - порядка операнда. Одновременно элементом 25 памяти осуществляется вычисление приращения порядка операнда.

Если тип операнда - с фиксированной точкой, то на элементах 22, 26 и 23 АЛБ по командам с блока 11 управления происходит вычисление 16-разрядного значения операнда, причем на элементе 22 вычисляются младшие разряды операнда, а на элементе 23 - вычисляются старшие разряды. Новое значение операнда поступает на второй информационный вход-выход 16 процессора, а также поступает на информационный вход (1) блока оперативной памяти.

Если новое значение операнда необходимо сразу же выдать на общие шины али- гативной вычислительной системы, то в соответствии с поступающей на вход кода операции блока управления командой на элементе 29 памяти (фиг.4) формируются сигналы, поступающие на поле местного управления. По этим сигналам блок 1 и шинный формирователь 2 включаются на передачу информации с первого входа на второй вход-выход. При этом адрес операнда с блока 3 формирования адреса через второй мультиплексор 5 и шинный формирователь поступает на адресный вход-выход 13 процессора.

Новое значение операнда поступает через блок 1 на первый информационный вход-выход 12 процессора. По тактирующему сигналу Тз происходит выдача управляющих сигналов на выходы поля внешнего управления 18 процессора, а также производится запись нового значения операнда на место его прежнего значения в блоке 7 оперативной памяти. В дальнейшем при отсутствии сигнала запроса на обработку следующим т снимается сигнал Процессор занят, и процессор переходит в режим ожидания.

Для преобразования операндов неали- гативного типа одновременной подачей сигналов Запись и Обработка на вход 15 режима работы и синхронизации может устанавливаться режим, при котором поступа- ющий с общих шин вычислительной системы операнд перед записью в блок оперативной памяти и выдачей на выходы 16 и 17 процессора преобразуется в блоке 9 аналогично режиму обработки. Тип обрабатываемых операндов, а также виды их преобразования легко изменить без изменения структуры процессора, а лишь перепрограммировав соответствующие элементы памяти.

Режим вывода имеет низший приоритет и предназначен для вывода любого из операндов для индикации или анализа на общую информационную шину алигативной вычислительной системы. Адрес выводимого операнда устанавливается на адресном входе-выходе 13 процессора, а сигнал низкого уровня Чтение, задающий режим, поступает на вход 15 процессора. Блок 11

управления вырабатывает сигналы, поступающие на поле местного управления, по которым блок 1 ввода-вывода переключается на передачу информации от первого входа-выхода на второй, а следовательно, на выдачу информации на первый информационный вход-выход 12 процессора. Шинный формирователь 2 включен на передачу информации об адресе операнда от второго

входа-выхода на вход блока, а второй мультиплексор 5 - на передачу от первого входа на выход.

Таким образом, адрес выводимого операнда поступает с адресного входа-выхода

13 процессора на вход регистра 6, запоминается (по Т) на период вывода и устанавливается на адресном входе (2) блока 7 оперативной памяти.

С блока 11 управления выдаются сигналы на поле местного управления, по которым хранящаяся информация об операнде считывается с блока оперативной памяти, фиксируется в регистре 8 операнда (по Г2) и поступает на второй информационный вход

блока 9. Без преобразования информация поступает на информационный выход АЛ Б 9, а следовательно, через первый блок ввода-вывода - на первый информационный вход-выход 12 процессора.

В режиме вывода на выходах поля 18 внешнего управления процессора вырабатывается только сигнал Процессор занят (18.1, фиг.4), остальные сигналы не вырабатываются. По окончании сигнала Чтение

передним фронтом сигнала т процессор устанавливается в исходный режим ожидания.

40

Формула изобретения

Процессор, содержащий первый и второй мультиплексоры, блок оперативной памяти, блок постоянной памяти, арифметико-логический блок, блок управления, причем выход первого мультиплексора соединен с информационным входом блока оперативной памяти, выход признаков результата арифметико-логического блока соединен с входом логических условий блока

управления, выход первого разряда поля местного управления которого соединен с управляющим входом первого мультиплексора, выходы второго и третьего разрядов поля местного управления блока управления соединены соответственно с входами записи-чтения и выборки блока оперативной памяти, вход режима работы и синхронизации процессора соединен с входом кода операции и синхронизации блока управления, выход поля внешнего управления которого соединен с управляющим выходом продессора, о тличающийся тем, что, с целью повышения быстродействия за счет исключения буферных пересылок операндов, процессор дополнительно содержит блок ввода-вывода, шинный формирователь, блок формирования адреса, регистр адреса, регистр операнда, причем первый информационный вход-выход процессора соединен с первым информационным входом-выходом блока ввода-вывода, второй информационный вход-выход процессора соединен с первым информационным входом первого мультиплексора, первым информационным выходом арифметико-логического блока и вторым информационным входом-выходом блока ввода-вывода, выход блока ввода-вывода соединен с вторым информационным входом первого мультиплексора, выход которого соединен с первым информационным входом арифметико-логического блока, второй информационный выход которого является информационным выходом процессора, информационный выход блока оперативной памяти соединен с информационным входом регистра операнда, выход которого соединен с вторым информационным входом арифметико-логического блока, адресный вход-выход процессора соединен с информационным входом-выходом шинного формирователя, информационный выход которого соединен с первым информационным входом второго мультиплексора, выход которого соединен с информационным входом шинного формирователя и информационным входом регистра адреса, выход которого соединен с ад- ресными входами блока оперативной памяти и блока постоянной памяти, выход

блока постоянной памяти, соединен с входом кода операции блока управления, выход поля операций которого соединен с входом кода операции арифметико-логического блока, адресный вход процессора соединен с информационным входом блока формирования адреса, выход которого соединен с вторым информационным входом второго мультиплексора, выход четвертого разряда поля местного управления блока

управления соединен с первым управляющим входом блока ввода-вывода и первым управляющим входом шинного формирователя, выход пятого разряда поля местного управления блока управления соединен с

вторым управляющим входом блока ввода- вывода, выход шестого разряда поля местного управления блока управления соединен с вторым управляющим входом шинного формирователя, выход седьмого

разряда поля местного управления блока управления соединен с управляющим входом второго мультиплексора, выход восьмого разряда поля местного управления блока управления соединен с входом синхронизации регистра операнда, выходы третьего и десятого разрядов поля местного управления блока управления соединены соответственно с первым и вторым управляющими входами блока формирования адреса, выход десятого разряда поля местного управления блока управления соединен с входом синхронизации регистра адреса.

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Процессор | 1977 |

|

SU691858A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

Устройство относится к вычислительной технике, в частности к процессорам для обработки цифровой информации, и может быть использовано при построении специализированных многопроцессорных систем большого быстродействия для моделирования динамических объектов и систем управления в алигативных вычислительных системах, а также в измерительных системах, работающих в режиме реального времени. Процессор имеет три основных режима функционирования и позволяет обрабатывать операнды, представленные в форме с фиксированной или плавающей точкой, которые изменяются в процессе решения динамической задачи. Целью изобретения является повышение быстродействия за счет исключения буферных пересылок операндов. Процессор содержит первый и второй мультиплексоры, блоки оперативной и постоянной памяти, блок управления, арифметико-логический блок, блок формирования адреса, блок напряжения, шинный формирователь, регистры адреса и операнда. 6 ил., 10 табл. (Л

,

I 00 01 02 I 03 Г 04 I 05 I 06 I 07 | 08 I 09 I ОЛ I 0В 1 ОС Т OD j ОЕ OF

Таблица 7

12

13

1Ц

Г

20

Л

1)

25

«О1

Риг. 2

(f)

(2)

(3)

Фиг. Ъ

(2)

(2)

Li

J l

Xl

Ъь

1725224 (3)

Фиг. Ц

(1) VocjfNfe 5056 si $o so

n

™™J x

.

t

N

§гй

е

.& Ј

Фиг. 6

(1) (2) (72)

| Грездов Г.И., Космач Ю.П., Логвиненко Ю.П | |||

| Модульная организация вычислений в гибридных имитационных моделях | |||

| - Электронное моделирование, 1979, № 1, Киев: Наукова думка, с.75-80 | |||

| Операционное устройство микропроцессорной вычислительной системы | 1982 |

|

SU1198532A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки данных | 1984 |

|

SU1352498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1992-04-07—Публикация

1989-11-04—Подача