(.

1

чда

N:

СП

Изобретение относится к электронной вычислительной технике и может быть использовано в аппаратуре автоматического контроля и диагностики цифровых узлов.

Целью изобретения является повышение достоверности контроля.

Цель достигается за счет обеспечения контроля при граничных значениях логических уровней на входных контактах и проверки соответствия логических уровней на выходных контактах,допусти.мым по техническим условиям значениям.

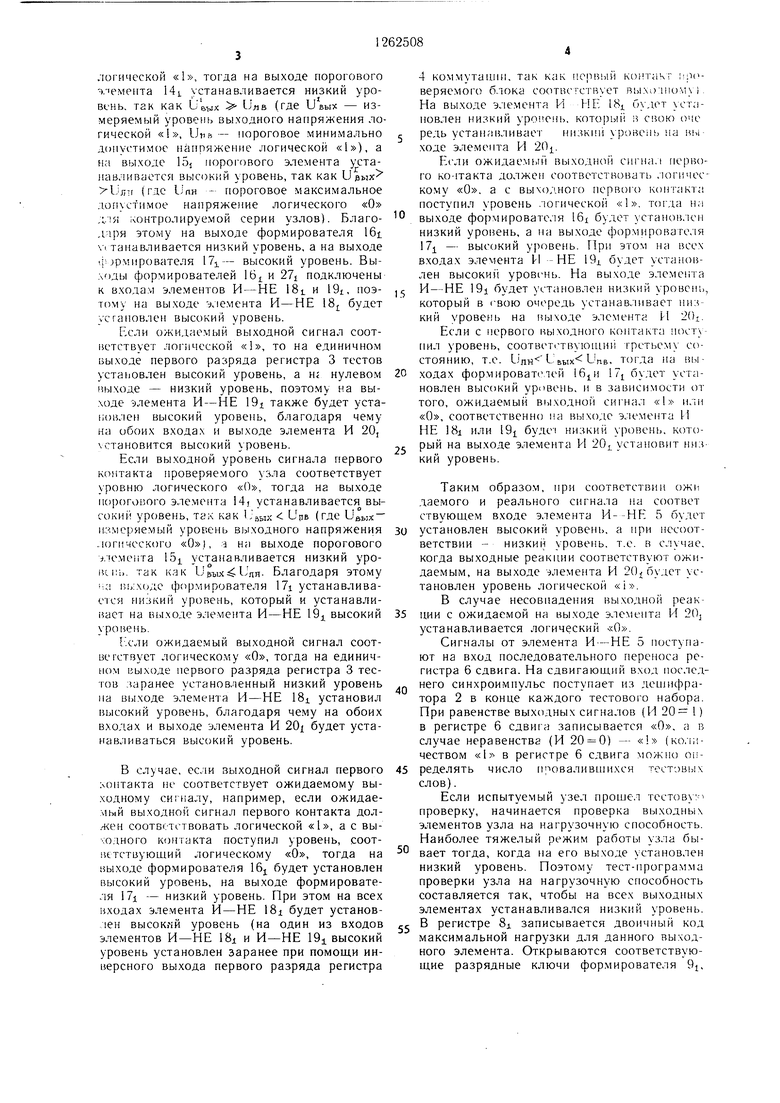

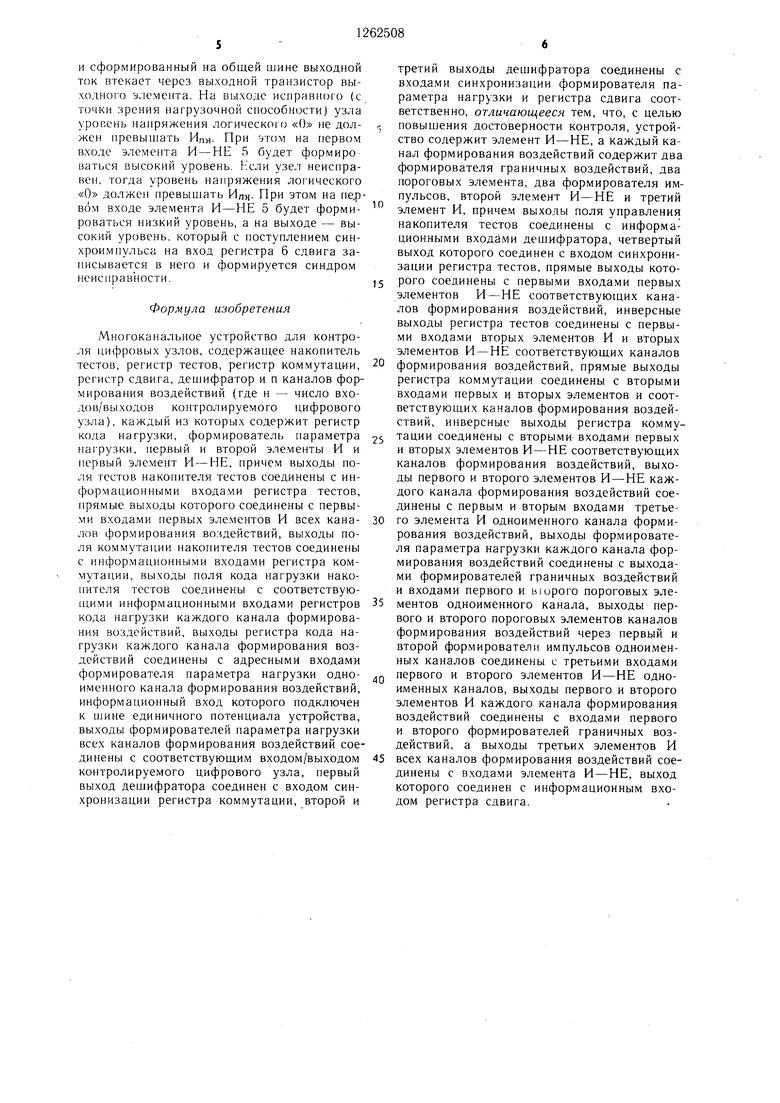

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема устройства для одного канала формирования воздействия.

Устройство содержит накопитель 1 тестов, дешифратор 2, регистр 3 тестов, регистр 4 коммутации, элемент И-НЕ 5, регистр 6 сдвига, проверяемые блок 7, группу регистPOL 8i-8п кодов нагрузки, группу формирователей 9i-9ппараметров нагрузки, элементы И lOi-lOn и ) -lln, группу формирователей 12i-12п граничных воздействий (граничных уровней логических «1), группу формирователей 13i-13л граничных воздействий (граничные уровни логических «О) пороговые элементы и ISj-15п, формирователи 16i - 16п и IT -17п импульсов, элементы И-НЕ 18i-- 8nH 19, - 19п, элементы И 20,. - 20п.

Устройство работает следующим образом.

Проверяемый узел 7 имеет и контактов, каждый из которых может быть входным и выходным. В начале каждого теста в накопителе 1 тестов записана информация, которая задает распределение входных и выходных контактов проверяемого узла и величину нагрузки, которую можно обеспечить отдельно для каждого выходного контакта, чтобы проверить работу узла в наихудшем режиме.

Структура слова тест-программы состоит из двух полей: поля тестов и поля управления. В поле тестов указывается состояние регистров 3, 4 и 8 в данном тесте, а в поле управления - адрес абонента, который должен принять информацию.

Информационная часть слова, поступающая из поля тестов накопителя 1 тестов, поступает на информационные входы регистров теста, регистров коммутации и регистра кодов нагрузки. С выходов поля управления управляющее слово поступает на деП1ифратор 2 с импульсом сопровождения. Выходы дешифратора 2 подключены к синхронизирующим входам регистров теста, коммутатора и кодов нагрузки, поэтому по номеру регистра (абонента), записанному в управляющем поле блока 1, информация принимается регистром 3 тестов, регистром 4 коммутатора или регистром 8f- 8п кодов нагрузки при помощи импульса, сформированного на соответствующем выходе дешифратора 2.

Один выход дешифратора 2 используется для формирования сдвигающего импульса регистра 6 сдвига, для чего в конце каждого теста в поле управления указывается признак обращения к регистру 6 сдвига.

Контроль испытуемого узла проводится

двумя режимами. Сначала производится тестовая проверка узла, при которой в начале работы регистр 4 коммутации устанавливается в соответствующее входу выходу состояние (для входных контактов единичное, для выходных - нулевое). Триггеры всех регистров 8i-S-n устанавливаются в нулевое состояние, поэтому на выходной шине формирователей 9i.-9птоки не формируются. После этого тест-слово при помощи выбранного выхода дешифратора 2 записывается в регистр 3 тестов.

Учитывая, что все каналы устройства функционируют аналогично, рассмотрим работу устройства на примере одного канала, например первого (фиг. 2).

Если первый контакт испытуемого узла

входной и на него нужно подать граничный уровень логической «1, тогда на единичном выходе первого разряда регистра 3 тестов установлен высокий уровень, а на нулевом выходе - низкий уровень. Так как первый контакт входной, в начале работы на единичном выходе первого регистра 4 ко.ммутации установлен высокий уровень, поэто.му на выходе элемента И lOi будет высокий, а на выходе элемента И И - низкий уровень. При помощи высокого уровня на выходе элемента И lO-i реле формирователя 2(

срабатывает, и через замкнутый контакт реле на первом входе проверяемого узла устанавливается граничный уровень логической «1.

Если первый контакт испытуемого узла

входной, и на него нужно подать граничный уровень логического нуля, тогда на нулевом выходе первого разряда регистра 3 тестов установлен высокий уровень, а на единичном выходе - низкий уровень. На выходе

элемента И llj устанавливается высокий уровень, при помощи которого реле формирователя 13i срабатывает, и через замкнутый контакт реле на первом входе проверяемого узла устанавливается граничный уровень логического «О.

Если первый контакт проверяемого узла выходной, тогда на выходах элементов И lOj. и И llj установлен низкий уровень, выходы формирователей 12 и 131становятся электрически нейтральными и не оказывают

искажающего влияния на выходной сигнал

проверяемого узла, поступающий в канал.

Если выходной сигнал первого контакта

проверяемого узла соответствует уровню

логической «1, тогда на выходе порогового ).емеита 14i. устанавливается низкий уровень, так как LUwx ияв (где ивыу - измеряемый уровень выходного напряжения логической «1, IJtiB - пороговое минимально допустимое напряжение логической «1), а на выходе loj порогового элемента устанавливается высокий уровень, так как Урых ljj;n (где UaH - пороговое максимальное aofiycTHMoe напряжение логического «О Д.1Я контролируемой серии узлов). Благодя.ря этому на выходе формирователя 16i -i танавливается низкий уровень, а на выходе rji рмпрователя высокий уровень. Вы.чоды формирователей 16 и 27i подключены к входам элементов И - НЕ 18. и 19i, поэтому на выходе элемента И-НЕ 18 будет установлен высокий уровень.

Если ожидаемый выходной сигнал соответствует логической «1, то на единичном выходе первого разряда регистра 3 тестов установлен высокий уровень, а Hi нулево.м иыходе - низкий уровень, поэтому на выходе элемента И-НЕ 19jr также будет установлен высокий уровень, благодаря чему на обоих входах и выходе элемента И 20, становится высокий уровень.

Если выходной уровень сигнала первого к(М1такта нроверяемого узла соответствует уровню логического «О, тогда на выходе порогового эле.мента 4 устанавливается высокий уровень, так как Ьаих Ьпв (где USMX измеряемый урОЕ.ень выходного напряжения .логического «О), а на выходе порогового .-емента 15 устанавливается низкий уровень, так клк Ug-bix Unn. Благодаря этому -.; 1,ь:ходе формирователя 17i устанавливается низкий уровень, который и устанавливает на выходе элемента И-НЕ 19, высокий ypoiieHb.

1.СЛИ ожидаемый выходной сигнал соответствует логическому «О, тогда на единичном выходе первого разряда регистра 3 тестов заранее установленный низкий уровень па выходе элемента И-НЕ 18i установил высокий уровень, благодаря чему на обоих входах и выходе элемента И 20 будет устанавливаться высокий уровень.

В случае, если выходной сигнал первого лонтакта tie соответствует ожидаемому выходному сигналу, например, если ожидаемый выходной сигнал первого контакта дол.Кен соответствовать логической «1, а с выгодного контакта поступил уровень, соответствующий логическому «О, тогда на выходе формирователя 16j будет установлен высокий уровень, на выходе формирователя 17i - низкий уровень. При этом на всех входах элемента И-НЕ 18i будет установлен высок.чй уровень (на один из входов элементов И-НЕ IBi и И-НЕ 19 высокий уровень установлен заранее при помощи инверсного выхода первого разряда регистра

4 коммутации, так как первый контлчг iipcверяемО1о блока соответствует пыхочиомх i. На выходе э.чемента И 18i Гллет установлен низкий уропень, который свою оче

редь устанавливает низкин уровень на вы ходе элемента И 20j.

Если ожидаемьн выходной сигна.1 первого контакта должен соответствовать логическому «О, а с выходного первого контакта поступил уровепь логической «1. тогда на

выходе формировате:1я 16i будет установ.лсн низкий уро15ень, а на выходе формирователя 7 - высокий уровень. При этом на всех входах элемента И -НЕ 19j, будет установлен ВЫСОКИ уровень. На выходе элемента

И - НЕ 19i будет установлен низкий уровень, который в свою очередь устанавливает низкий уровень на выходе элемента 1-1 2{)i. Если с первого выходного контакта постунил уровень, соотвст1:твую1ПиГ1 гретьемх состоянию, т.е. UnH Labix Una, тогда на вы0 ходах формирователей 17 бу.тет установлен высокий уровень, и в зависимости от того, ожидаемый выходной сигнал «1 или «О, соответственно па выходе эле.мента И НЕ 18i или 19i буде-| низкий уровень, кото5 рый на выходе элемента И 20, установит низкий уровень.

Таким образом, при соответствии ожи даемого и реального сигнала на соответ ствуюпте.м входе элемента И--HF- 5 будет 0 установлен выеокий уровень, а при несоответствии - низкий уровень, т.е. в случае, когда выходные реакции соответствуют ожидаемым, на выходе элемента И 20/будет установлен уровень логической «i.

В случае несовпадения вы.чодной реак5 НИИ с ожидаемой на выходе элемента И 20 устанавливается логический «О.

Сигналы от элемента И - НЕ 5 поступают на вход последовательного переноса регистра 6 сдвига. На сдвигающий вход послед,. него синхроимпульс поступает из ден1ифратора 2 в конце каждого тестового набора. При равенстве выходных сигналов (И 20 1) в регистре 6 сдвига записываетея «О, а Б случае неравенства (И 20 0) - « (ко.л; чеством «Ь в регистре 6 сдвига можно oi-5 ределять число провалившихся тестовых слов).

Если испытуемый узел прощел тестеву:проверку, начинается проверка выходных элементов узла на нагрузочную способность. Наиболее тяжелый режим работы узла бы0

вает тогда, когда на его выходе установлен

низкий уровень. Поэтому тест-программа проверки узла на нагрузочную способность составляется так, чтобы на всех выходных элементах устанавливался низкий уровень. В регистре 8i записывается двоичный код максимальной нагрузки для данного выходного элемента. Открываются соответствующие разрядные ключи формирователя 9,

и сформированный на обшей шине выходной ток Езтекает через выходной транзистор выходногч) э.юмента. На выходе исправного (с точки зрения нагрузочной способности) узла уровень напряжения логическо о «О не должен превыптть Ипн- При этом на нервом входе элемента И - НЕ 5 будет формиро ваться высокий уровень. узел неиснравен, тогда уровень напряжения логического «О должен превышать Илд. При этом на nefвом входе элемента И - НЕ 5 будет формироваться низкий уровень, а на выходе - высокий уровень, который с поступлением синхроимпульса на вход регистра 6 сдвига записывается в него и формируется синдром неисправности.

Формула изобретения

Многоканальное устройство для контроля пифровых узлов, содержан1ее накопитель тестов, регистр тестов, регистр ко.ммутации, регистр сдвига, дешифратор и п каналов формирования воздействий (где н - число входов/выходов контролируемого цифрового узла), каждый из которых содержит регистр кода нагрузки, формирователь параметра нагрузки, первый и второй элементы И и первый элемент И - НЕ, причем выходы поля тестов накопителя тестов соединены с информационными входа.ми регистра тестов, прямые выходы которого соединены с первыми входами первых элементов И всех каналов формирования воздействий, выходы поля коммутации накопителя тестов соединены с информационными входами регистра коммутации, выходь поля кода нагрузки накогштеля тестов соединены с соответствующими информационными входами регистров кода нагрузки каждого канала формирования воздействий, выходы регистра кода нагрузки каждого канала формирования воздействий соединены с адресными входами формирователя параметра нагрузки одноименного канала формирования воздействий, информационный вход которого подключен к шине единичного потенциала устройства, выходы формирователей параметра нагрузки всех каналов формирования воздействий соединены с соответствуюш,им входом/выходом контролируемого цифрового узла, первый выход дешифратора соединен с входом синхронизации регистра коммутации, второй и

третий выходы дешифратора соединены с входами синхронизации формирователя параметра нагрузки и регистра сдвига соответственно, отличающееся тем, что, с целью

повышения достоверности контроля, устройство содержит элемент И-НЕ, а каждый канал формирования воздействий содержит два формирователя граничных воздействий, два пороговых элемента, два формирователя импульсов, второй элемент И-НЕ и третий элемент И, причем выходы поля управления накопителя тестов соединены с информационными входами дешифратора, четвертый выход которого соединен с входом синхронизации регистра тестов, прямые выходы которого соединены с первыми входами первых элементов И-НЕ соответствующих каналов формирования воздействий, инверсные выходы регистра тестов соединены с первыми входами вторых элементов И и вторых элементов И-НЕ соответствующих каналов

0 формирования воздействий, прямые выходы регистра коммутации соединены с вторыми входами первых и вторых элементов и соответствующих каналов формирования воздействий, инверсные выходы регистра комму5 тации соединены с вторыми входами первых и вторых элементов И-НЕ соответствующих каналов формирования воздействий, выходы первого и второго элементов И-НЕ каждого канала формирования воздействий соединены с первым и вторым входами третье0 го элемента И одноименного канала формирования воздействий, выходы формирователя параметра нагрузки каждого канала формирования воздействий соединены с выходами формирователей граничных воздействий и входами первого и ыорого пороговых эле5 ментов одноименного канала, выходы первого и второго пороговых элементов каналов формирования воздействий через первый и второй формирователи импульсов одноименных каналов соединены с третьими входами

д первого и второго элементов И-НЕ одноименных каналов, выходы первого и второго элементов И каждого канала формирования воздействий соединены с входами первого и второго формирователей граничных воздействий, а выходы третьих элементов И

5 всех каналов формирования воздействий соединены с входами элемента И-НЕ, выход которого соединен с информационным входом регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для тестового контроля цифровых узлов электронно-вычислительных машин | 1981 |

|

SU993266A2 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

Изобретение относится к электронной вычислительной технике и может быть использовано в аппаратуре автоматического контроля и диагностики цифровых узлов. Цель изобретения - повышение достоверности контроля. Устройство содержит накопитель тестов, регистр тестов, регистр коммутации, регистр сдвига, дешифратор и каналы формирования воздействий, каждый из которых содержит регистр кода нагрузки, формирователь параметра нагрузки, элемент И-НЕ, три элемента И, два формирователя граничных значений логической единицы и логического нуля. В устройстве проводится контроль имитацией наихудших допустимых уровней входных сигналов. В условиях реальной эксплуатации цифровых узлов уровни входных сигналов, как прави,до, соответствуют средним значениям, поэтому, если в результате контроля выходные элементы проверяемого узла оказываются работоспособными при наихудших входных сигналах, это гарантирует их работоспособность во всем диапазоне уровней входных сигналов. Можно также проводить измерение уровней выходных сигналов проверяемого блока. 2 1-;л. (Л

| Устройство для тестового контроля цифровых узлов электронных вычислительных машин | 1976 |

|

SU694863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового контроля цифровых узлов электронно-вычислительных машин | 1981 |

|

SU993266A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-04-01—Подача