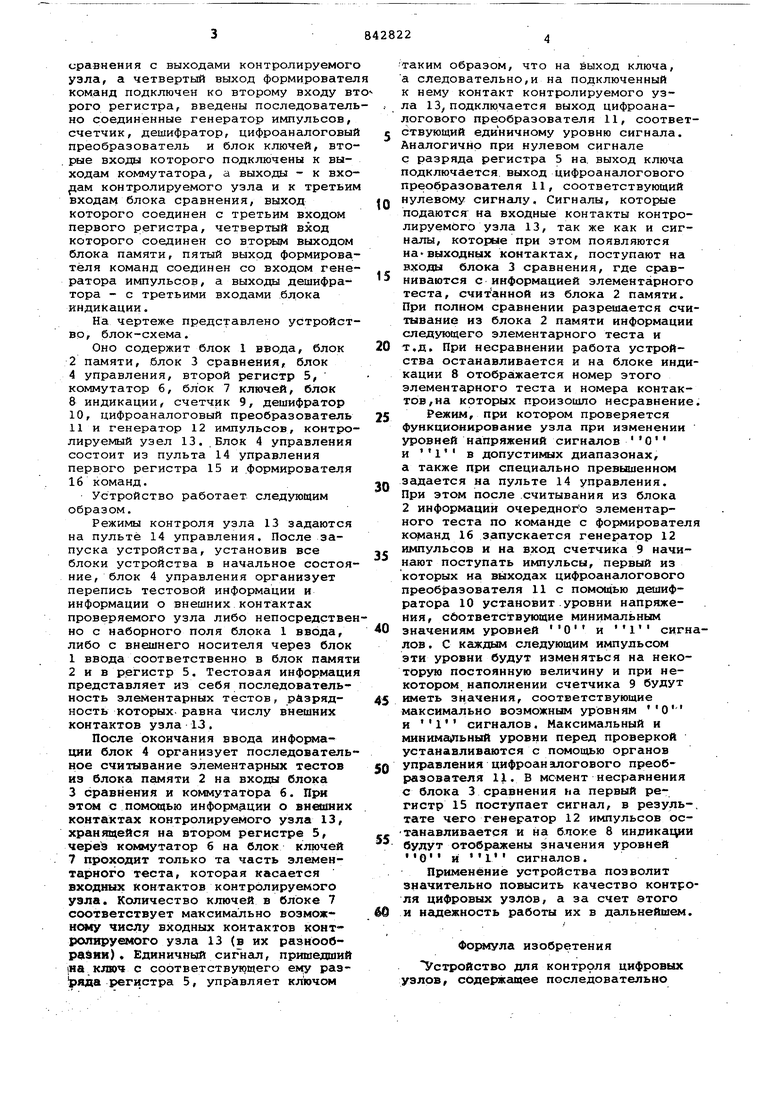

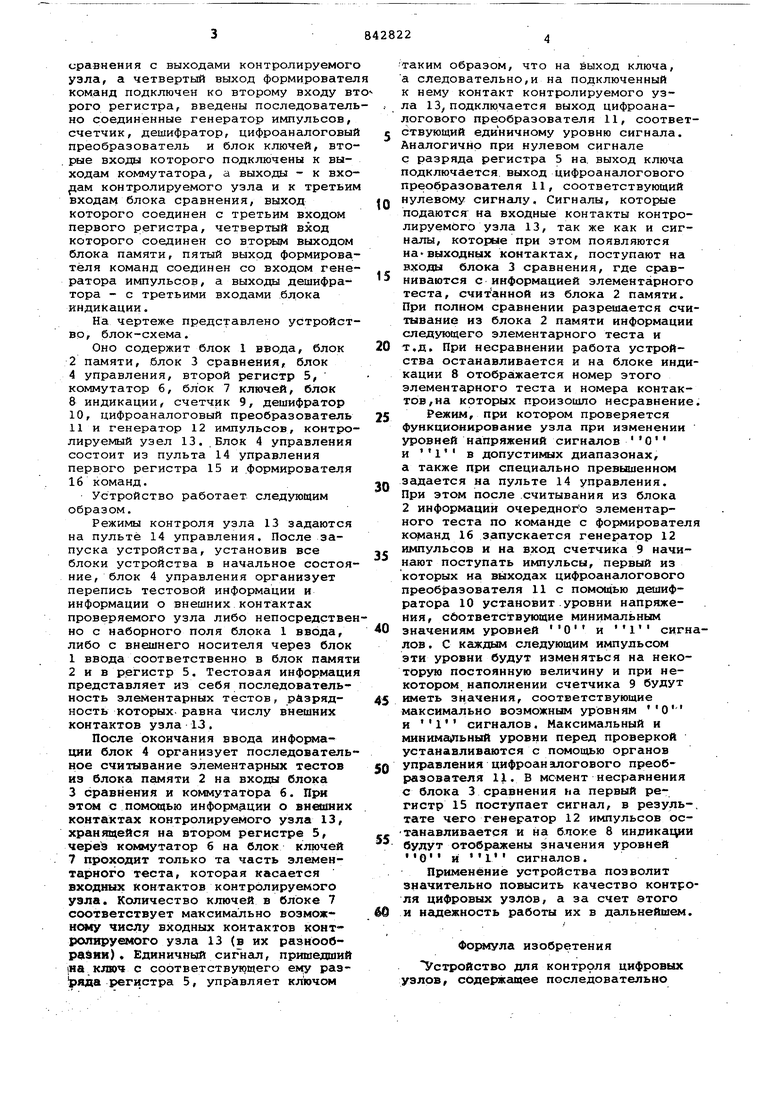

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ сравнения с выходами контролируемог узла, а четвертый выход формировате команд подключен ко второму входу в рого регистра, введены последовател но соединенные генератор импульсов, счетчик, дешифратор, цифроаналоговы преобразователь и блок ключей, вто рые входы которого подключены к выходам коммутатора, а выходы - к вхо ам контролируемого узла и к третьи входам блока сравнения, выход которого соединен с третьим входом первого регистра, четвертый вход которого соединен со вторым выходом блока памяти, пятый выход формирова теля команд соединен со входом гене ратора импульсов, а выходы дешифратора - с третьими входами блока индикации. На чертеже представлено устройст во, блок-схема. Оно содержит блок 1 ввода, блок 2 памяти, блок 3 сравнения, блок 4 управления, второй регистр 5/ коммутатор 6, блок 7 ключей, блок 8 индикации, счетчик 9, дешифратор 10, цифроаналоговый преобразователь 11 и генератор 12 импульсов, контро лируемый узел 13..Блок 4 управления состоит из пульта 14 управления первого регистра 15 и .формирователя 16 команд. Устройство работает следующим образом. Режимы контроля узла 13 задаются на пульте 14 управления. После запуска устройства, установив все блоки устройства в начальное состоя ние, блок 4 управления организует перепись тестовой информации и информации о внешних контактах проверяемого узла либо непосредстве но с наборного поля блока 1 ввода, либо с внешнего носителя через блок 1ввода соответственно в блок памят 2и в регистр 5. Тестовая информаци представляет из себя последовательность элементарных тестов, разрядность которых равна числу внешних контактов узла 13. После окончания ввода информа дни блок 4 организует последователь ное считывание элементарных тестов из блока памяти 2 на входа блока 3сравнения и коммутатора б. При этом с помощью информации о виешних контактах контролируемого узла 13, храншцейся на втором регистре 5, через коммутатор б на блок ключей 7 проходит только та часть элементарного теста, которая касается входных контактов контролируемого узла. Количество ключей в блоке 7 соответствует максимально возможному числу входных контактов контролируемого узла 13 (в их разнообразии) . Единичный с и г) ал, пришедший {иа ключ с соответствующего ему разряда регистра 5, управляет ключом таким образом, что на выход ключа, а следовательно,и на подключенный к нему контакт контролируемого узла 13у подключается выход цифроаналогового преобразователя 11, соответствующий единичному уровню сигнала. Аналогично при нулевом сигнале с разряда регистра 5 на. выход ключа подключается выход цифроаналогового преобразователя 11, соответствующий нулевому сигналу. Сигналы, которые подаются на входные контакты контролируемого узла 13, так же как и сигналы, которые при этом появляются на ВЫХОДНЫХ контактах, поступают на входы блока 3 сравнения, где сравниваются с информацией элементарного теста, считанной из блока 2 памяти. При полном сравнении разрешается считывание из блока 2 памяти информации следующего элементарного теста и т.д. При несравнении работа устройства останавливается и на блоке индикации 8 отображается номер этого элементарного теста и номера контактов, на которых произошло несравнение. Режим, при котором проверяется функционирование узла при изменении уровней напряжений сигналов и Ч в допустимых диапазонах, а также при специально превышенном задается на пульте 14 управления. При этом после .считывания из блока 2 информации очередного элементарного теста по команде с формирователя команд 16 запускается генератор 12 импульсов и на вход счетчика 9 начинают поступать импульсы, первый из которых на выходах цифроаналогового преобразователя 11 с помощью дешифратора 10 установит уровни напряжения, сбответствующие минимальным значениям уровней О сигналов . С каждым следующим импульсом эти уровни будут изменяться на некоторую постоянную величину и при некотором наполнении счетчика 9 будут кметъ значения, соответствующие максимально возможным уровням О сигналов. Максимальный и минима пьный уровни перед проверкой устанавливаются с помощью органов управления цифроаналогового преобразователя 1. В момент несравнения с блока 3 сравнения на первый регистр 15 поступает сигнал, в резуль-, тате чего генератор 12 импульсов останавливается и на блоке 8 индикации будут отображены значения уровней IIQII J, tijii сигналов. Применение устройства позволит значительно повысить качество контроля цифровых узлов, а за счет этого и надежность работы их в дальнейшем. Форму па. изобретения Устройство для КОНТР9ЛЯ цифровых узлов, содержащее последовательно

соединенные пульт управления, первый регистр, формирователь команд, блок ввода, блок памяти, блок сравнения и блок индикации, второй вход которого соединен со вторым выходом формировг.теля команд, третий выход которого подключен ко второму входу блока памяти, соединенного первыми выходами с первыми входами коммутатора, вторые входы которого через второй регистр подключены к первым выходам блока ввода, подсоединенного вторым выходом ко второму входу первого регистра, вторые входы блока сравнения соединены с выходами контролируемого узла, а четвертый выход форм(;рователя команд подключен ко второму входу второго регистра, о т л и ч а. ю щ е е с я тем, что, с целью повышения достоверности результатов контроля, в устройство введены последовательно соединенные

генератор импульсов, счетчик, дешифратор, иифроаналоговый преобразователь и блок ключей, вторые входы которого подключены к выходам коммутатора, а выходы - к входсш контролируемого узла и к третьим входам блока сравнения, выход которого соединен с третьим входом первого регистра, четвертый вход которого соединен со вторым выходом блока памяти, пятый выход формирователя команд соединен со входом генератора импульсов, а выходы дешифратора-с третьими входами блока индикации.

Источники информации,

5 принятые во внимание при экспертизе

1.Авторское свидетельство СССР I 605216, кл. G 06 F 11/00, 1976.

2.Авторское свидетельство СССР 498816, кл. G 06-F 11/00, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для диагностирования группы из @ логических узлов | 1985 |

|

SU1390611A1 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

Авторы

Даты

1981-06-30—Публикация

1979-07-27—Подача