у

о

СП

ю

оо

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство передачи информации со сжатием | 1989 |

|

SU1665399A1 |

| Устройство обработки информации | 1989 |

|

SU1810892A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано в системах передачи и приема информации. Цель изобретения - повышение достоверности принимаемой информации. Устройство содержит генератор 1 импульсов, счетчик 2, мультиплексор 3, первый 4 и второй 14 блоки памяти, первый 5 и второй 15 формирователи адреса, первый 6 и второй 16 блоки сравнения приоритетов, элементы И 7,8,12,13,19,20, первый 9 и второй 21 блоки управления передачей, первый 10 и второй 11 блоки обработки информации, первый 17 и второй 18 параллельные интерфейсы. Устройство позволяет обнаружить "срабатывание" любого канала, аппроксимировать это "срабатывание", т.е. очистить от "дребезга", точно привязать ко времени, когда это "срабатывание" произошло, и формировать выходную информацию о каждом "срабатывании" в любом канале. 1 табл., 8 ил.

. 1

3

Изобретение относится к автоматике, телемеханике и вычислительной технике и может найти применение в многоканальных системах передачи и приема информации.

Цель изобретения - повьппение дрс- товерности принимаемой информации.

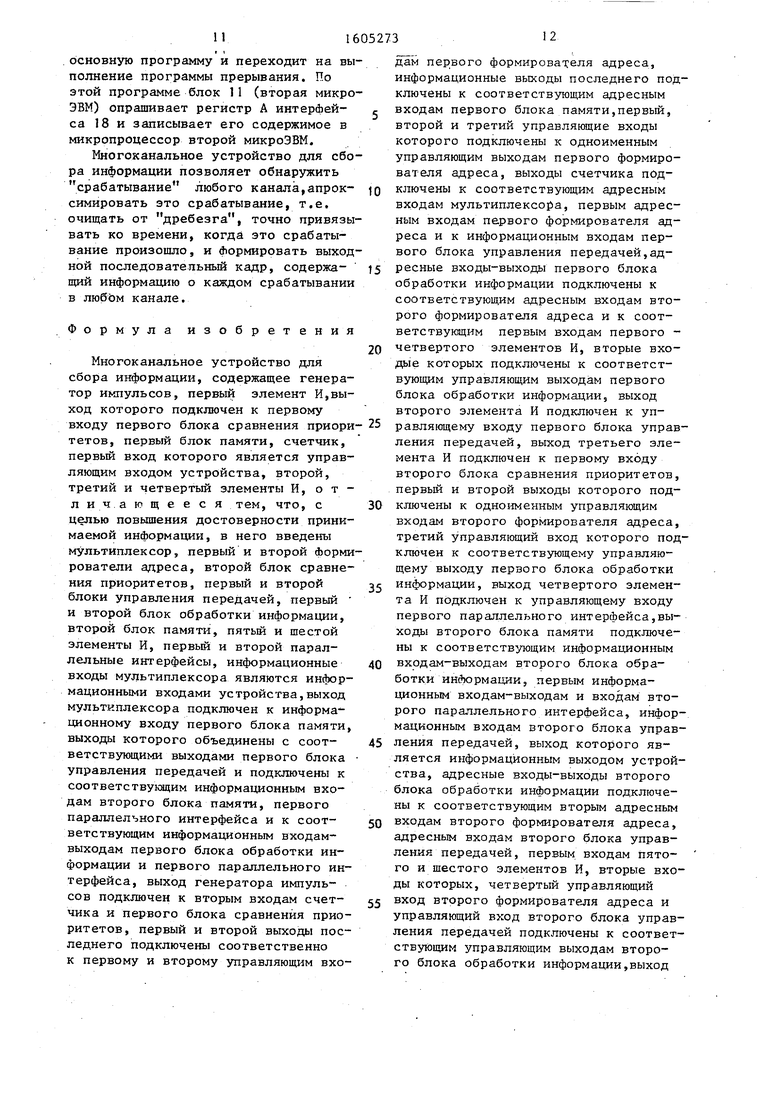

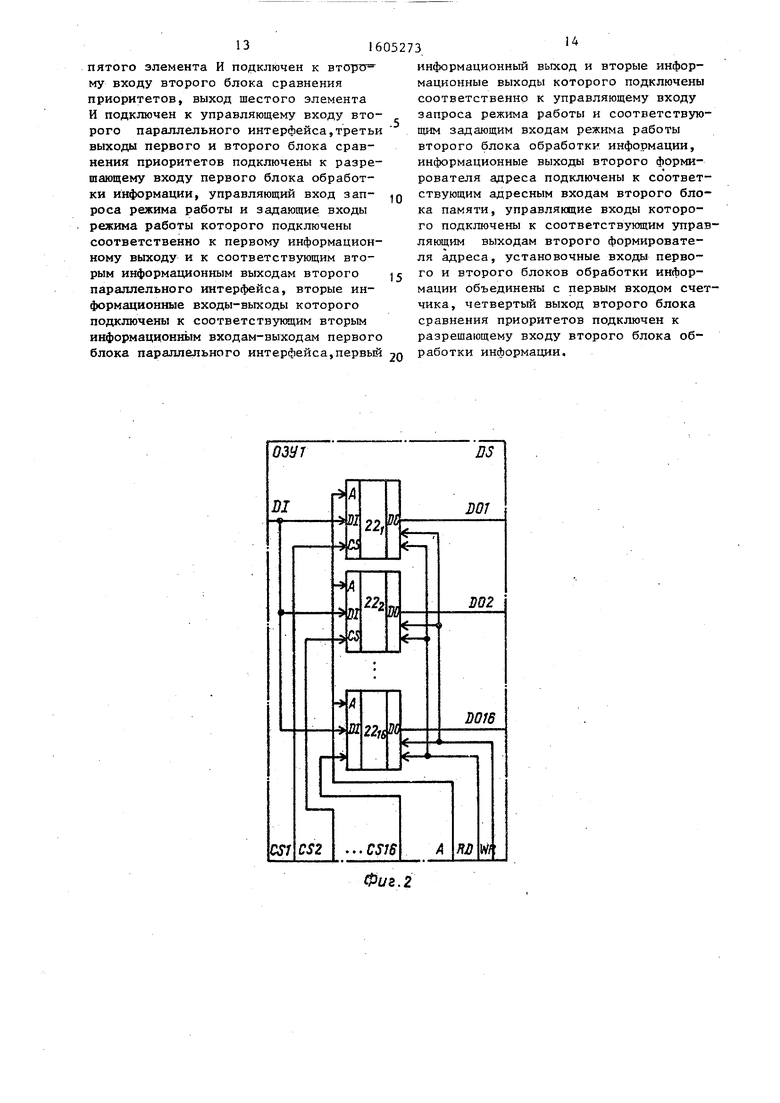

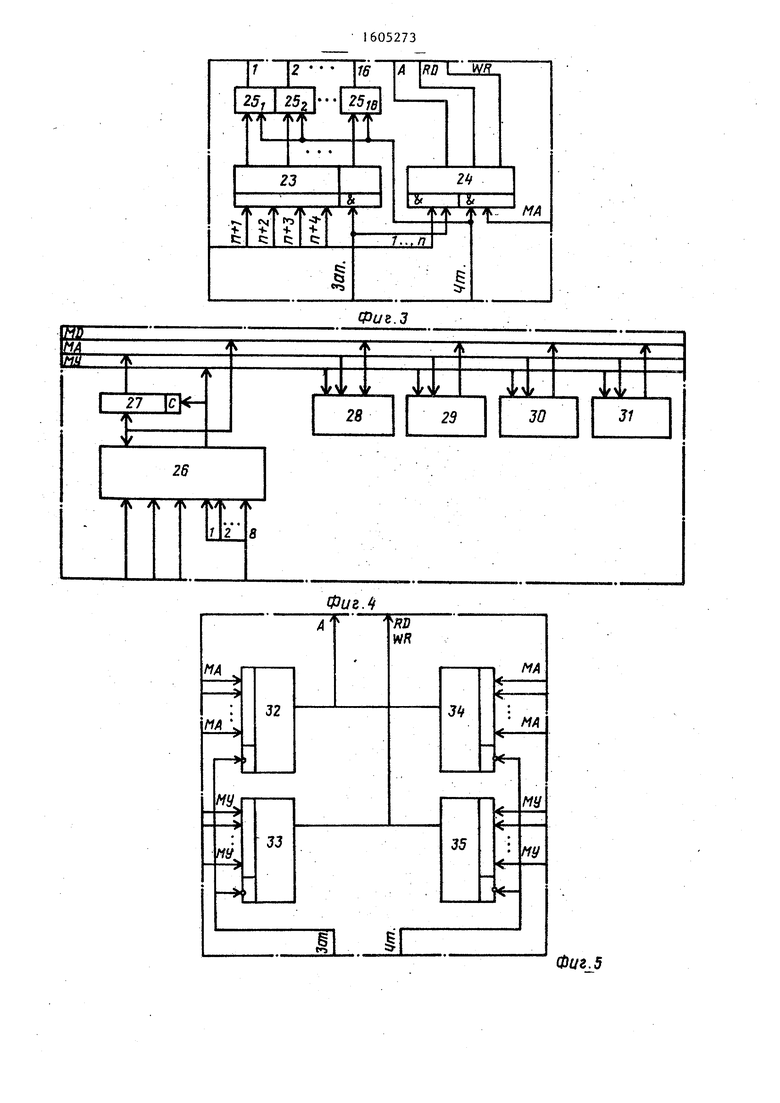

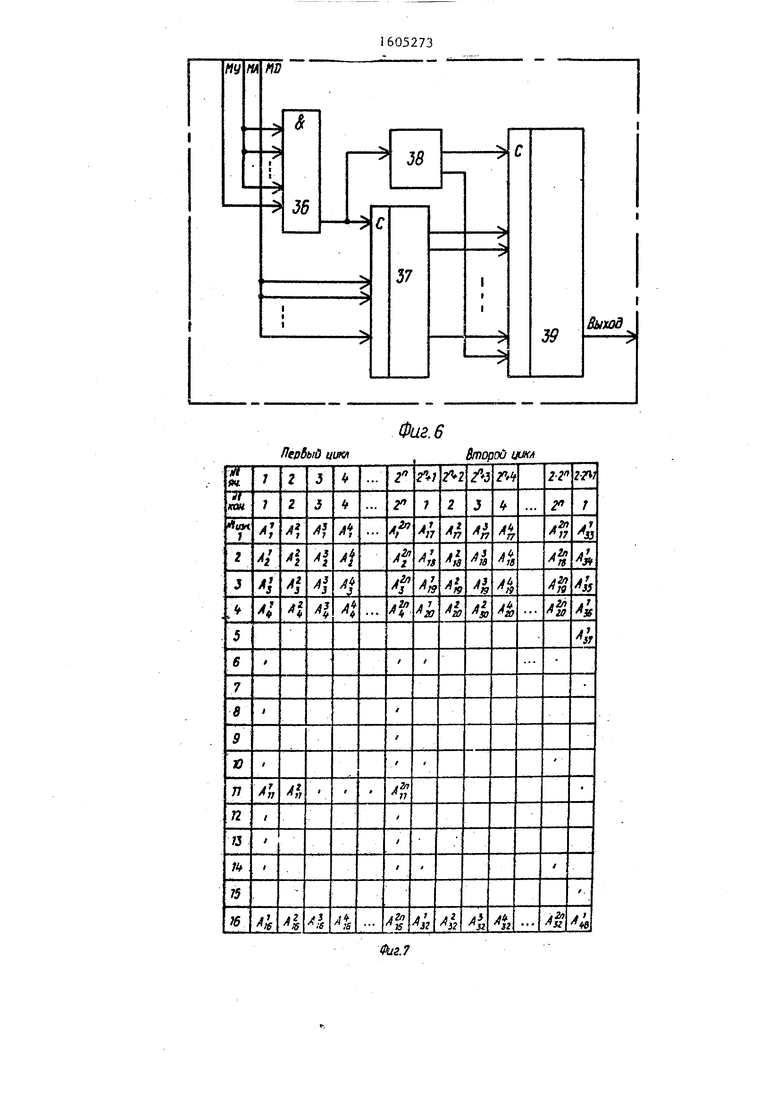

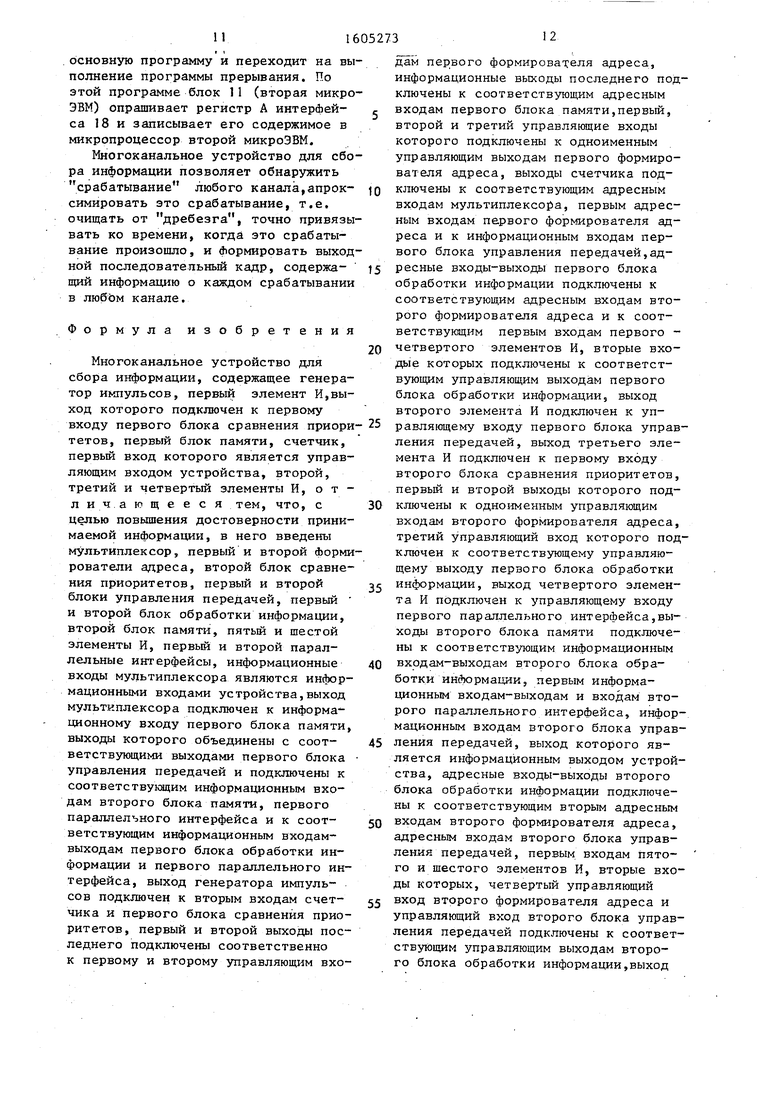

На фиг.I представлена функциональная схема устройства; на фиг.2 - фун циональная схема первого блока памя

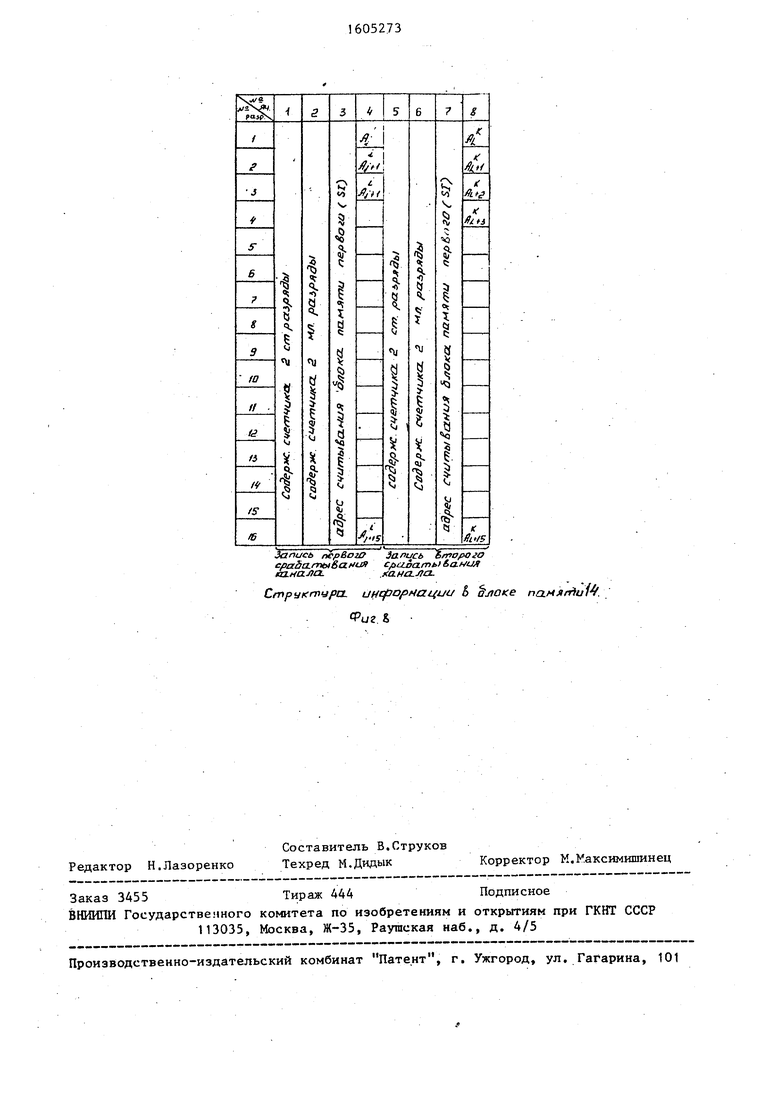

ти; на фиг.З - функциональная схема первого формирователя адреса; на фиг.4 - схема первого и второго блоков обработки информации; на фиг.З - функциональная схема второго формирователя адреса; на фиг. б - функисио- нальная схема второго блока управления передачей; на фиг.7 - структурная схема информации в первом блоке памяти; на фиг 8 - то же, во втором блоке памяти.

Устройство содержит генератор импульсов, счетчик 2, мультиплексор 3, первый блок 4 памяти, первый фор- мирователь 5 адреса, первый блок 6 сравнения приоритетов, первый 7 и . .второй 8 элементы И, первый блок 9 управления передачей, первый 10 и второй 11 блоки обработки информации третий 12 и четвертый 13 элементы И, второй блок 14 памяти, второй формирователь 15 адреса, второй блок 16 сравнения приоритетов, первый 17 и второй 18 параллельные интерфейсы, пятый 19 и шестой 20 элементы И,второй бкок 21 управления передачей.

Кроме того, на фиг.1 обозначены магистрали даннь х MD для микроЭВМ, адреса МА и управления МУ.

Блок памяти (фиг.2) содержит элементы памяти по числу кристаллов, которые можно выполнить на микросхемах серии 132 РУЗ.

Формирователь адреса (фиг.З) содержит дешифратор 23, выполненный на микросхеме серии 533 ИД7, мультиплексор 24, микросхему серии 533 КПП элементы ИЛИ 25 ) - 25 . Каждый блок обработки информации, выполненный на микроэвм (фиг.4), содержит микропроцессор 26 типа 1810 ВМ86, регистр адреса 27 - микросхема 533ТМ9, ОЗУ 2 сегмента стека - микросхема 541,РУ2 ПЗУ 29 сегмента прерывания, ПЗУ 30 сегмента кода, ПЗУ 31 начального запуска. Все ПЗУ вьтолнены на микросхеме 556РТ7. Второй формирователь адреса (фиг.5) содержит шинные формиро

5

0

5 о

5

0

5

0

5

ватели 32 - 35 на микросхемах . 589АП26.

Блок выдачи информации (фиг.6) содерзкит элемент И 36, буферный регистр 37, блок управления БУ 38,выполненный по схеме распределителя импульсов на микросхеме 533 ИР16, сдвиговьй регистр 39.

Для обеспечения работоспособности устройства входящие в его состав остальные блоки могут быть выполнены как параллельно программируемые интерфейсы типа 580ВВ55, первый блок

9управления передачей - 589АП26, мультиплексор 3 - 533КП11.

Устройство работает следующим образом .

Перед началом работы устройства поступает сигнал Сброс, который приводит в исходное состояние блоки

10и 11 и устанавливает в нуль счетчик 2.

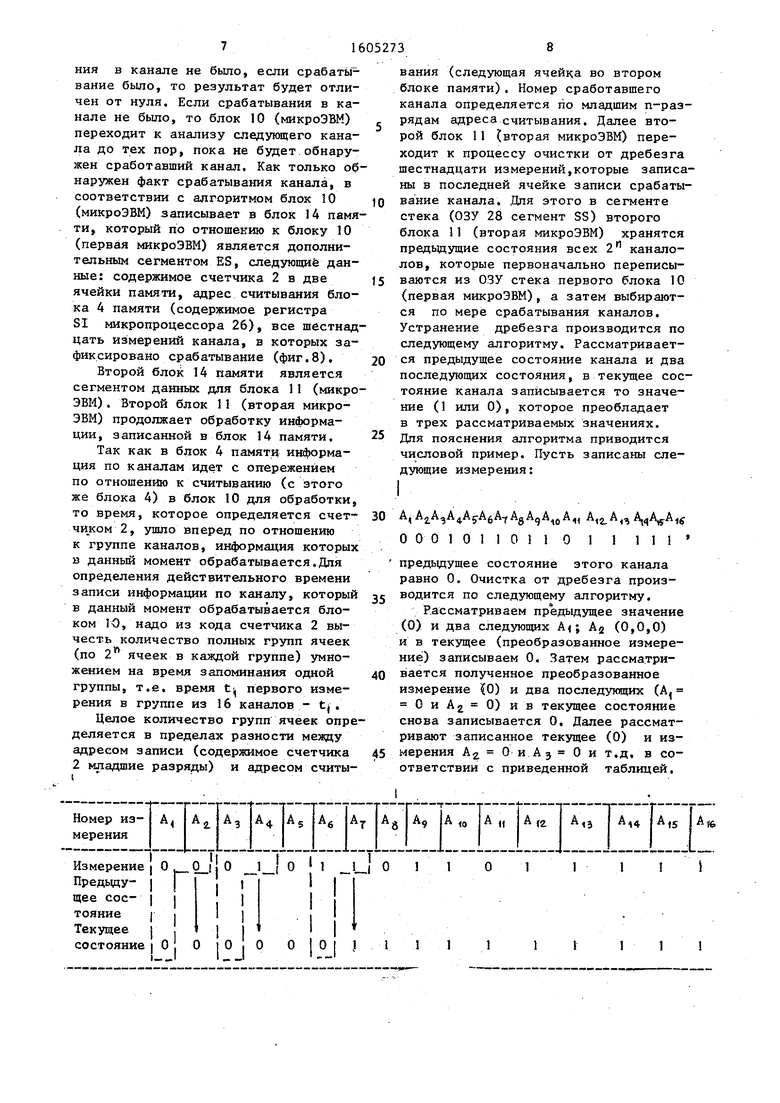

Затем счетчиком 2 пересчитываются импульсы с генератора 1 для оцифровки времени и управления мультиплексором 3. Т льтиплексор 2 опрашивает входные каналы и информация с входа устройства последовательно записывается в первый блок 4 памяти в соответствии с адресом, формируемым младшими разрядами С},,..,п счетчика 2. За время первого измерения, определяемого одним циклом опроса всех каналов, информация с них записывается в первые разряды с 1-й по 2-ю ячейки блока 4 памяти, как показано на фиг.7 1(А - AJ ). При втором измерении (второй цикл опроса) информации,поступающая по всем каналам, записывается во вторые разряды этих же ячеек (фиг.7, А - А) и т.д.

В результате шестнадцать измерений (по числу разрядов ОЗУ блока 4 памяти) записываются в первые 2 ячеек блока 4 памяти. Следовательно, при чтешет блоком 10 (микроэвм) первой ячейки блока 4 памяти в регистр общего назначения (РОН) записываются 16 измерений первого канала. Затем начинается запись информации во вторую группу ячеек 2 1,... ,2х2,ко- торые содержат измерения с 17 по 32 каждого из каналов Лиг.7 (А .т

А А - « эг згБлок 10 (микроэвм) по обращении к внешнему устройству, дешифрируемому на элементе И 8, считывает содержимое (адрес и время) счетчика 2 .

10

15

20

через блок 9, т.е. адрес записи информации в блок 4 памяти. Так как блок 4 памяти представляет сегмент данных DS для блока 10 (микроЭВМ), то адрес чтения формируется в регистре SI. Блок 10 (микроэвм) рассчитывает разность адресов записи и чтения и, если эта разность больше величины группы, т.е. между адресом считывания и адресом записи располагается целая группа каналов, то блок 10 переходит на алгоритм обработки информации каналов этой группы.

Для устранения конфликтных ситуаций, возникающих при одновременном обращении к блоку 4 памяти на запись (от генератора 1) и чтение (от блока 10), включен блок 6 сравнения приоритетов. Если в блок 4 памяти производится запись информации и в это время блок 10 обращается к этому же блоку на чтение, то чтение информации будет произведено после окончания цикла записи, а на время записи информации с блока 10 снимается сигнал готовность (RDY). Если блок 4 памяти занят чтением информации в блок 10 и в это время пришел запрос на запись, тогда обращение на запись произойдет после окончания цикла чтения.

Сигналы управления записью и чтением с блока сравнения приоритетов 6 поступают на формирователь 5, кото- рый KONwyTHpyeT адрес обращения к блоку 4 памяти. Структура записи информации в блок 4 памяти обеспечивается архитектурой самого блока 4 памяти и формирователей 5 адреса.

Дешифратор 23 (фиг.3) обеспечивает выбор кристалла в блоке 4 памяти (фиг.2, 22 ( - 22,g) по каждому из 16 разрядов ячеек, по адресу которьй поступает со счетчика 2 (разряды п+1...+п4).

Обращение к блоку 4 памяти (чтение или запись) осуществляется через мультиплексор 24, который коммутиру- ет младшие разряды адреса блока 4 памяти ИЛИ с магистрали адреса блока 10 (микроэвм) или с выходов счетчика 2.

Алгоритм блока 10 (микроЭВМ) заключается в определении Факта срабатывания канала (под фактом срабатывания сигнального канала понимают изменения информации в канале в пределах

30

25

40

45

шестнадцати измерений, которые записаны в одной ячейке блока 4 памяти. С этой целью в начальной области сегмента стека SS (ОЗУ 28 сегмента стека) , адресуемой регистром ВР процессора 26, располагаются предыдущие состояния всех 2 входных сигнальных каналов.

Срабатывание по каналу должно фиксироваться , если проход в новое состояние подтверждается не менее чем двумя измерениями. Для пояснения приводится числовой пример.

Пусть измерения по одному из каналов равны

А, jAgA AgAgA,/. , A.,A,A, 00010001000 10000

такие однократные переходы в единицу не считаются срабатыванием.Предположим, что предыдущее состояние этого канала также равно 0. Для определе- ния наличия срабатывания микропроцессор логически умножает этот двоичный код, сдвинутый на один разряд вправо, при этом место крайнего левого разряда занимает предыдущее состояние этого канала

0001 0001 0001 0000 Предыдущее сос- х 0000 ШОО1000 ШОО

ТОЯНИе --QQQQ QQQQ QQQQ QQQQ

Нулевой результат логического умножения обозначает,, что срабатывания по каналу нет. Пусть измерения по одному каналу равны

A AjA A Aj-AgAvAgA A A A jA Ai gA 1111011110111011

Предыдущее состояние равно едини- це. В этом случае логически перемножаются инверсные измерения по каналу со сдвинутой на один разряд вправо той же инверсией

Таким образом, если хотя бы одна из двух описанных проверок дает нулевой результат, значит срабатывания в канале не бьто, если срабатывание было, то результат будет отличен от нуля. Если срабатывания в канале не было, то блок 10 (микроЭВМ) переходит к анализу следующего канала до тех пор, пока не будет обнаружен сработавший канал. Как только обнаружен факт срабатывания канала, в соответствии с алгоритмом блок 10 (микроэвм) записывает в блок 14 памяти, который по отношекию к блоку 10 (первая микроэвм) является дополнительным сегментом ES, следующие данные: содержимое счетчика 2 в две ячейки памяти, адрес считывания блока 4 памяти (содержимое регистра SI микропроцессора 26), все шестнадцать измерений канала, в которых зафиксировано срабатывание (фиг.8),

Второй блок 14 памяти является сегментом данных для блока 11 (микро ЭВМ) , Второй блок 11 (вторая микро- ЭВМ) продолжает обработку информации, записанной в блок 14 памяти.

Так как в блок 4 памяти информация по каналам идет с опережением по отношению к считыванию (с этого же блока 4) в блок 10 для обработки, то время, которое определяется счет- 2, ушло вперед по отношению к группе каналов, информация которых в данный момент обрабатывается.Для определения действительного времени записи информации по каналу, который в данный момент обрабатывается блоком 10, надо из кода счетчика 2 вычесть количество полных групп ячеек (по 2 ячеек в каждой группе) умножением на время запоминания одной группы, т.е. время t первого изме

рения в группе из 16 каналов - t

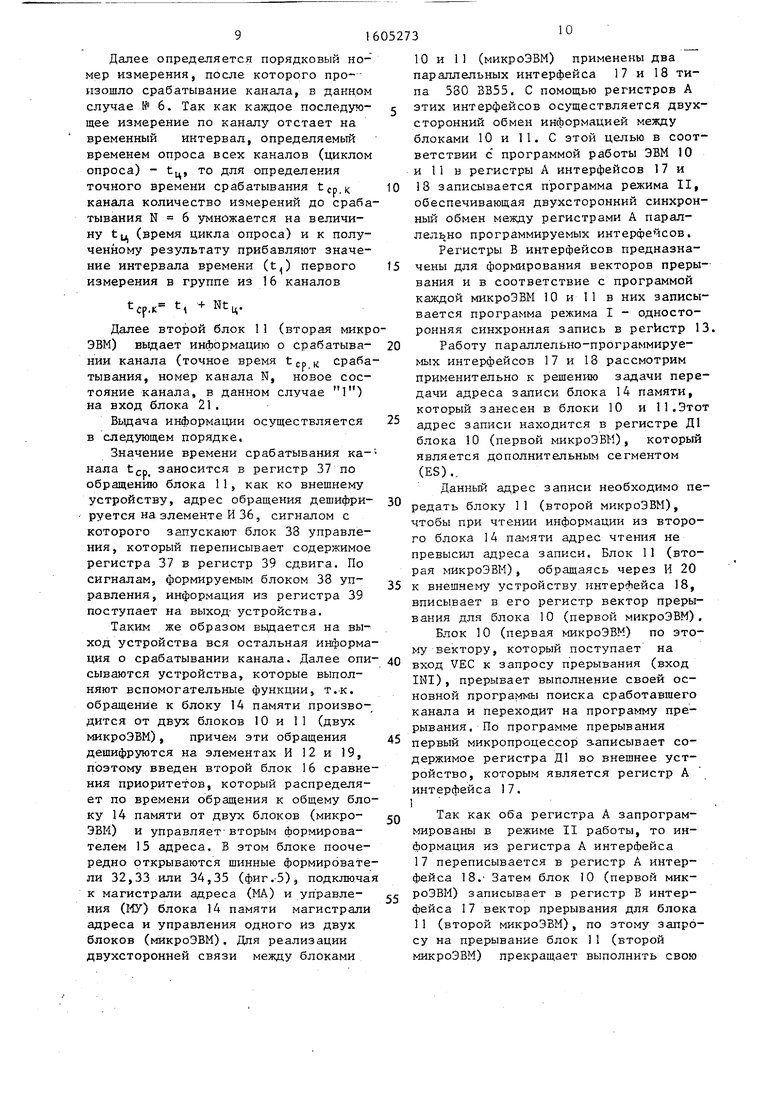

Целое количество групп ячеек определяется в пределах разности между адресом записи (содержимое счетчика 2 младшие разряды) и адресом считывания (следующая ячейка во втором блоке памяти). Номер сработавшего канала определяется по младшим п-раз- рядам адреса считывания. Далее второй блок 11 (вторая микроэвм) переходит к процессу очистки от дребезга шестнадцати измерений,которые записаны в последней ячейке записи срабатывание канала. ,Дпя этого в сегменте стека (ОЗУ 28 сегмент SS) второго блока 11 (вторая микроЭВМ) хранятся предьщущие состояния всех 2 канало- лов, которые первоначально переписываются из ОЗУ стека первого блока 10 (первая микроэвм), а затем выбираются по мере срабатывания каналов. Устранение дребезга производится по следующему алгоритму. Рассматривается предыдущее состояние канала и два последующих состояния, в текущее состояние канала записывается то значение (1 или 0), которое преобладает в трех рассматриваемых значениях. Дпя пояснения алгоритма приводится числовой пример. Пусть записаны следующие измерения;

А, A A A A A A-yAgAqA oA,, А,,, А,,, 00010110110 1 1 111

предыдущее состояние этого канала равно 0. Очистка от дребезга производится по следзгющему алгоритму.

Рассматриваем предыдущее значение (0) и два следующих Ag (0,0,0) и в текущее (преобразованное измерение) записываем 0. Затем рассматривается полученное преобразованное измерение 0) и два последунщих (А, ) ив текущее состояние снова записывается О, Далее рассматривают записанное текущее (0) и измерения А2 ОиАз О и т.д. в соответствии с приведенной таблицей.

Далее определяется порядковый номер измерения, после которого изошло срабатывание канала, в данном случае № 6. Так как каждое последующее измерение по каналу отстает на временный интервал, определяемый временем опроса всех каналов (циклом опроса) - 1ц, то для определения точного времени срабатывания ten. к канала количество измерений до срабатывания N 6 умножается на величину t ц (время цикла опроса) и к полученному результату прибавляют значение интервала времени (t) первого измерения в группе из 16 каналов

ср.к

+ Nt

ЦДалее второй блок 11 (вторая микро- ЭВМ) выдает информацию о срабатыва- 20 НИИ канала (точное время t р срабатывания, номер канала N, новое состояние канала, в данном случае 1) на вход блока 21.

Выдача информации осуществляется 25 в следующем порядке.

Значение времени срабатывания канала tcp, заносится в регистр 37 по обращению блока 11, как ко внещнему устройству, адрес обращения дешифрируется на элементе И 36, сигналом с которого запускают блок 38 управления, который переписывает содержимое регистра 37 в регистр 39 сдвига. По сигналам, формируемым блоком 33 управления, информация из регистра 39 поступает на выход- устройства.

Таким же образом вьщается на выход устройства вся остальная информация о срабатывании канала. Далее описываются устройства, которые выполняют вспомогательные функции, т.-к. обращение к блоку 14 памяти производится от двух блоков 10 и 11 (двух микроэвм), причем эти обращения дешифруются на элементах И 12 и 19, поэтому введен второй блок 16 сравнения приоритетов, который распределяет по времени обращения к общему блоку 14 памяти от двух блоков (микро- ЭВМ) и управляет-вторым формирователем 15 адреса. В этом блоке поочередно открываются шинные формирователи 32,33 или 34,35 (фиг.-5), подключая к магистрали адреса (МА) и управления (I-iy) блока 14 памяти магистрали адреса и управления одного из двух блоков (микроэвм). Для реализации двухсторонней связи между блоками

0

5

0

5

0

5

0

5

0

5

10и 11 (микроэвм) применены два параллельных интерфейса 17 и 18 типа 580 ВВ55, С помощью регистров А этих интерфейсов осуществляется двухсторонний обмен информацией между блоками 10 и 11. С этой целью в соответствии с программой работы ЭВМ 10

и 11 в регистры А интерфейсов 17 и 8 записывается программа режима II, обеспечивающая двухсторонний синхронный обмен между регистрами А параллельно программируемых интерфейсов.

Регистры В интерфейсов предназначены для формирования векторов прерывания и в соответствие с программой каждой микроэвм 10 и 11 в них записывается программа режима I - односторонняя синхронная запись в регистр 13.

Работу параллельно-программируемых интерфейсов 17 и 18 рассмотрим применительно к решению задачи передачи адреса записи блока 14 памяти, который занесен в блоки 10 и 11.Этот адрес записи находится в регистре Д1 блока 10 (первой микроЭВМ), который является дополнительным сегментом (ES).,

Данный адрес записи необходимо передать блоку 11 (второй микроэвм), чтобы при чтении информации из второго блока 14 памяти адрес чтения не превысил адреса записи. Блок 11 (вторая микроэвм), обращаясь через И 20 к внвшнеьгу устройству интерфейса 18, вписывает в его регистр вектор прерывания для блока 10 (первой микроЭВМ). Блок 10 (первая микроЭВМ) по этому вектору, который поступает на вход VEC к запросу прерывания (вход 1И1), прерывает выполнение своей основной программы поиска сработавшего канала и переходит на программу прерывания. По программе прерывания первый микропроцессор 5аписывает содержимое регистра Д1 во внешнее устройство, которым является регистр А интерфейса 17. 1 .

Так как оба регистра А запрограммированы в режиме II работы, то информация иэ регистра А интерфейса 17 переписывается в регистр А интерфейса 18. Затем блок 10 (первой микроЭВМ) записывает в регистр В интерфейса 17 вектор прерывания для блока

11(второй микроэвм), по этому запросу на прерывание блок 11 (второй микроэвм) прекращает выполнить свою

основную программу и переходит на выполнение программы прерывания. По этой программе блок 11 (вторая микро ЭВМ) опрашивает регистр А интерфейса 18 и записывает его содержимое в микропроцессор второй микроэвм.

Многоканальное устройство для сбора информации позволяет обнаружить срабатывание любого канала,апрок- симировать это срабатывание, т.е. очищать от дребезга, точно привязывать ко времени, когда это срабатывание произошло, и формировать выходной последовательный кадр, содержащий информацию о каждом срабатывании в любом канале.

Формула изобретения

Многоканальное устройство для сбора информации, содержащее генератор импульсов, первый элемент И,выход которого подключен к первому входу первого блока сравнения приоритетов, первый блок памяти, счетчик, первый вход которого является управляющим входом устройства, второй, третий и четвертый элементы И, о т - ли чающееся тем, что, с целью повышения достоверности принимаемой информации, в него введены мультиплексор, первый и второй формирователи адреса, второй блок сравнения приоритетов, первый и второй блоки управления передачей, первый и второй блок обработки информации, второй блок памяти, пятый и шестой элементы И, первый и второй параллельные интерфейсы, информационные входы мультиплексора являются информационными входами устройства,выход мультиплексора подключен к информационному входу первого блока памяти, выходы которого объединены с соответствующими выходами первого блока управления передачей и подключены к соответствукнцим информационным входам второго блока памяти, первого параллельного интерфейса и к соответствующим информационным входам- выходам первого блока обработки информации и первого параллельного интерфейса, выход генератора импуль- сов подключен к вторым входам счетчика и первого блока сравнения приоритетов, первый и второй выходы последнего подключены соответственно к первому и второму управляющим входам первого формирователя адреса, информационные выходы последнего подключены к соответствующим адресным

входам первого блока памяти,первый, второй и третий управляющие входы которого подключены к одноименным управляющим выходам первого формирователя адреса, выходы счетчика подключены к соответствующим адресным входам мультиплексора, первым адресным входам первого формирователя адреса и к информационным входам первого блока управления передачей,адресные входы-выходы первого блока обработки информации подключены к соответствующим адресным входам второго формирователя адреса и к соответствующим первым входам первого четвертого элементов И, вторые вхо- дь1е которых подключены к соответствующим управляющим выходам первого блока обработки информации, выход второго элемента И подключен к управляющему входу первого блока управления передачей, выход третьего элемента И подключен к первому входу второго блока сравнения приоритетов, первый и второй выходы которого подключены к одноименным управляющим входам второго формирователя адреса, третий управляющий вход которого подключен к соответствующему управляющему выходу первого блока обработки

информации, выход четвертого элемента И подключен к управляющему входу первого параллельного интерфейса,выходы второго блока памяти подключены к соответствующим информационным

входам-выходам второго блока обработки информации, первым информационным входам-выходам и входам второго параллельного интерфейса, информационным входам второго блока управления передачей, выход которого является информационным выходом устройства, адресные входы-выходы второго блока обработки информации подключены к соответствующим вторым адресным

входам второго формирователя адреса, адресным входам второго блока управления передачей, первым входам Пятого и шестого элементов И, вторые входы которых, четвертый управляющий

вход второго формирователя адреса и управляющий вход второго блока управления передачей подключены к соответствующим управляющим выходам второго блока обработки информации,выход

пятого элемента И подключен к вторсг му входу второго блока сравнения приоритетов, выход шестого элемента И подключен к управляющему входу второго параллельного интерфейса,третьи выходы первого и второго блока сравнения приоритетов подключены к разрешающему входу первого блока обработки информации, управляющий вход запроса режима работы и задающие входы режима работы которого подключены соответственно к первому информационному выходу и к соответствующим вторым информационным выходам второго параллельного интерфейса, вторые информационные входы-выходы которого подключены к соответствующим вторым информацирннь1м входам-выходам первого

блока параллельного интерфейса,первый 2о работки информации.

информационный выход и вторые информационные выходы которого подключены соответственно к управляющему входу запроса режима работы и соответствующим задающим входам режима работы второго блока обработки информации, информационные выходы второго формирователя адреса подключены к соответствующим адресным входам второго блока памяти, управляющие входы которого подключены к соответствующим 5трав- ляющим выходам второго формирователя адреса, установочные входы первого и второго блоков обработки информации объединены с первым входом счетчика, четвертый выход второго блока сравнения приоритетов подключен к разрешающему входу второго блока обФиг. 2

Фиг л

Фив.З

Фиг. 5

НУ

fU

MS

J

J5

J5

57

39

Sbfxod

Фиг. 6

Запись первого Запись то/юго сра чтыВания Cfitaoa-m i а2.нала...на.лаСтруцгтпура. uHcfiof na uu В na.f j rrtui.

| Многоканальное устройство для сбора информации | 1983 |

|

SU1117677A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-11-07—Публикация

1988-02-25—Подача